Production method of heavily phosphorus-doped thin substrate silicon epitaxial layer for Schottky devices

A silicon epitaxial layer, epitaxial layer technology, applied in chemical instruments and methods, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problem of different flow field distribution, increase the difficulty of thickness uniformity control, and increase the difficulty of epitaxial defect control and other issues to achieve good uniformity, improve performance and yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

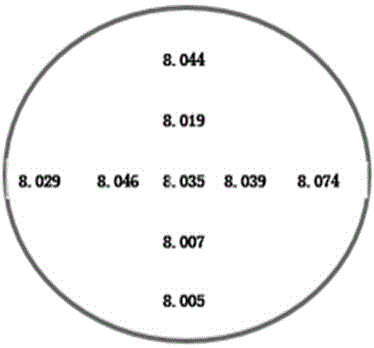

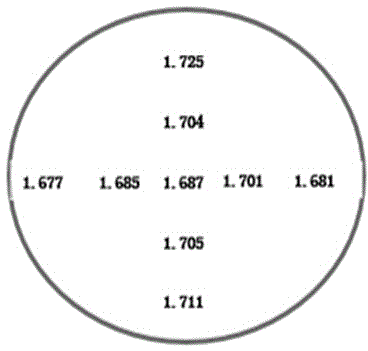

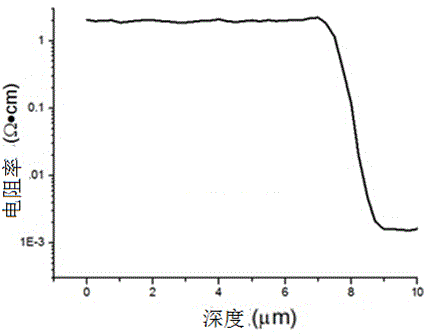

Examples

Embodiment 1

[0021] (1) Use hydrogen chloride with a purity ≥ 99.99% to polish the base of the epitaxial furnace at high temperature to completely remove the residual deposits on the base. The eclipse time was set to 5 min. Then wrap a layer of undoped polysilicon on the graphite base, the growth material is trichlorosilane gas with a purity ≥ 99.95%, the flow rate is set to 5 g / min, and the growth time is set to 5 min.

[0022] (2) Load a phosphorus-doped silicon substrate sheet with a thickness of 290±10 μm into the pit of the base of the epitaxial furnace, and then use nitrogen and hydrogen with a purity of ≥99.999% to purge the epitaxial furnace cavity for 8 minutes, and set the gas flow rate to 150 L / min.

[0023] (3) Use hydrogen chloride gas to perform in-situ polishing on the surface of the silicon substrate to remove the micro-damage layer and improve the surface lattice quality. Use hydrogen gas to transport hydrogen chloride gas into the reaction chamber. The hydrogen flow rat...

Embodiment 2

[0031] (1) Use hydrogen chloride with a purity ≥ 99.99% to polish the base of the epitaxial furnace at high temperature to completely remove the residual deposits on the base. The eclipse time was set to 5 min. Then wrap a layer of undoped polysilicon on the graphite base, the growth material is trichlorosilane gas with a purity ≥ 99.95%, the flow rate is set to 4 g / min, and the growth time is set to 4 min.

[0032] (2) Load a phosphorus-doped silicon substrate sheet with a thickness of 290±10 μm into the pit of the base of the epitaxial furnace, and use nitrogen and hydrogen with a purity of ≥99.999% to purge the epitaxial furnace cavity for 8 minutes in sequence, and set the gas flow rate to 150 L / min.

[0033] (3) Use hydrogen chloride gas to perform in-situ polishing on the surface of the silicon substrate to remove the micro-damage layer and improve the quality of the surface lattice. Use hydrogen gas to transport hydrogen chloride into the reaction chamber. The hydroge...

Embodiment 3

[0041] (1) Use hydrogen chloride with a purity ≥ 99.99% to polish the base of the epitaxial furnace at high temperature to completely remove the residual deposits on the base. The eclipse time was set to 5 min. Then wrap a layer of undoped polysilicon on the graphite base, the growth material is trichlorosilane gas with a purity ≥ 99.95%, the flow rate is set to 6 g / min, and the growth time is set to 6 min. In the subsequent mass transfer effect, the polysilicon on the base can encapsulate the back and side surfaces of the phosphorus substrate, suppressing the volatilization of substrate impurities.

[0042] (2) Load a phosphorus-doped silicon substrate sheet with a thickness of 290±10 μm into the pit of the base of the epitaxial furnace, and use nitrogen and hydrogen with a purity of ≥99.999% to purge the epitaxial furnace cavity for 10 minutes in sequence, and set the gas flow rate to 150 L / min.

[0043] (3) Use hydrogen chloride gas to perform in-situ polishing on the su...

PUM

| Property | Measurement | Unit |

|---|---|---|

| evenness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More