Extendable method for revising patterned microelectronic conductor layer layouts

a technology of microelectronic conductors and extendable methods, which is applied in the direction of electric digital data processing, instruments, computing, etc., can solve the problems of time-consuming and iterative methods, and achieve the effect of being ready for commercial implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

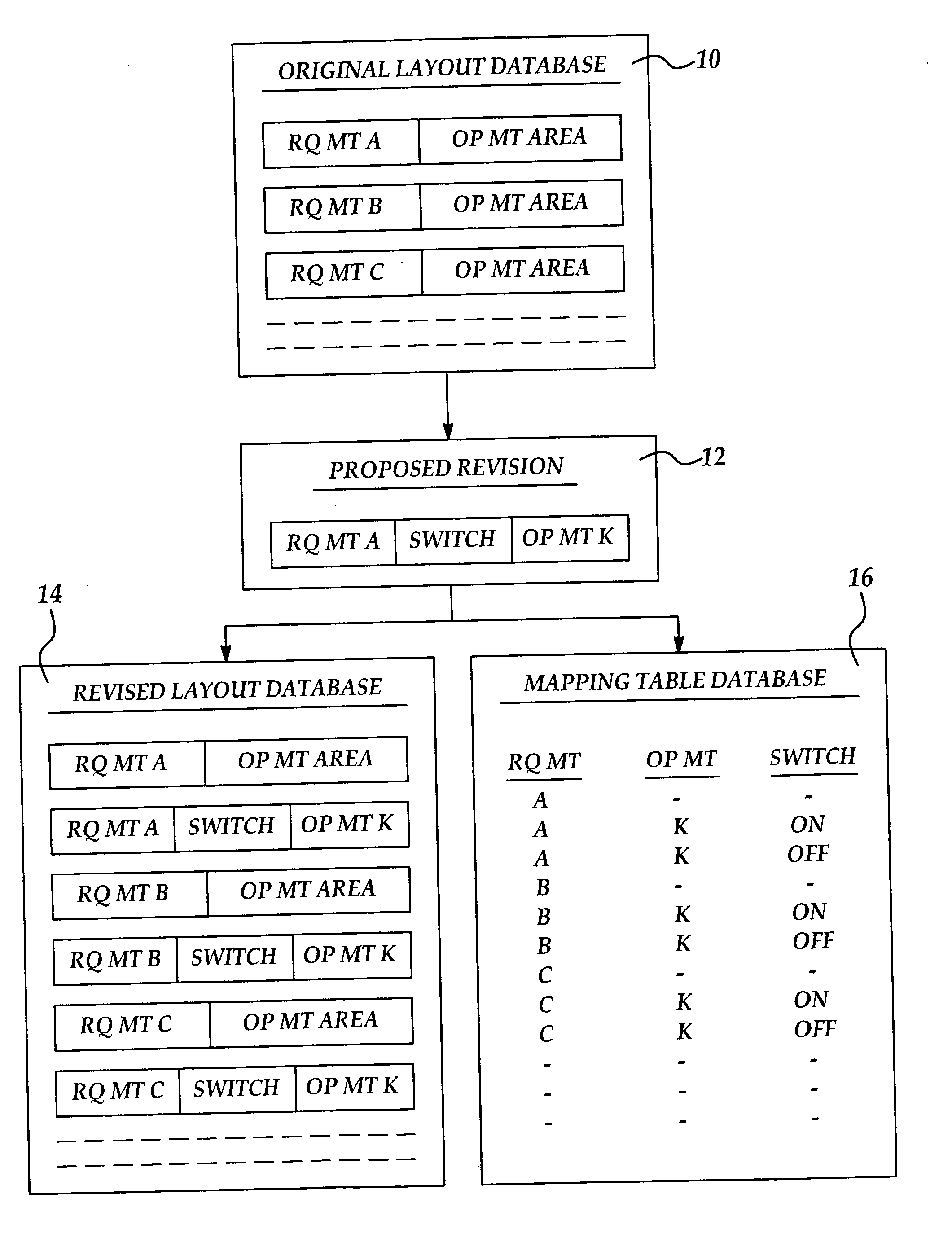

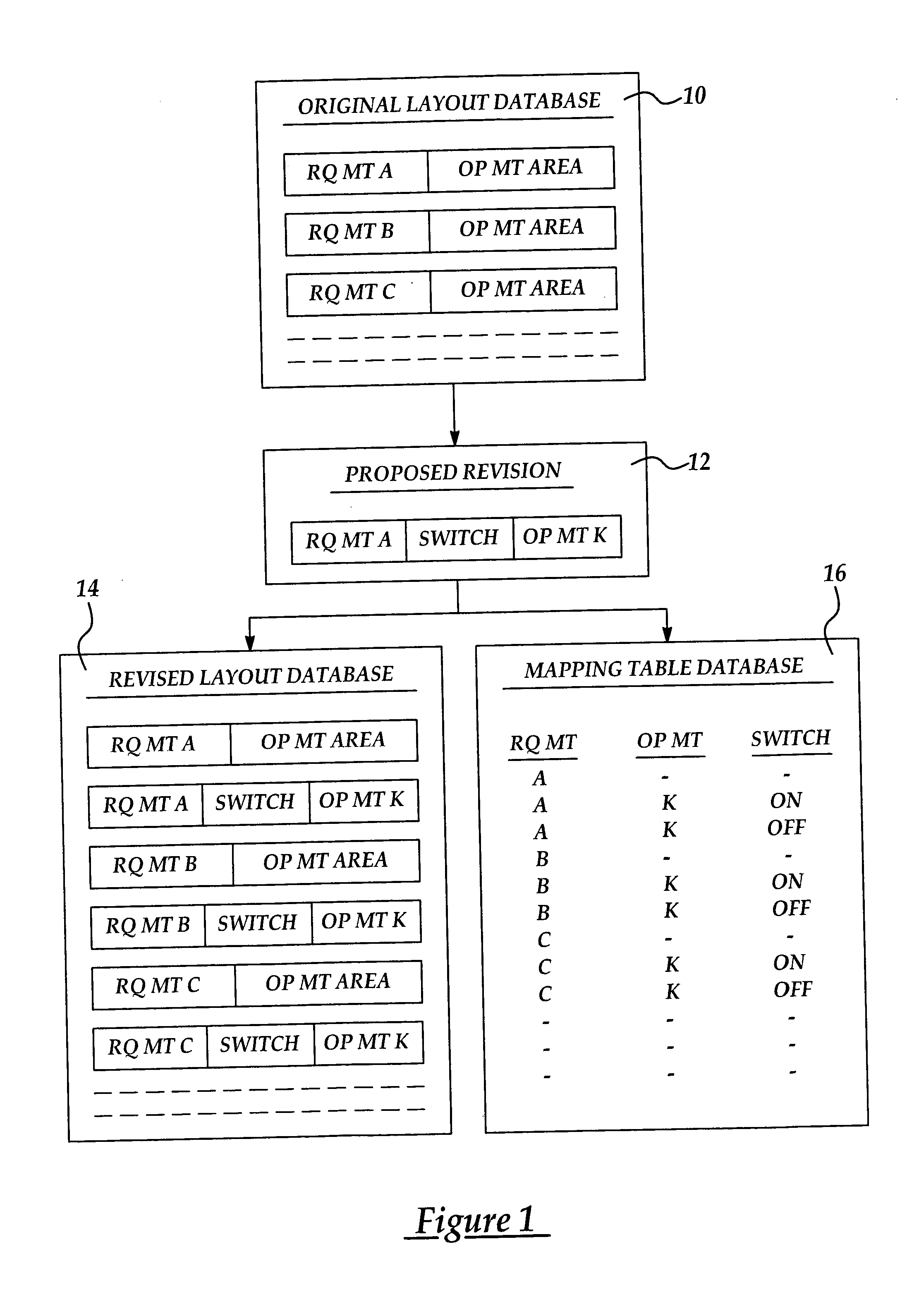

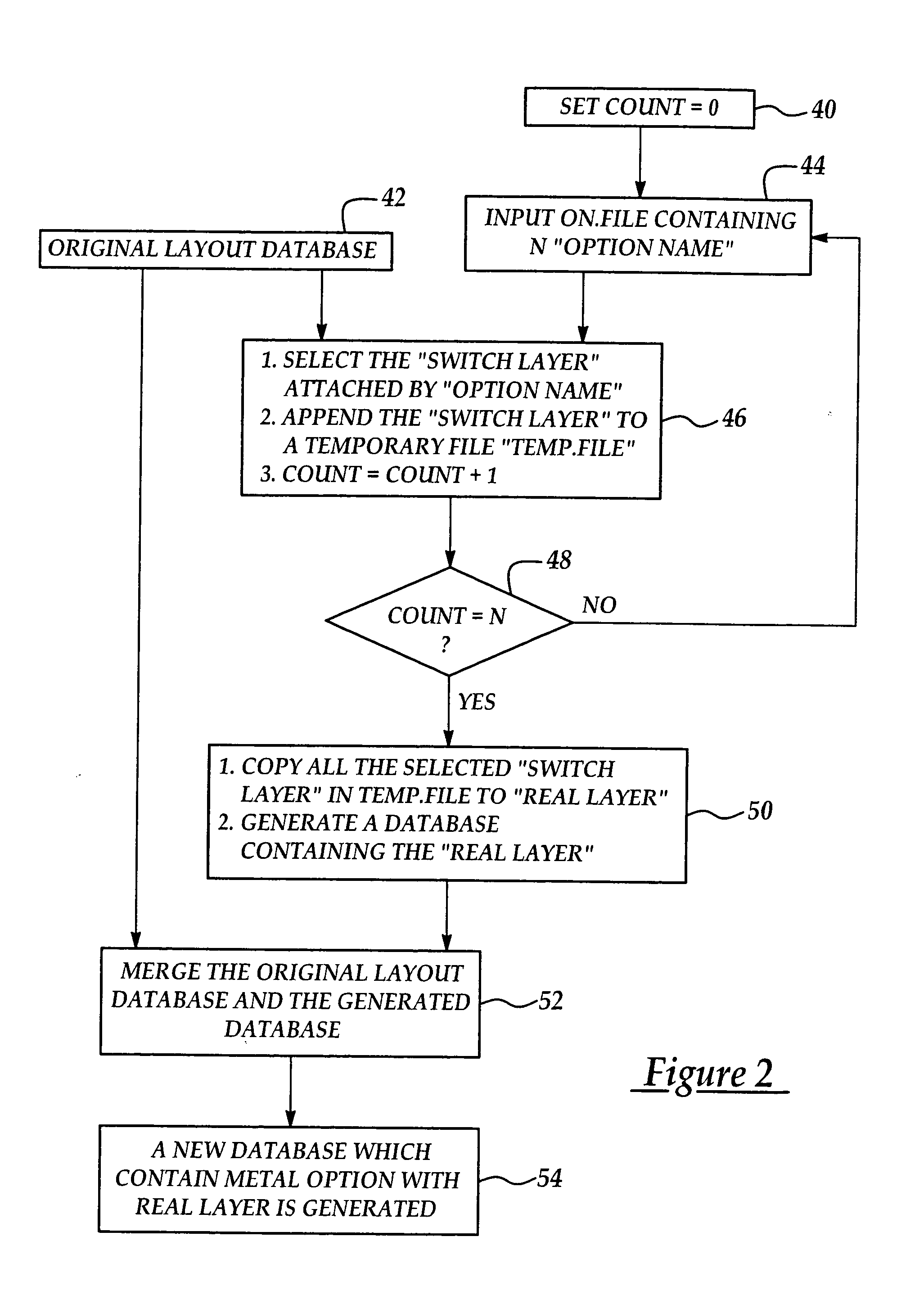

[0029] There is provided by the present invention a method for designing a patterned microelectronic conductor layer layout for use when fabricating a microelectronic fabrication and a system for designing the patterned microelectronic conductor layer layout for use when fabricating the microelectronic fabrication, wherein the patterned microelectronic conductor layer layout is efficiently designed while employing the method for designing the patterned microelectronic conductor layer layout and the system for designing the patterned microelectronic conductor layer layout.

[0030] The present invention realizes the foregoing object by providing within each wiring layout record within a series of wiring layout records within a wiring layout database directed towards a series of microelectronic fabrications an unoccupied equivalent wiring location within which may be formed at least one optional wiring pattern. Thus, when there is designed within an unoccupied equivalent wiring location...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More