Pseudo-synchronization of the transportation of data across asynchronous clock domains

a technology of asynchronous clock domain and data transportation, applied in the field of electronic circuits, can solve the problems of normal control circuit delays, delays in data transfer between blocks, and delays in data transfer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

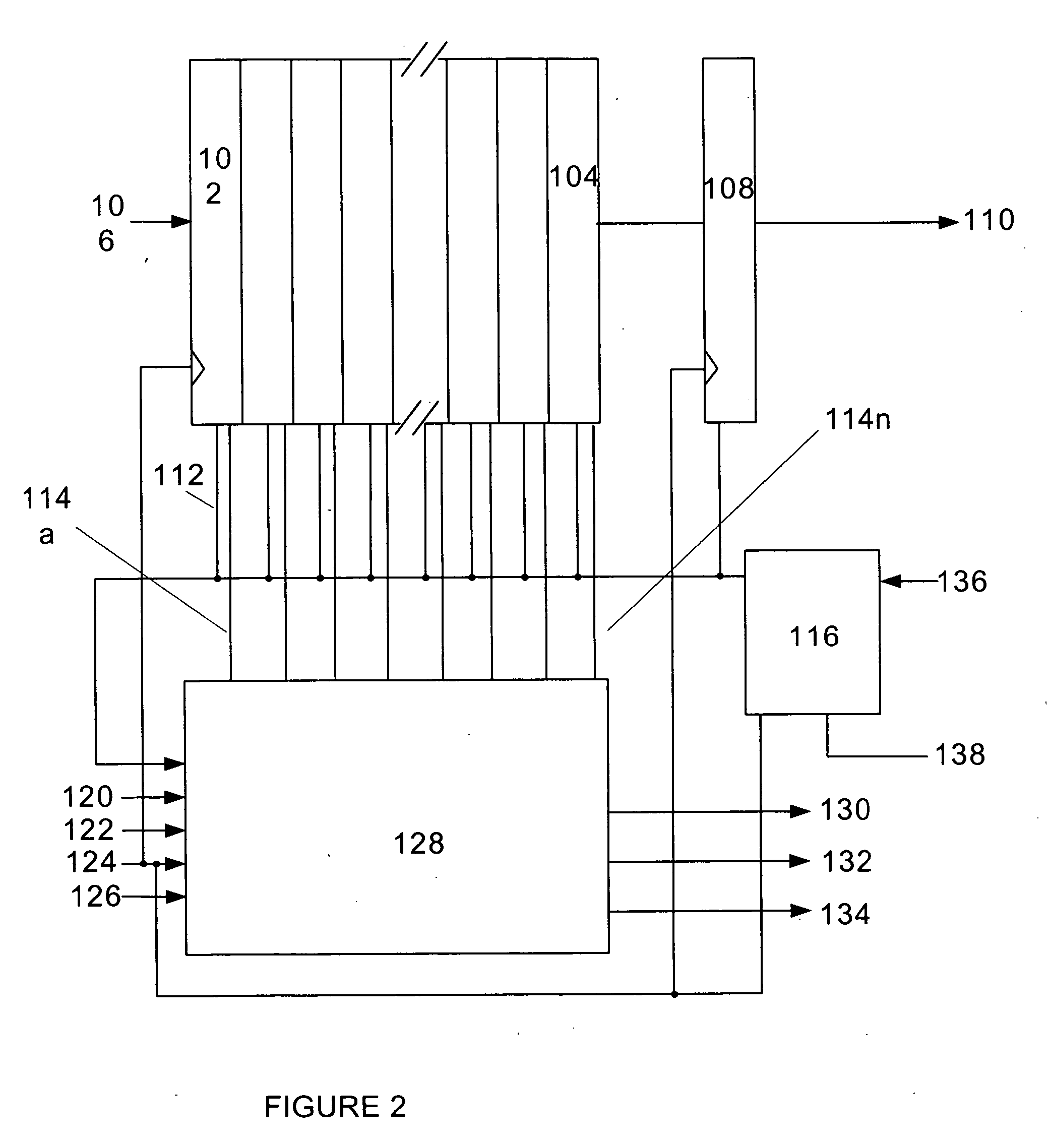

[0017] Disclosed herein are systems and methods for pseudo-synchronous data transfer. To facilitate description of the inventive systems, example systems that can be used to implement the systems and methods for pseudo-synchronous data transfer are discussed with reference to the figures. Although these systems are described in detail, it will be appreciated that these systems are provided for purposes of illustration only and modifications are feasible without departing from the inventive concept.

[0018] Referring now and in more detail to the drawings in which like numerals indicate corresponding parts through the several views, this disclosure describes pseudo-synchronous data transfer. It describes how the system is configured and how it operates.

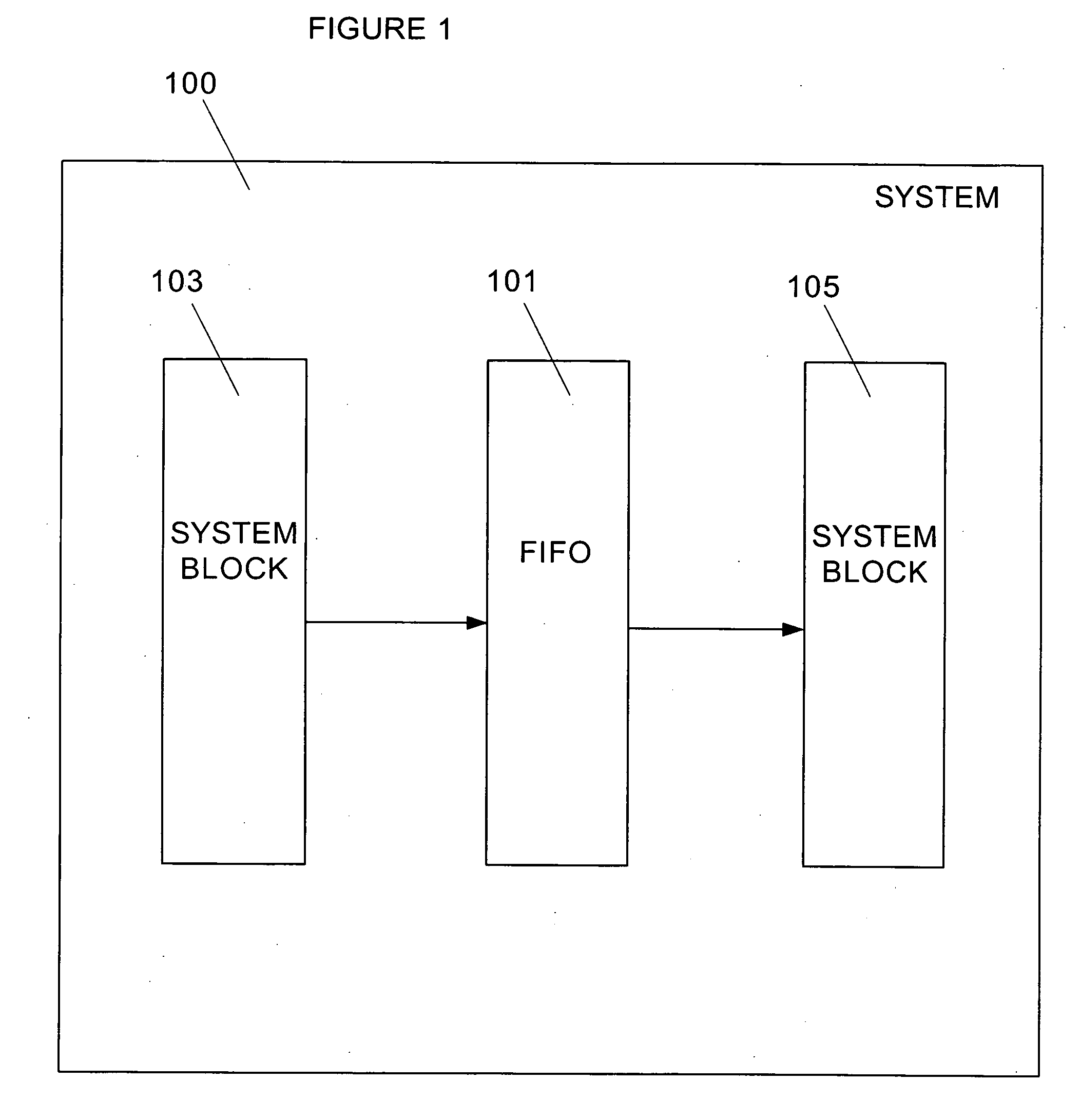

[0019] A system level block diagram 100 is provided in FIG. 1. FIFO 101 is used to transport data between system block 103 and system block 105. System blocks 103, 105 operate at different frequencies. The frequencies of a preferred em...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More