Semiconductor device and method for manufacturing same

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

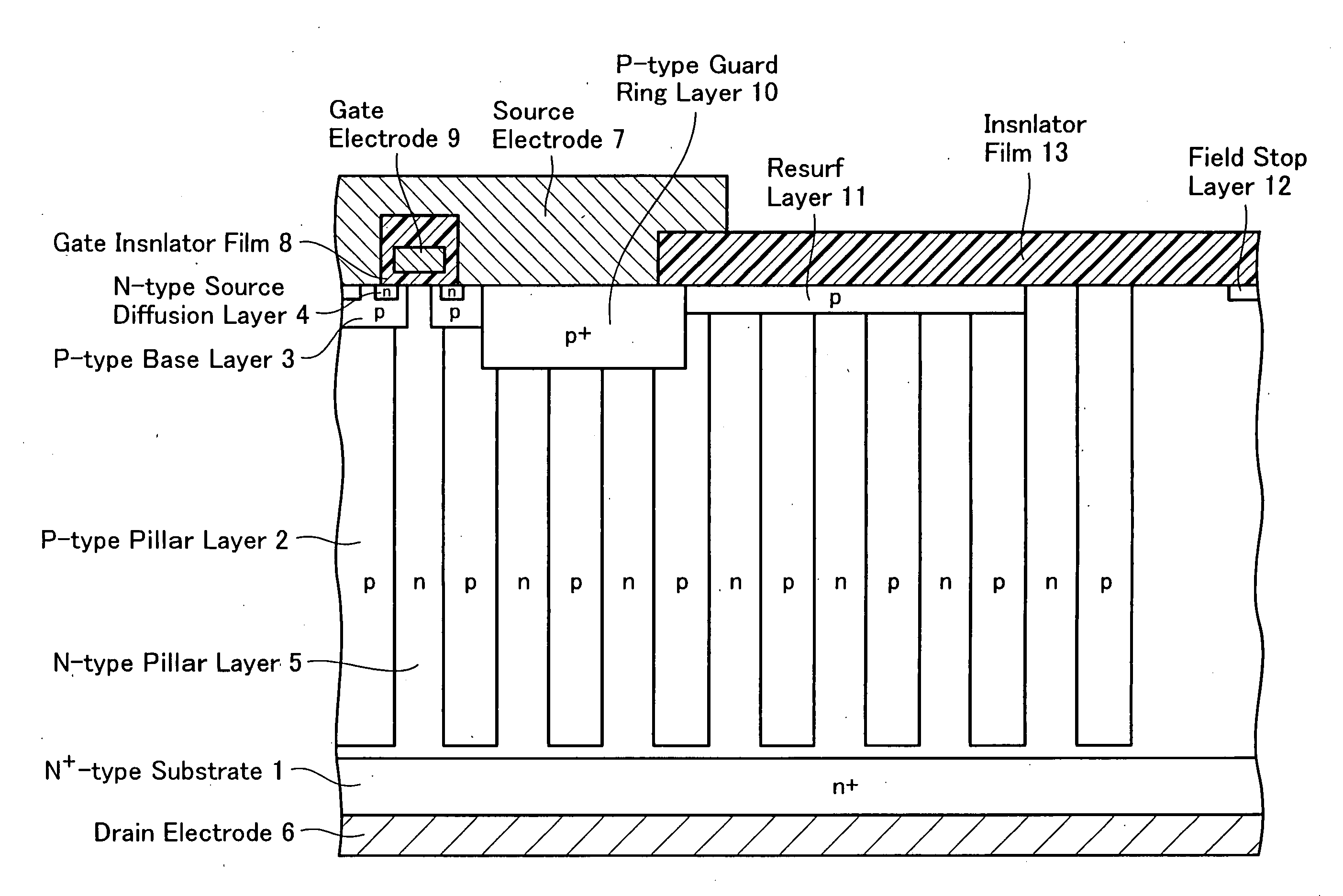

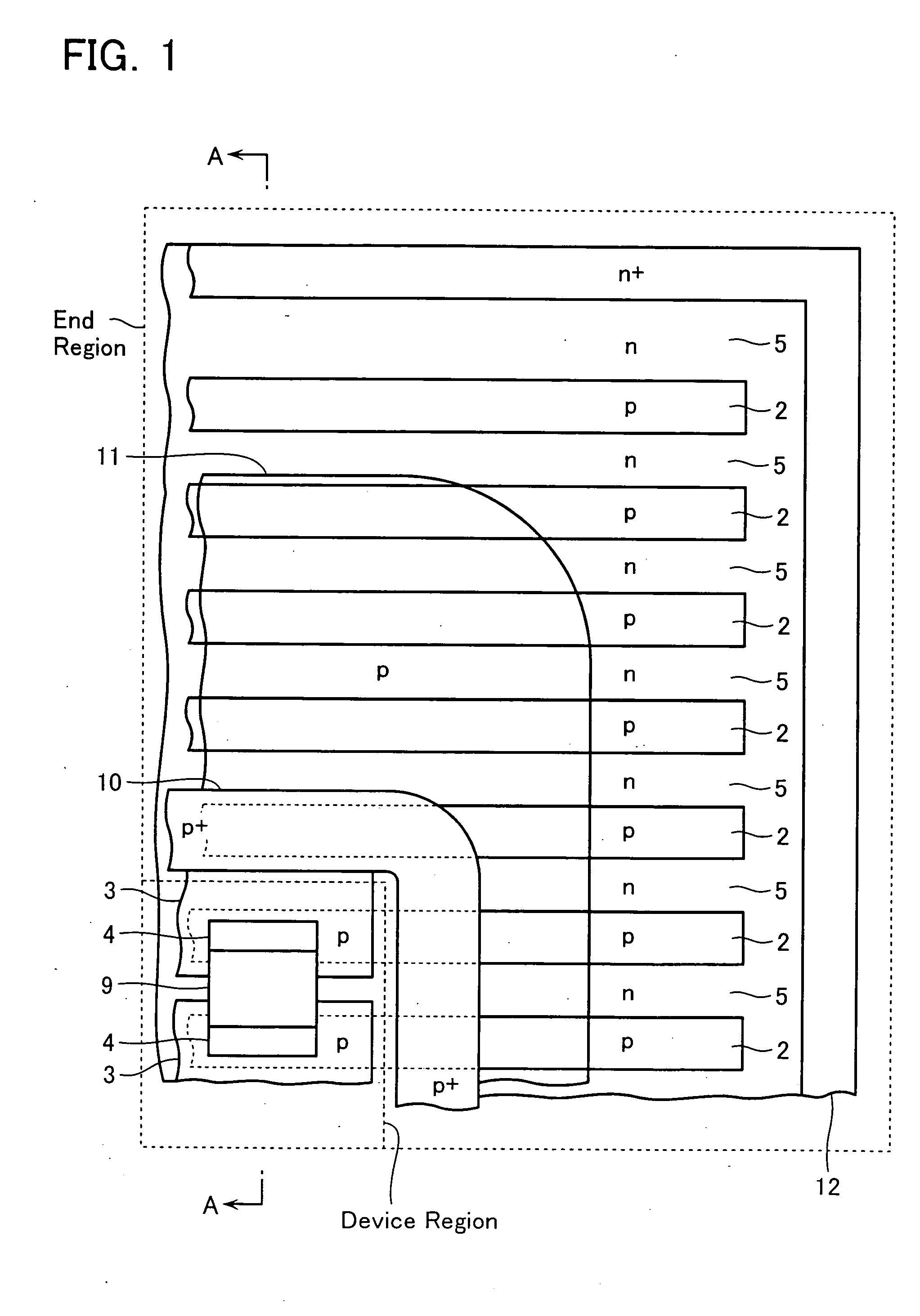

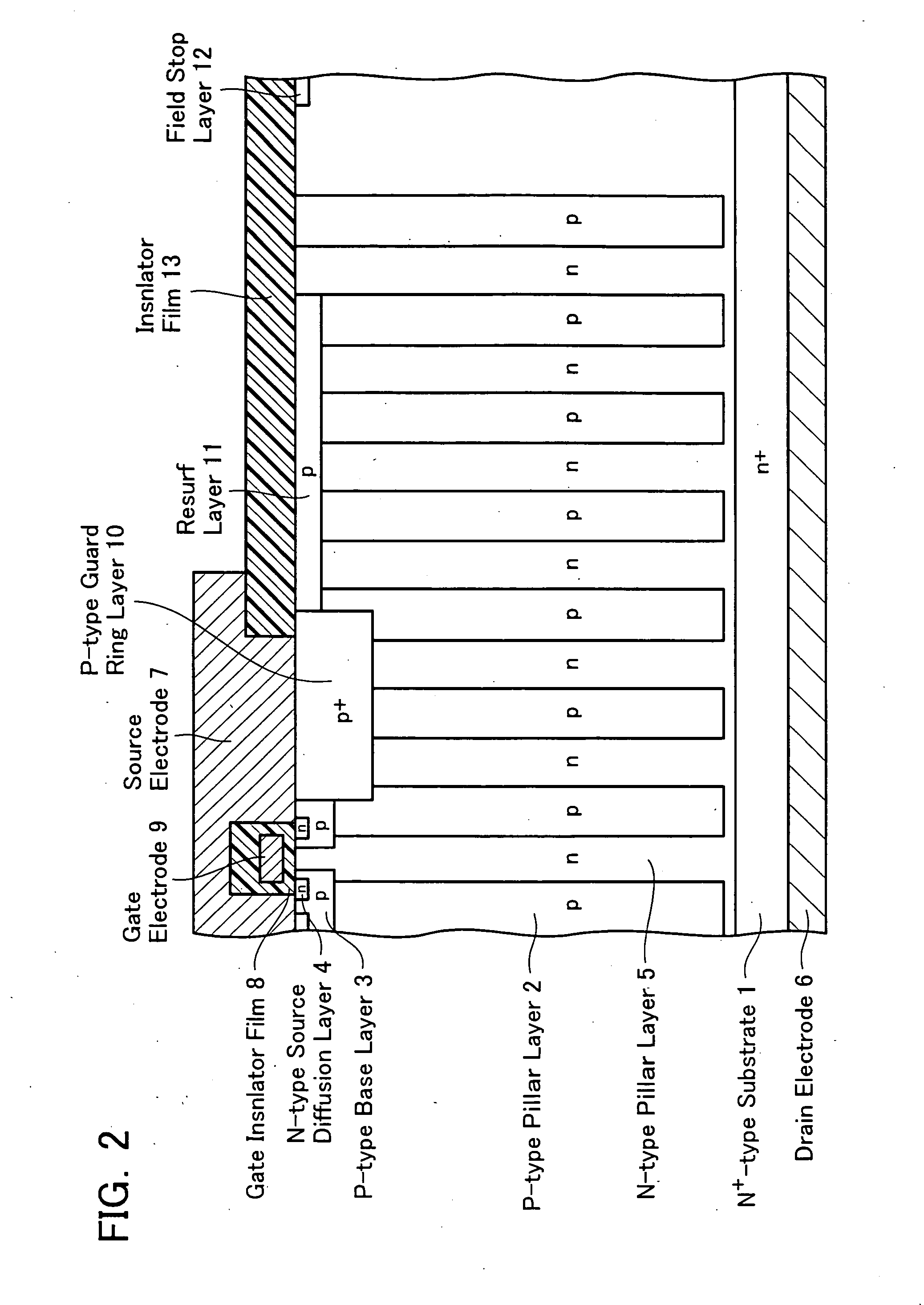

[0027]FIG. 1 is a schematic plan view of the configuration of the power MOSFET according to the first embodiment of the present invention. FIG. 2 is a cross sectional view along the line A-A in FIG. 2. The MOSFET has a super junction structure formed over the n+-type substrate 1 which functions as the drain layer. The super junction structure includes an n-type pillar layer 5 and a p-type pillar layer 2, which have a cross section of a vertically-oriented strip and are formed alternately in the lateral direction (the first direction) along the surface of the n+-type substrate 1. Formed under the n+-substrate 1 is a drain electrode 6 common to a plurality of MOSFETs. Note that although the example in FIG. 2 shows the p-type pillar layer 2 which is not contact with the n+-type substrate 1, the layer 2 can be configured to be in contact with the substrate 1.

[0028] A p-type base layer 3 in a stripe shape is selectively formed on the surface of the p-type pillar layer 2. An n-type sourc...

second embodiment

[0041]FIG. 9 is a schematic cross sectional view of the configuration of the power MOSFET according to the second embodiment of the present invention. The plan view is omitted here because it is substantially the same as FIG. 1 except for the resurf layer 11. In the power MOSFET according to this embodiment, an insulator film 13 resides on the surface of the super junction structure formed in the end region. A field plate electrode 14 resides on the insulator film 13, the field plate electrode 14 being connected to the source electrode 7. Consequently, as in the resurf structure in the first embodiment (FIG. 1), the depletion layer extends immediately laterally in the end region when the MOSFET is non-conducting, thereby helping to increase the breakdown voltage.

third embodiment

[0042]FIG. 10 is a schematic cross sectional view of the configuration of the power MOSFET according to the third embodiment of the present invention. This embodiment differs from the above embodiments in that the super junction structure is not formed in the end region, and alternatively, a high resistance layer 15 is formed, and a p-type guard ring layer 16 is formed on the high resistance layer 15. Also in this embodiment, when the MOSFET is non-conducting, the depletion layer extends laterally along the guard ring layer 16, thereby helping to increase the breakdown voltage.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More