Impedance matching commonly and independently

a technology of impedance matching and common impedance, which is applied in the field of common impedance matching and independent impedance matching, can solve the problems of easy adjustment errors and troublesome operation, and achieve the effect of improving impedance matching with the transmission line and high accuracy impedance matching

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

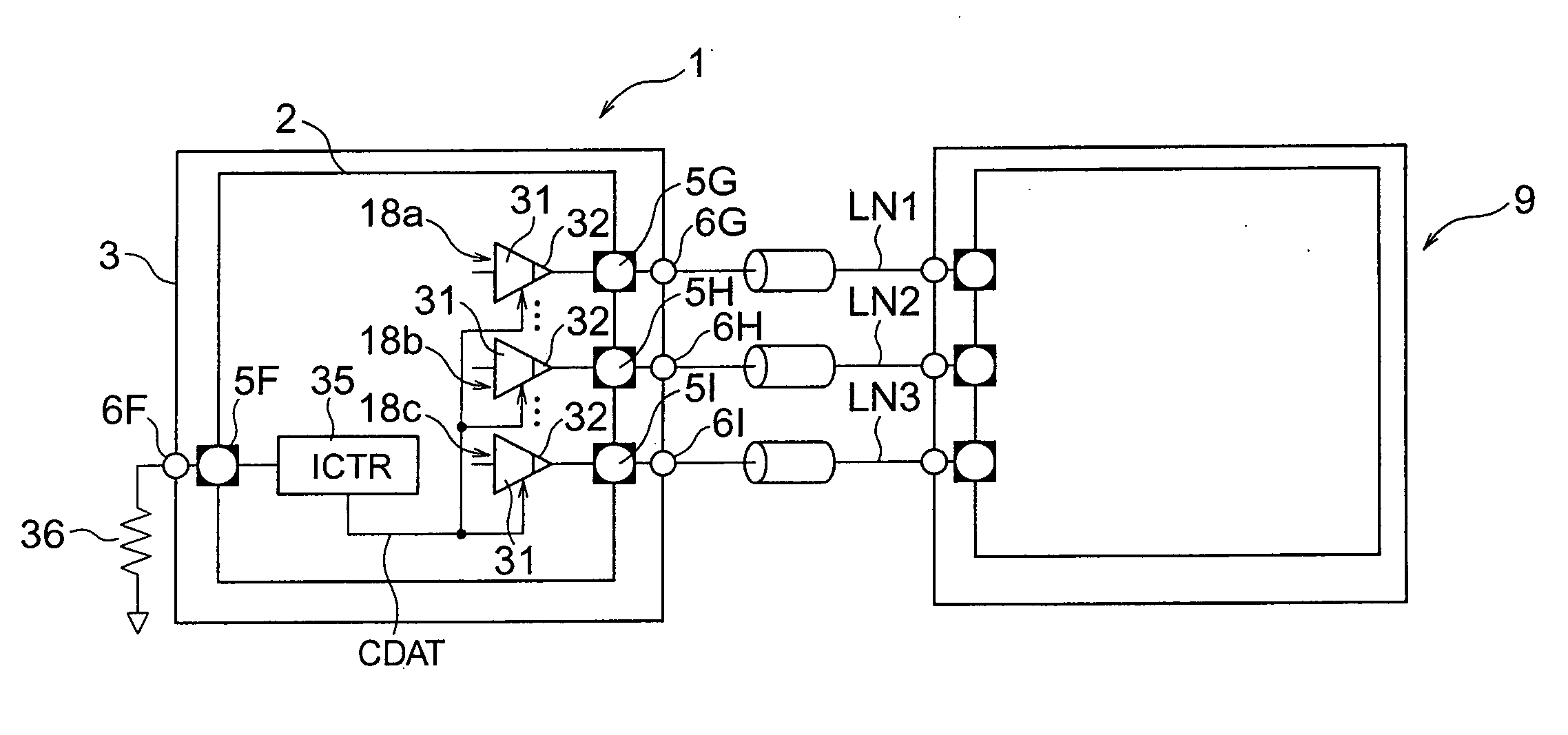

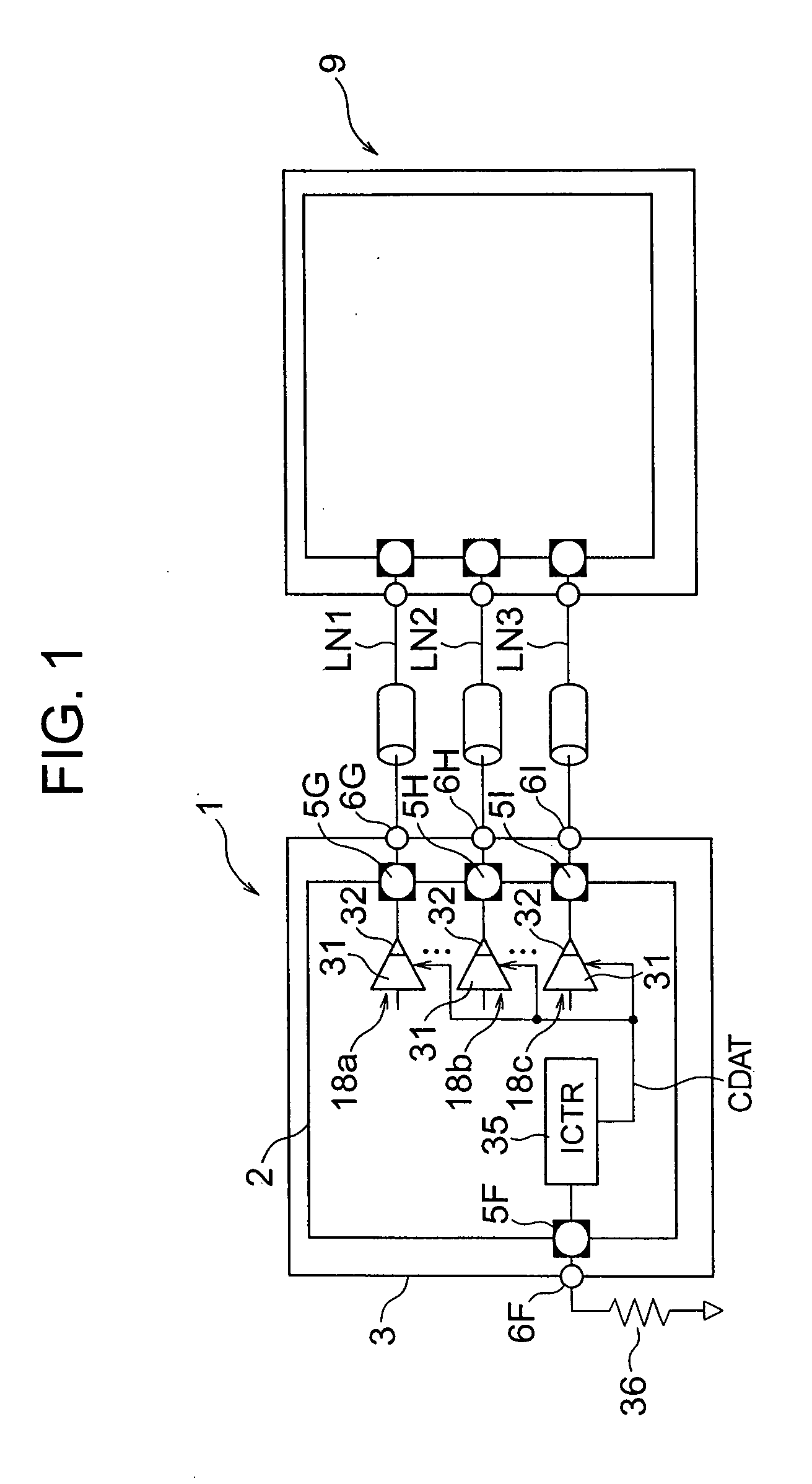

[0036]FIG. 1 mainly shows an impedance matching structure of an SRAM as an example of the semiconductor device according to the invention. The SRAM 1 shown in the Figure is fabricated on one semiconductor substrate such as a single crystal silicon substrate by a CMOS integrated circuit fabrication technology, or the like.

[0037] The SRAM 1 includes an SRAM chip 2 as a semiconductor chip (pellet) and a packaging circuit portion (hereinafter called also “package”) 3 combined with the SRAM 2, though the construction is not restrictive, in particular. The package 3 will be later described in detail but a construction for face-down package is hereby assumed. The SRAM chip 2 has a plurality of pad electrodes 5F, 5G to 5I typically shown as representatives of external terminals. The package 3 has a plurality of external connection terminals (packaging terminals) 6F, 6G to 6I typically shown as representatives of packaging terminals for packaging the SRAM 1 to a packaging substrate (not sho...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More