System and method for accommodating non-gaussian and non-linear sources of variation in statistical static timing analysis

a statistical static timing and non-linear source technology, applied in the field of statistical static timing analysis, can solve the problems of inefficient computational procedure, too conservative and non-optimal designs, and proportional increase in the variation of electrical characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

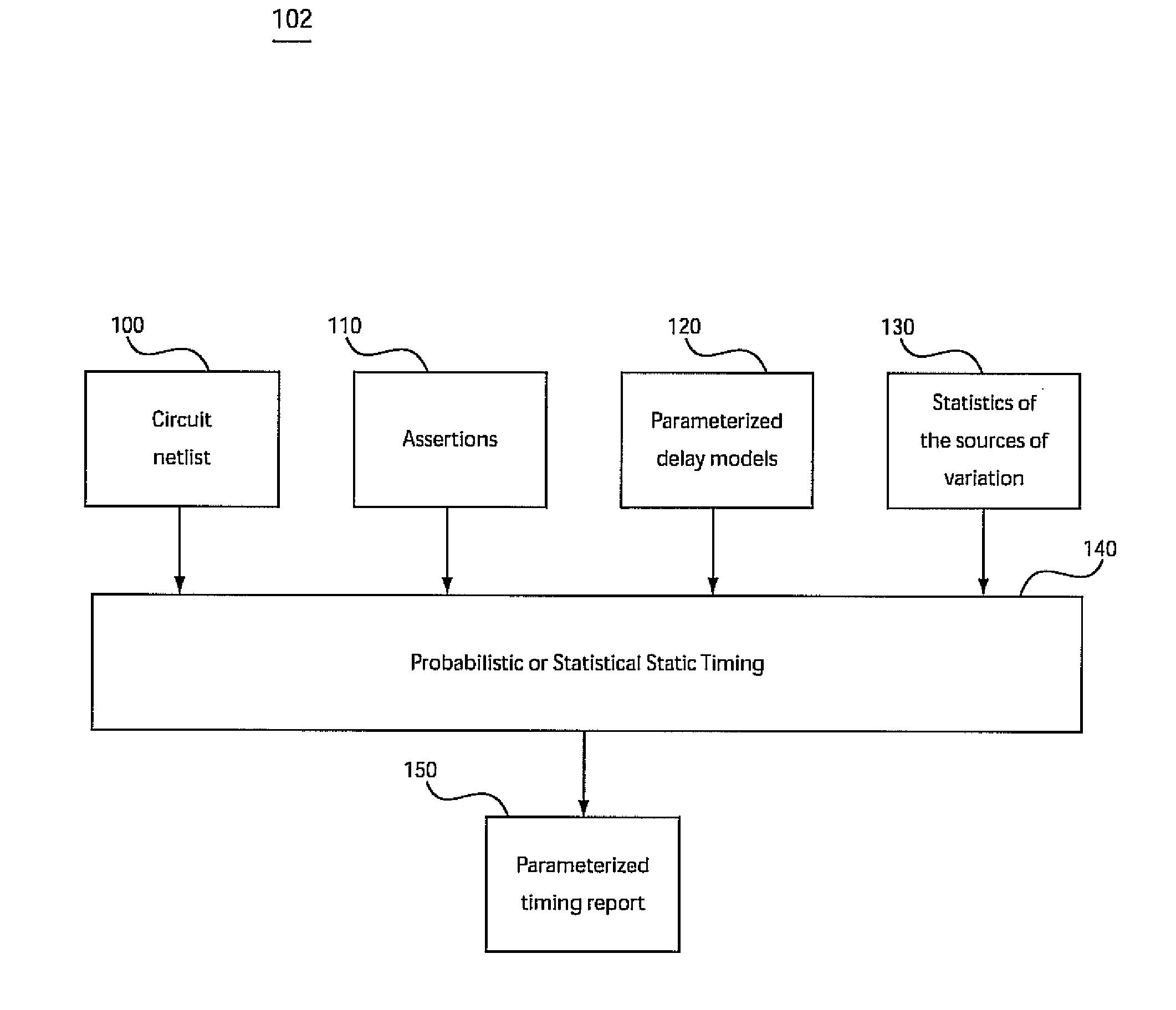

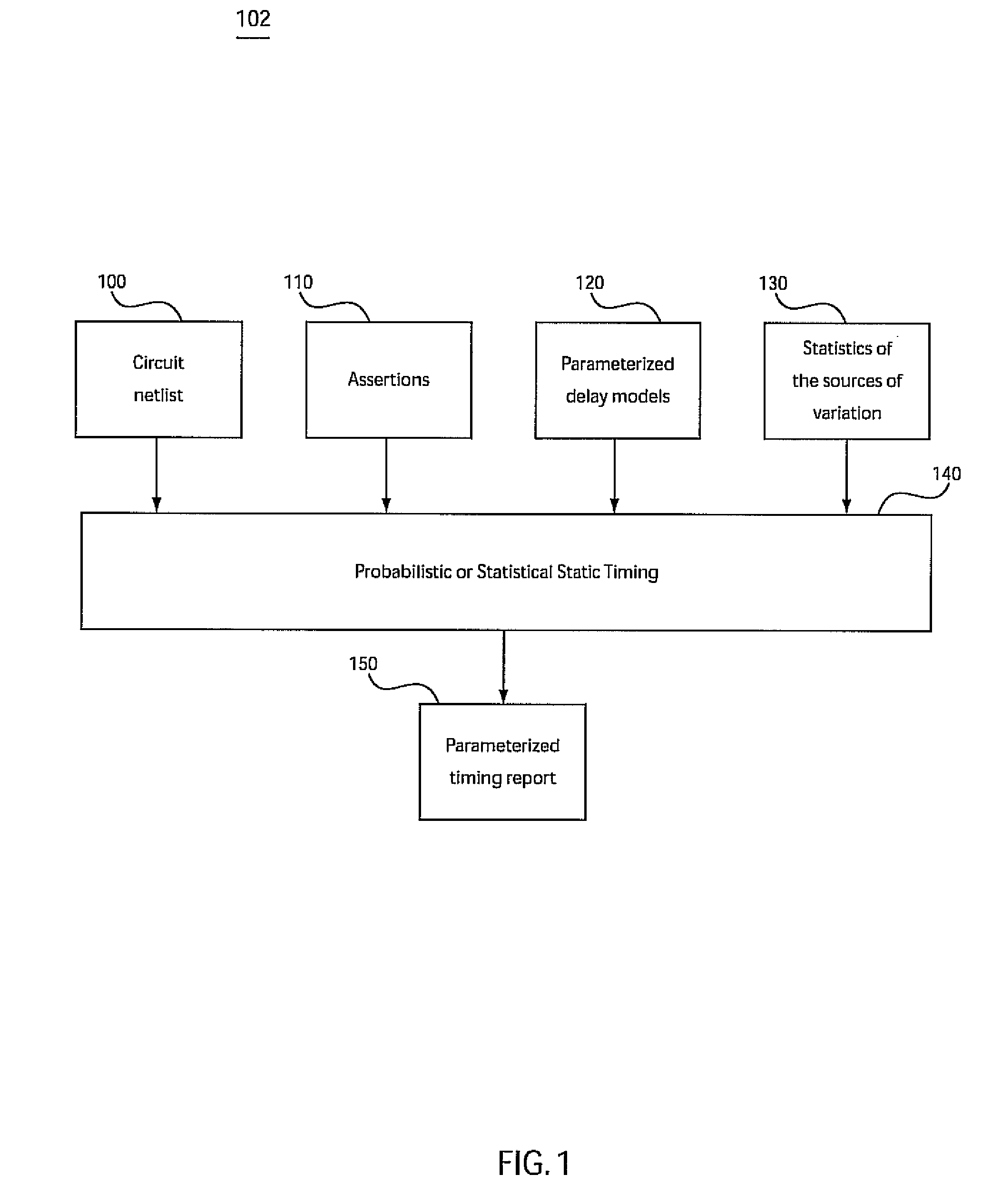

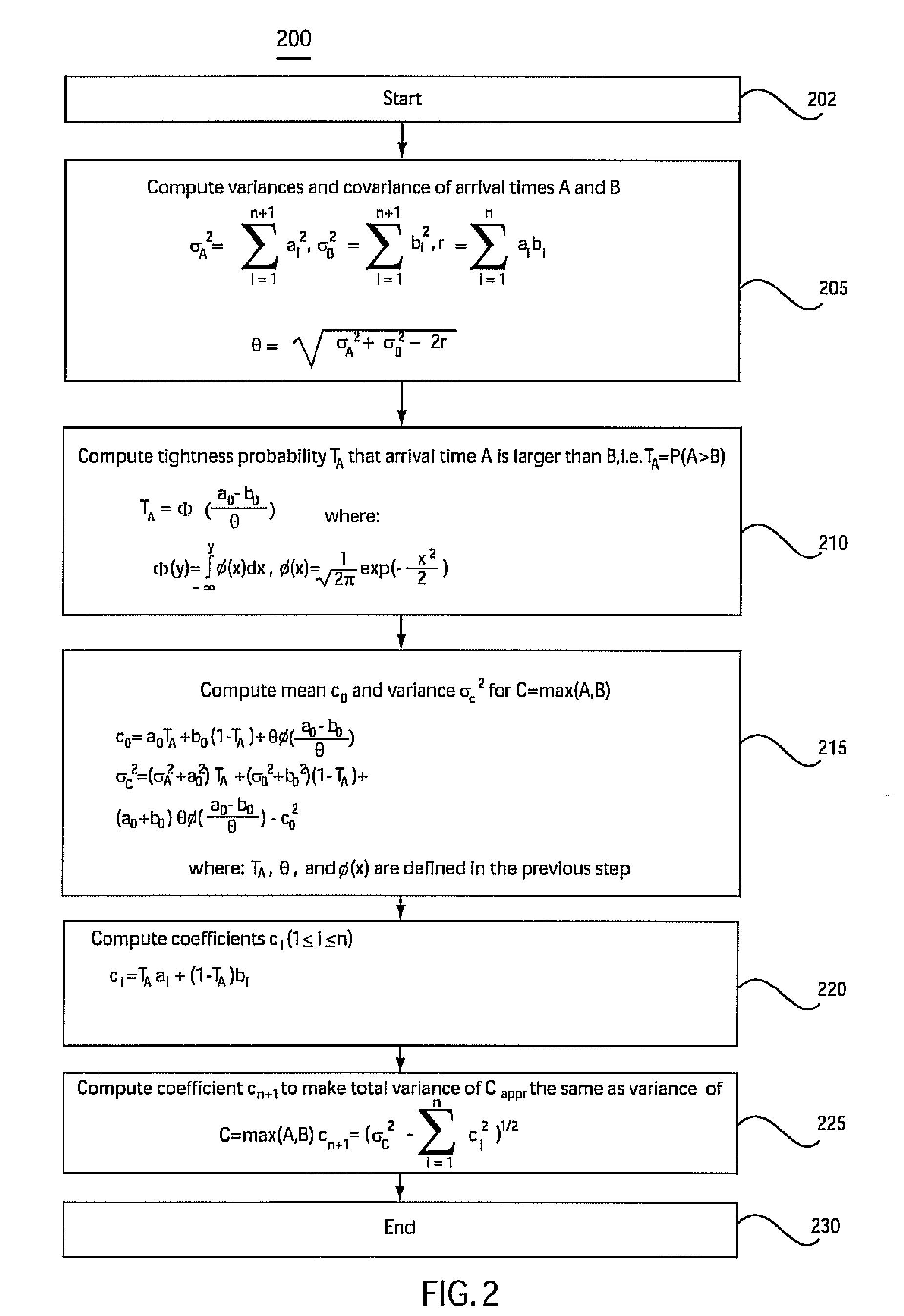

[0032] The present invention is directed to a system and method for accommodating non-Gaussian and nonlinear sources of variation in statistical static timing analysis.

[0033] Digital systems typically work on the basis of the circuit doing some work or computation in each clock cycle or “tick.” In a certain clock cycle, a given signal may not switch, may switch once, or may switch many times, depending on the inputs applied to the circuit. Within each clock cycle, for each and every signal in the system, we are very interested in knowing two things to ensure correct timing: namely the early mode arrival time (or “early arrival time” for short) and the late mode arrival time (or “late arrival time” for short).

[0034] The early mode arrival time is the earliest time at which the signal could possibly switch (i.e., change from the stable logical state at which it was during the previous clock cycle). It is preferred to have the previous cycle “settled down” and recorded correct logic ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More