Apparatus and method for ensuring maximum code motion of accesses to DMA buffers

a buffer and code motion technology, applied in the field of data processing devices, can solve the problems of dma execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution execution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

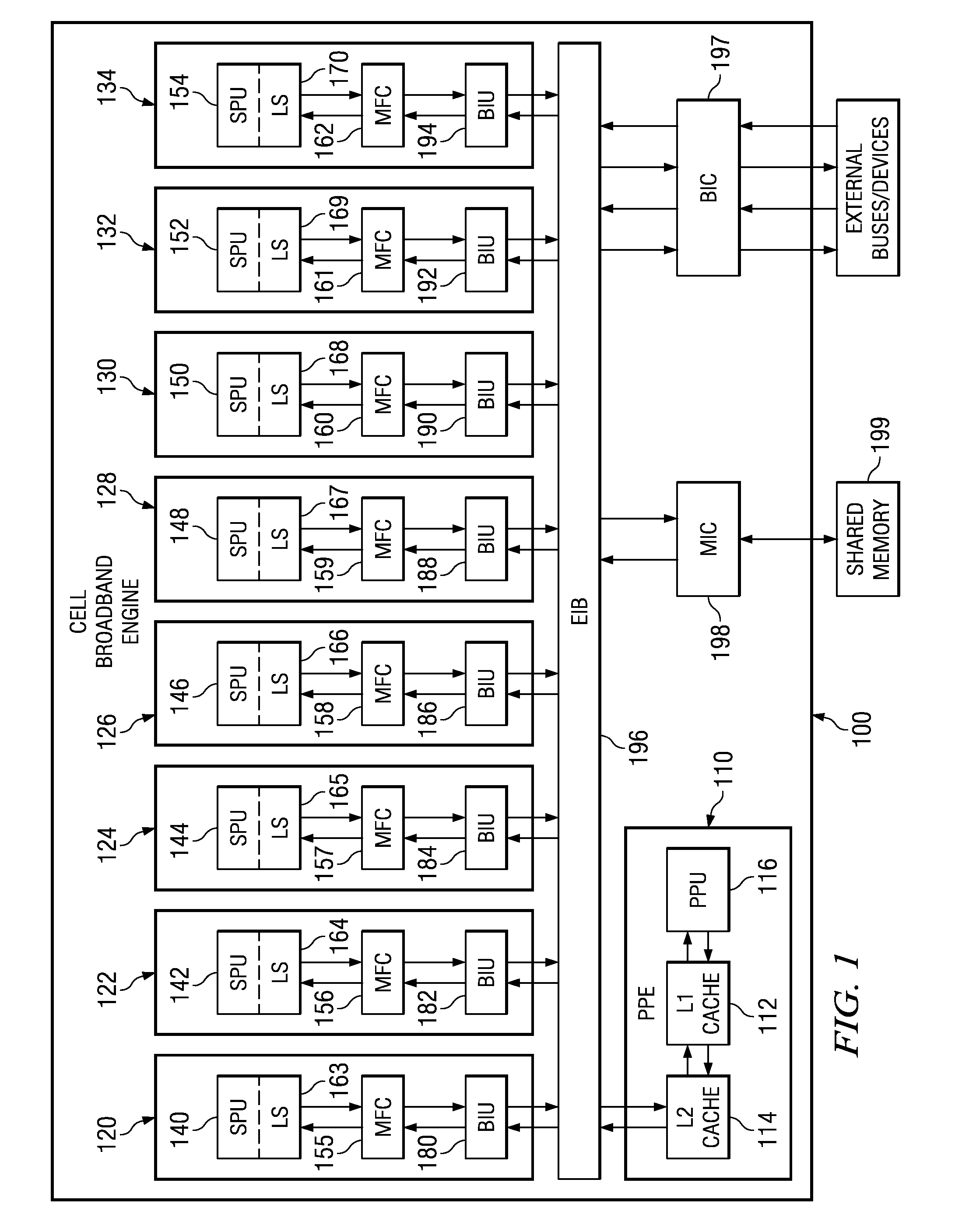

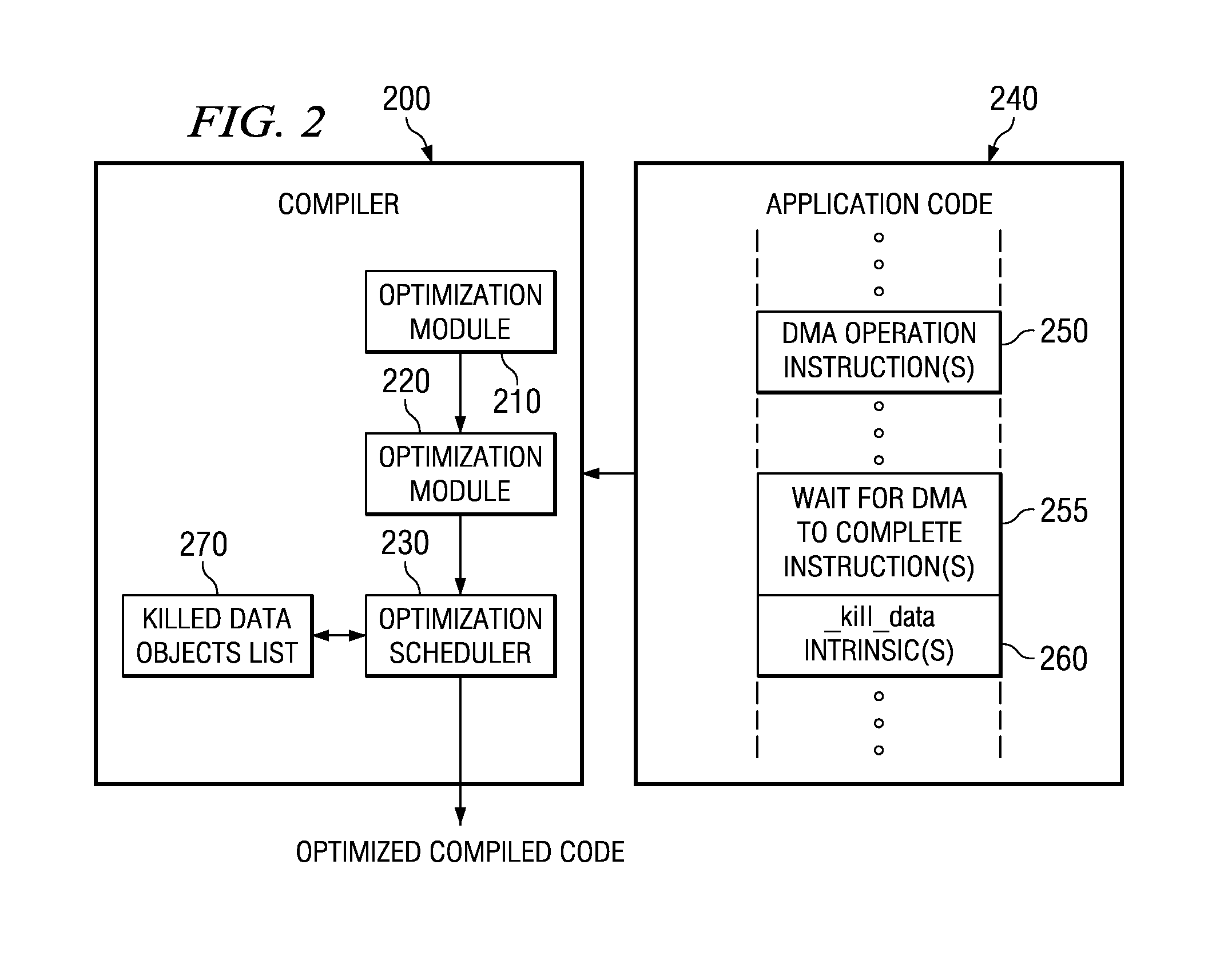

[0029] The following illustrative embodiments provide an apparatus, method and computer program product for ensuring maximum code motion of accesses to Direct Memory Access (DMA) buffers. The illustrative embodiment may be implemented in any processor design or architecture in which DMA buffers are utilized. One such processor design or architecture in which the exemplary aspects of the illustrative embodiments may be implemented is the Cell Broadband Engine (CBE) architecture available from International Business Machines, Inc. The CBE architecture is only exemplary of the possible processor architectures in which the illustrative embodiment may be implemented and the description of such in the following detailed description is not intended to state or imply any limitation with regard to the types of processor architectures in which the illustrative embodiment may be implemented.

[0030]FIG. 1 is an exemplary block diagram of a microprocessor chip in which aspects of the illustrativ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More