Boosting methods for NAND flash memory

a boosting method and flash memory technology, applied in static storage, digital storage, instruments, etc., can solve the problems of low level caused by such a high boosting voltage (boosting voltage disturbance) and achieve the effect of reducing programming voltage, high boosting voltage, and high boosting voltag

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047]FIG. 5 shows a cross section of a portion of a NAND string in a flash memory array undergoing programming according to an embodiment of the present invention. FIG. 5 shows capacitors representing capacitive coupling between some of the elements of the NAND string. Not all couplings between elements are shown. For example, word lines are strongly coupled to directly underlying floating gates allowing floating gates to be programmed. Also, both floating gates and word lines are coupled to a portion of the underlying substrate. The particular couplings shown are chosen to illustrate some of the advantages of this embodiment over prior art programming schemes. Also, the couplings shown are becoming more significant as lateral dimensions of NAND arrays are scaled down in size more rapidly than vertical dimensions are scaled.

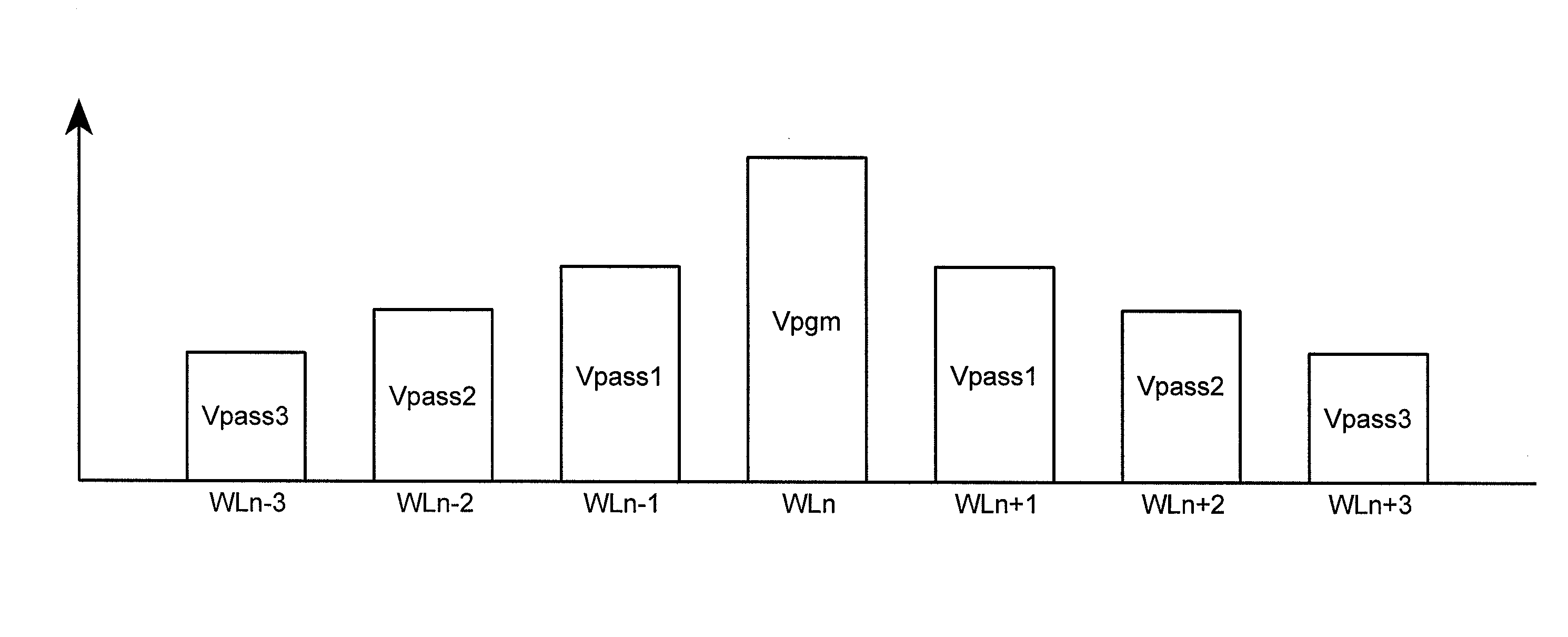

[0048]FIG. 6 shows voltages applied to word lines WLn−3 to WLn+3 of FIG. 5 according to one embodiment of the present invention. WLn is the selected word line ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More