Semiconductor memory device, memory module including the same, and data processing system

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

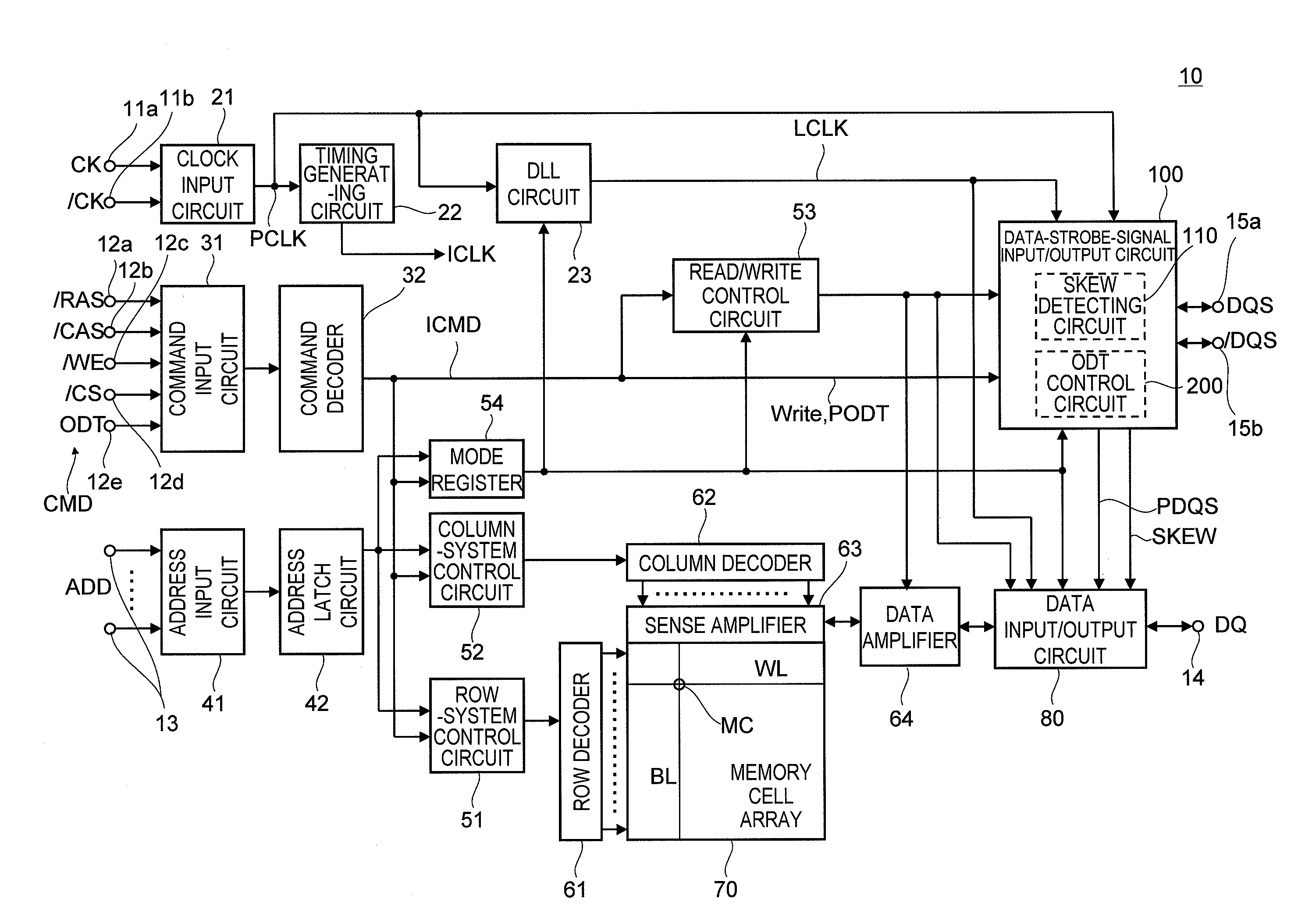

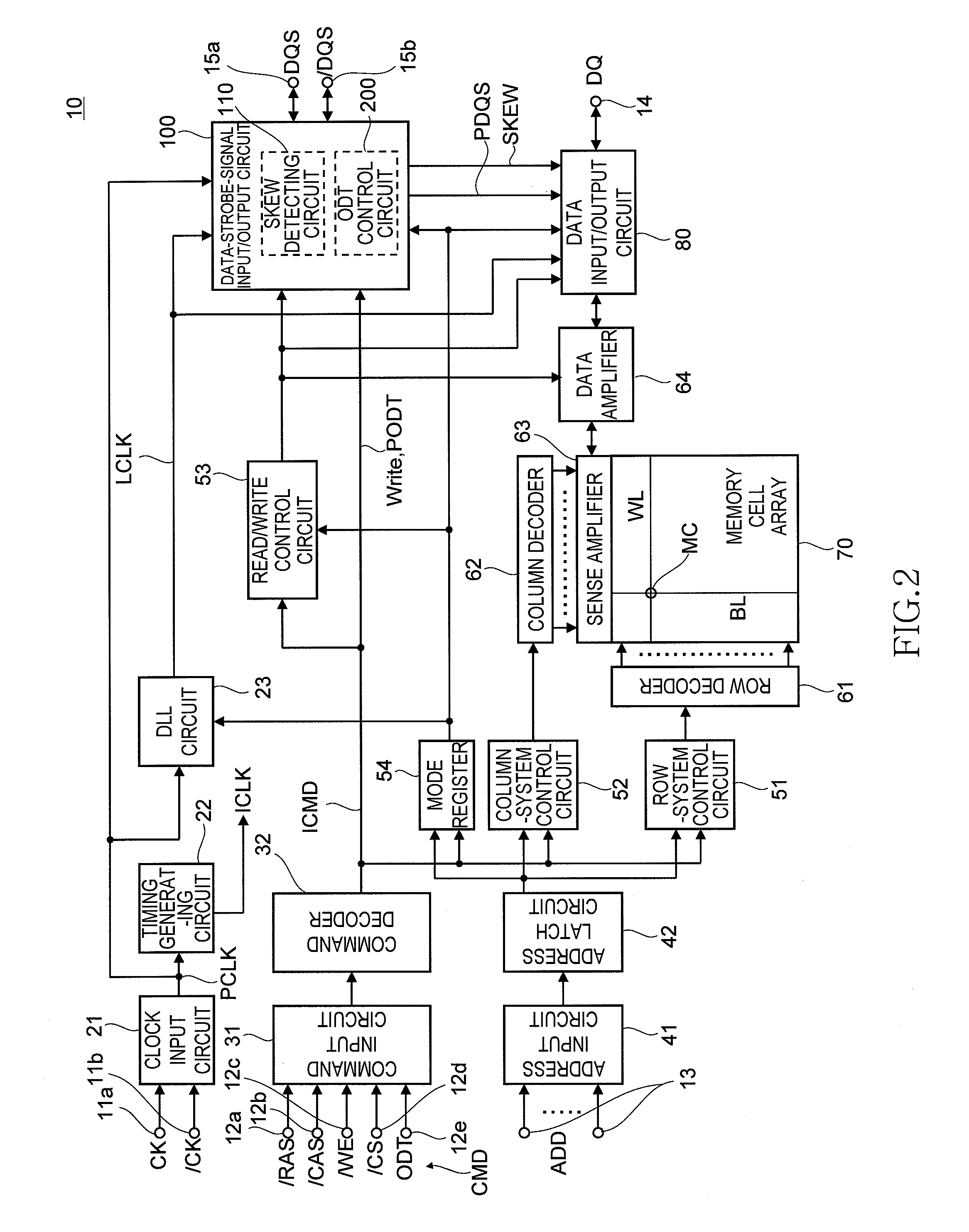

[0027]Preferred embodiments of the present invention will be explained below in detail with reference to the accompanying drawings.

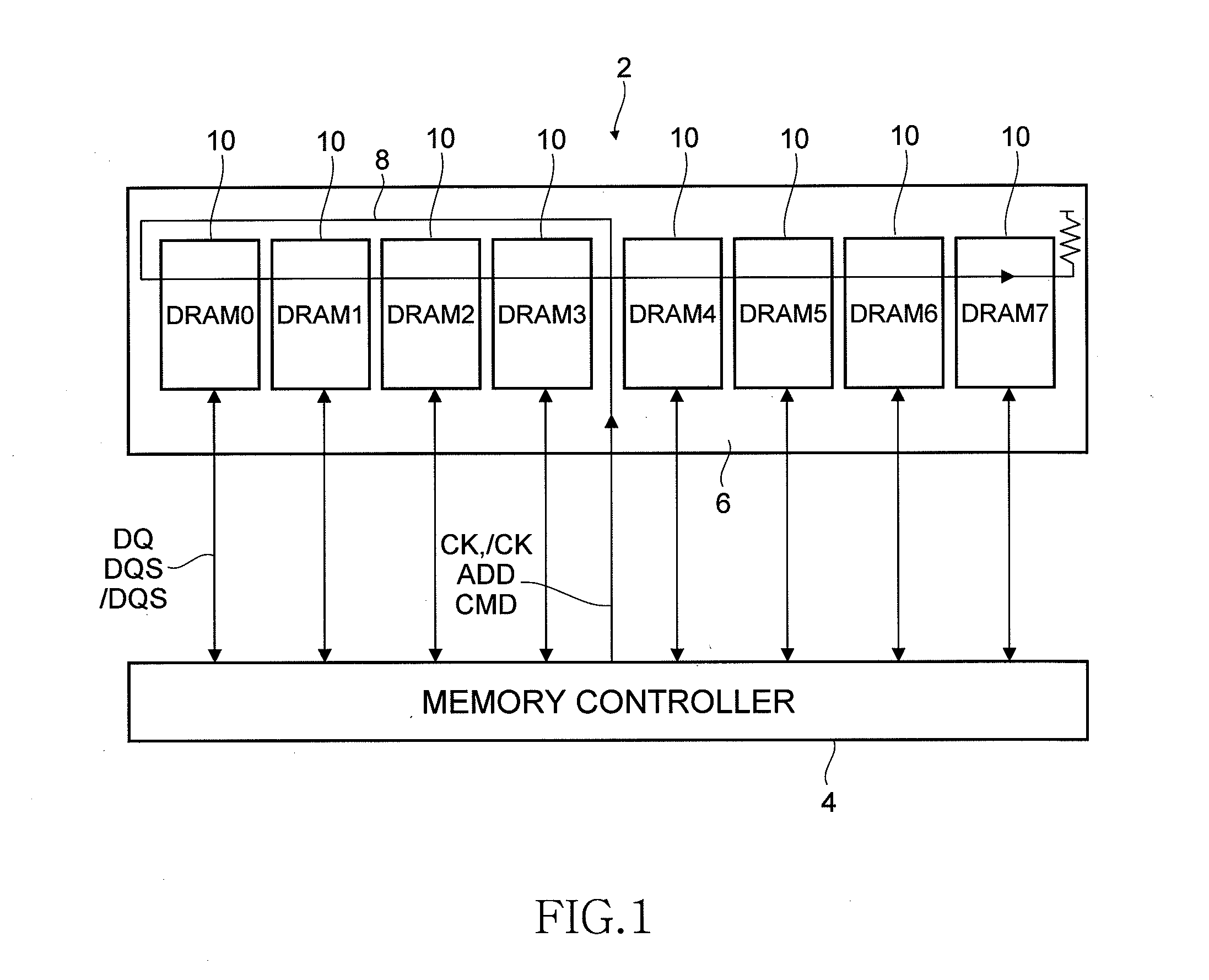

[0028]FIG. 1 shows a configuration of a data processing system according to a preferred embodiment of the present invention.

[0029]The data processing system shown in FIG. 1 includes a memory module 2 and a memory controller 4 connected to the memory module 2. The memory module 2 has plural semiconductor memory devices 10 (DRAM0 to DRAM7) mounted on a module substrate 6. While the memory module 2 shown in FIG. 1 has eight DRAMs of DRAM0 to DRAM7 on the module substrate 6, the number of the semiconductor memory devices 10 mounted on the module substrate 6 is not limited thereto. The semiconductor memory devices 10 can be mounted on either one side or both sides of the module substrate 6. The structure and material of the module substrate 6 are not particularly limited.

[0030]The type of the semiconductor memory devices 10 is not also particularly limited. I...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com