Full-digital clock correction circuit and method thereof

a technology of digital clock and correction circuit, which is applied in the direction of pulse automatic control, pulse manipulation, pulse technique, etc., can solve the problems of inability to adopt the positive and negative edges of clock signals for accelerating digital data extraction, errors may occur during data acquisition, and the cycle of clock signals in digital devices is not equal to 50%, so as to improve the duty-cycle correction accuracy and widen the frequency operating range , the effect of wide duty-cycle range of input clock

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015]In order to make the structure and characteristics as well as the effectiveness of the present invention to be further understood and recognized, the detailed description of the present invention is provided as follows along with embodiments and accompanying figures.

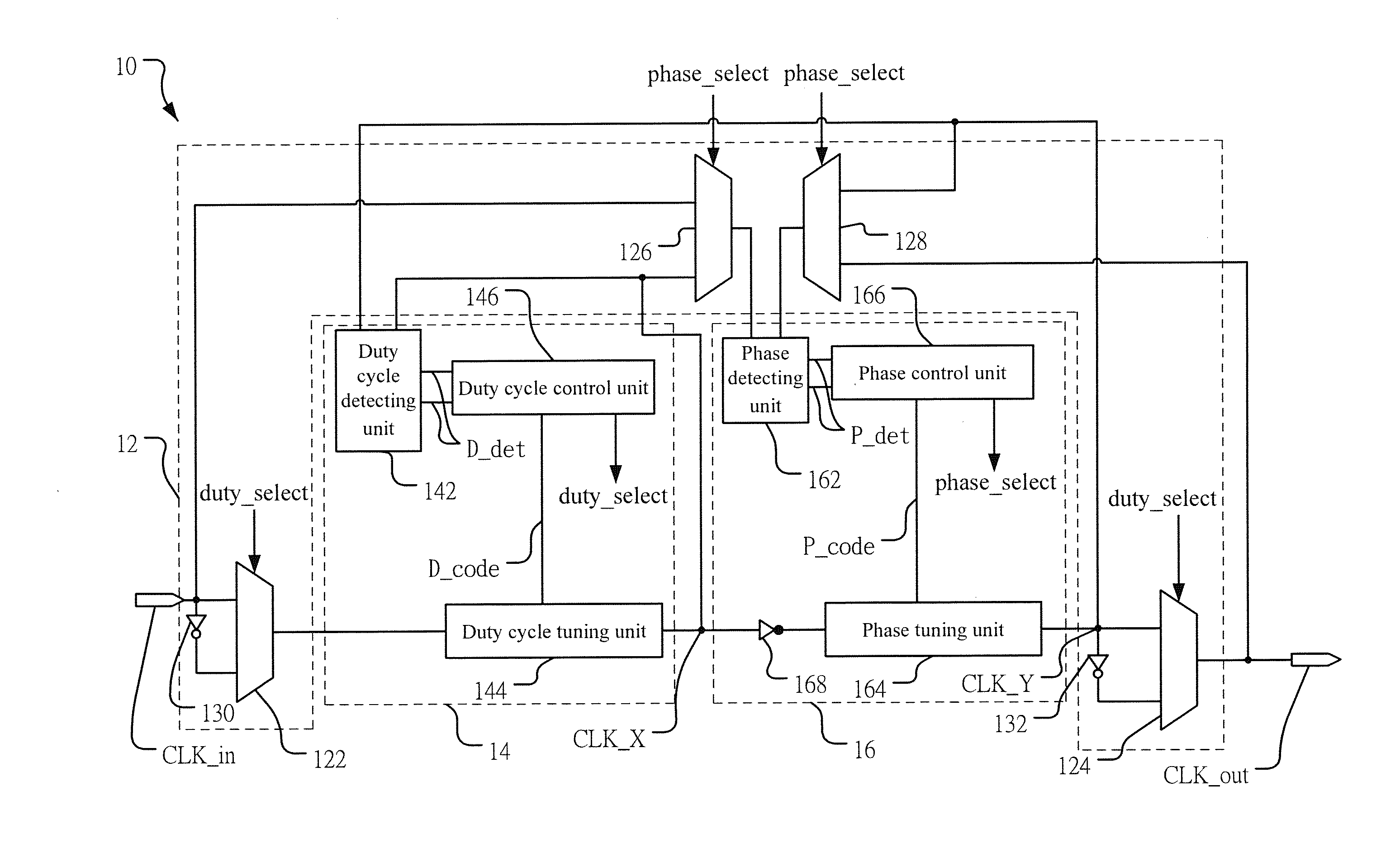

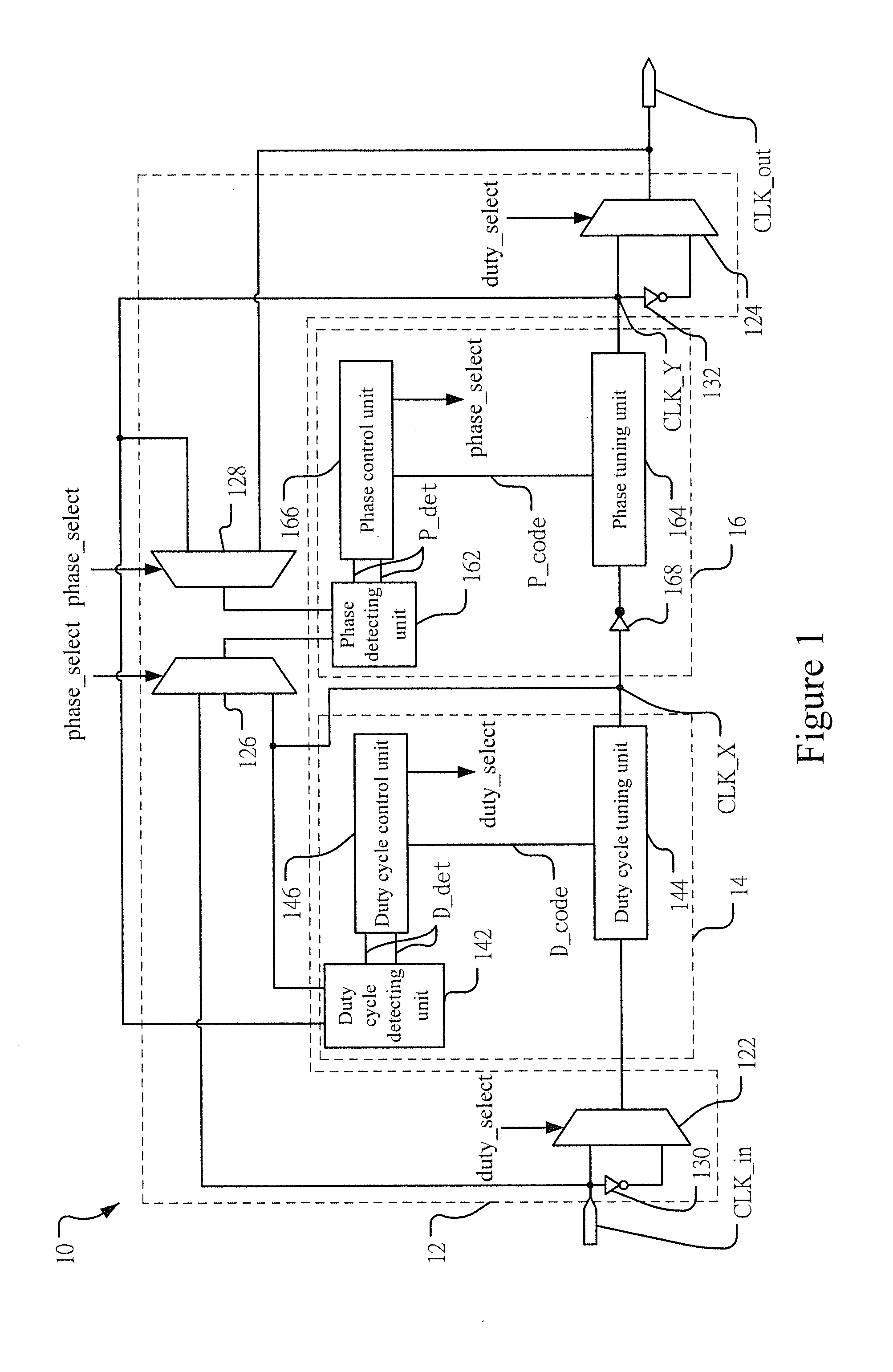

[0016]FIG. 1 shows a circuit diagram according to an embodiment of the present invention. As shown in the figure, the full-digital clock duty cycle correction circuit 10 according to the present invention comprises a sampling unit 12, a duty cycle correcting module 14, and a phase-lock module 16. In addition, the sampling unit 12 further comprises a first multiplexer 122, a second multiplexer 124, a third multiplexer 126, a fourth multiplexer 128, a first inverter 130, and a second inverter 132. The duty cycle correction module 14 further comprises a duty cycle detecting unit 142, a duty cycle tuning unit 144, and a duty cycle control unit 146. Besides, the phase-lock module 16 further comprises a phase detecting u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More