Mounting method and mounting device

a mounting method and mounting device technology, applied in semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve problems such as difficult prevent fluctuations in the temperature of heated semiconductor chips, circuit boards, mounting heads, etc., to achieve stable and accurate mounting, prevent thermal expansion and contraction, and prevent thermal expansion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

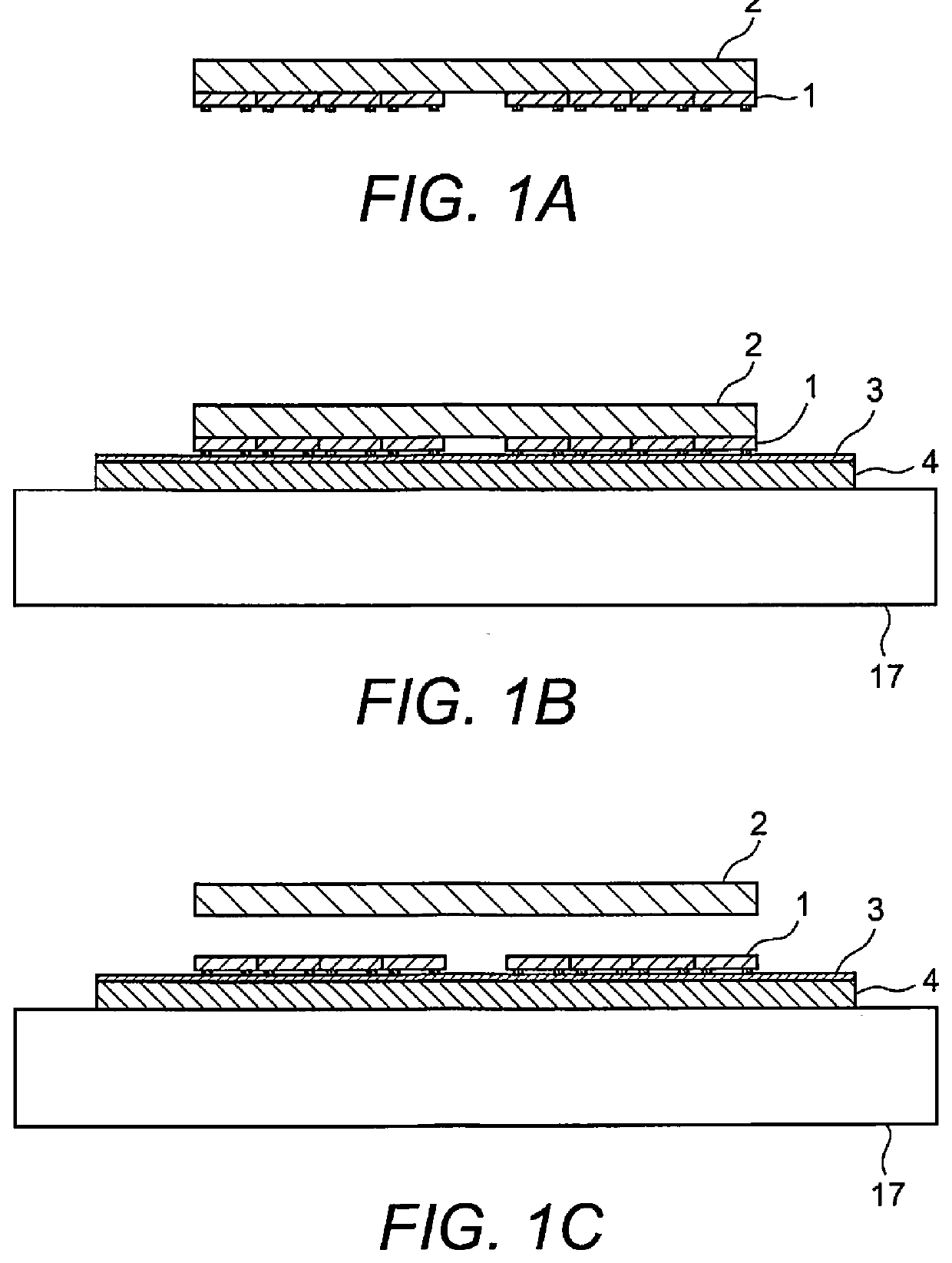

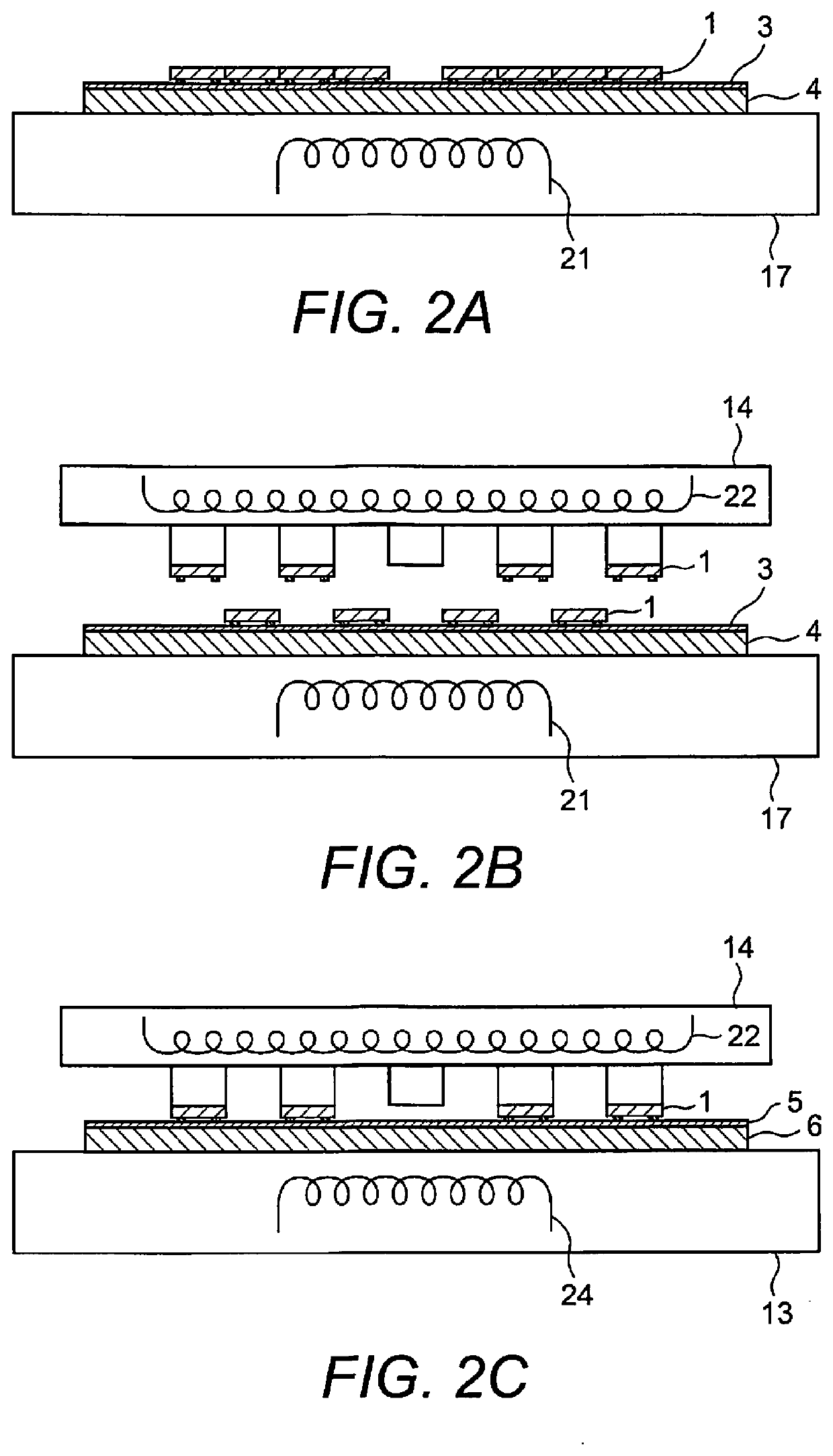

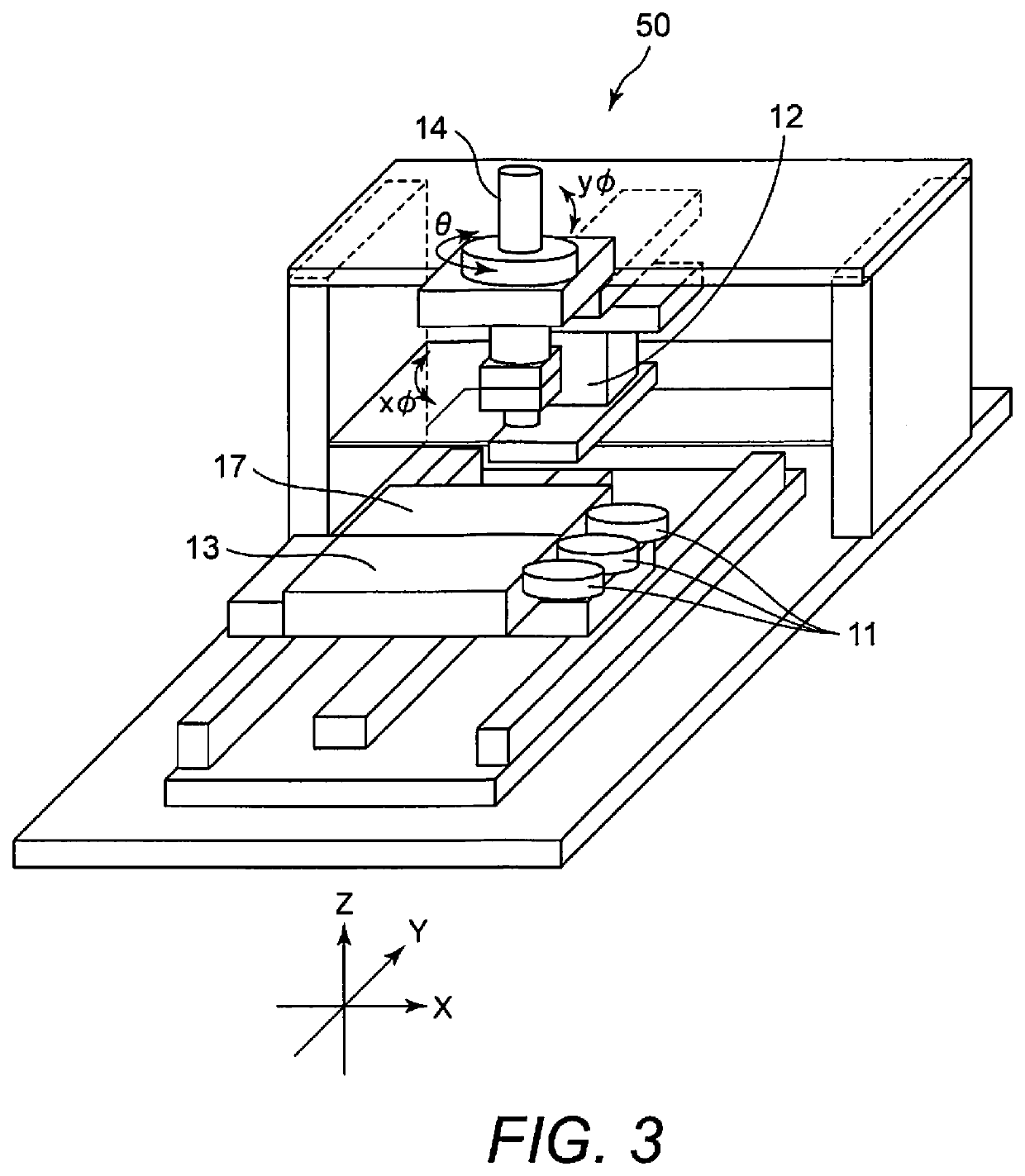

[0053]A first embodiment of the present invention will be described through reference to FIGS. 1A to 5B. FIGS. 1A, 1B and 1C are diagrams illustrating the first half of a mounting method in the first embodiment of the present invention. FIGS. 2A, 2B and 2C are diagrams illustrating the second half of the mounting method in the first embodiment of the present invention. FIG. 3 is a diagram illustrating a mounting device in the first embodiment of the present invention. FIG. 4 is a diagram illustrating a head portion of the mounting device in the first embodiment of the present invention. FIGS. 5A and 5B are diagrams illustrating the adjustment of the parallelism of the head of the mounting device in the first embodiment of the present invention.

[0054]In the present invention, of the two main faces of a semiconductor chip, the face held by the carrier substrate shall be termed the first face, the face on the opposite side from the first face is defined as the second face, and it shall...

second embodiment

[0082]A second embodiment of the present invention differs from the first embodiment in that a head 114 that picks up the semiconductor chips 1 from the adhesive sheet 4 whose adhesive strength has been reduced picks up the semiconductor chips 1 one at a time. Just as with the head 14 in the first embodiment, the head 114 comprises a heating component comprising a heater 122.

[0083]The mounting method in the second embodiment of the present invention will be described through reference to FIGS. 6A to 6C. FIGS. 6A, 6B and 6C are diagrams illustrating the second half of a mounting method in the second embodiment of the present invention. The first half of the mounting method in the second embodiment is the same as in the first embodiment. In the second half of the mounting method in the second embodiment, the adhesive strength reduction step shown in FIG. 6A is executed as in the first embodiment. In the adhesive strength reduction step, the adhesive strength of the adhesive film 3 of ...

third embodiment

[0087]A third embodiment of the present invention differs from the first and second embodiments in that the semiconductor chips I are pressed in order to prevent the semiconductor chips 1 from scattering due to the reduction in the adhesive strength of the adhesive sheet 4 in the adhesive strength reduction step.

[0088]The third embodiment of the present invention will be described through reference to FIG. 7. FIG. 7 is a diagram illustrating the adhesive strength reduction step in the third embodiment of the present invention. In the third embodiment, as shown in FIG. 7, a mounting device 50 is provided with a pressing component 231, and can be pressed and moved in the Z direction by a drive mechanism (not shown). In the adhesive strength reduction step, the pressing component 231, which has been heated to the specific temperature in the adhesive strength reduction step described in the first embodiment, presses on the semiconductor chips 1 held by the adhesive sheet 4, the semicond...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More