Method of forming trench isolation having polishing step and method of manufacturing semiconductor device

a technology of trench isolation and polishing step, which is applied in the direction of semiconductor/solid-state device manufacturing, electrical equipment, basic electric elements, etc., can solve the problems of difficult polishing and wire disconnection, and achieve the effect of satisfying the flattening shape, easy removal, and convenient removal

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example 1

In this example, the present invention is applied to the formation of an integrated a semiconductor device and, in particular, to the formation of trench isolation in the semiconductor device.

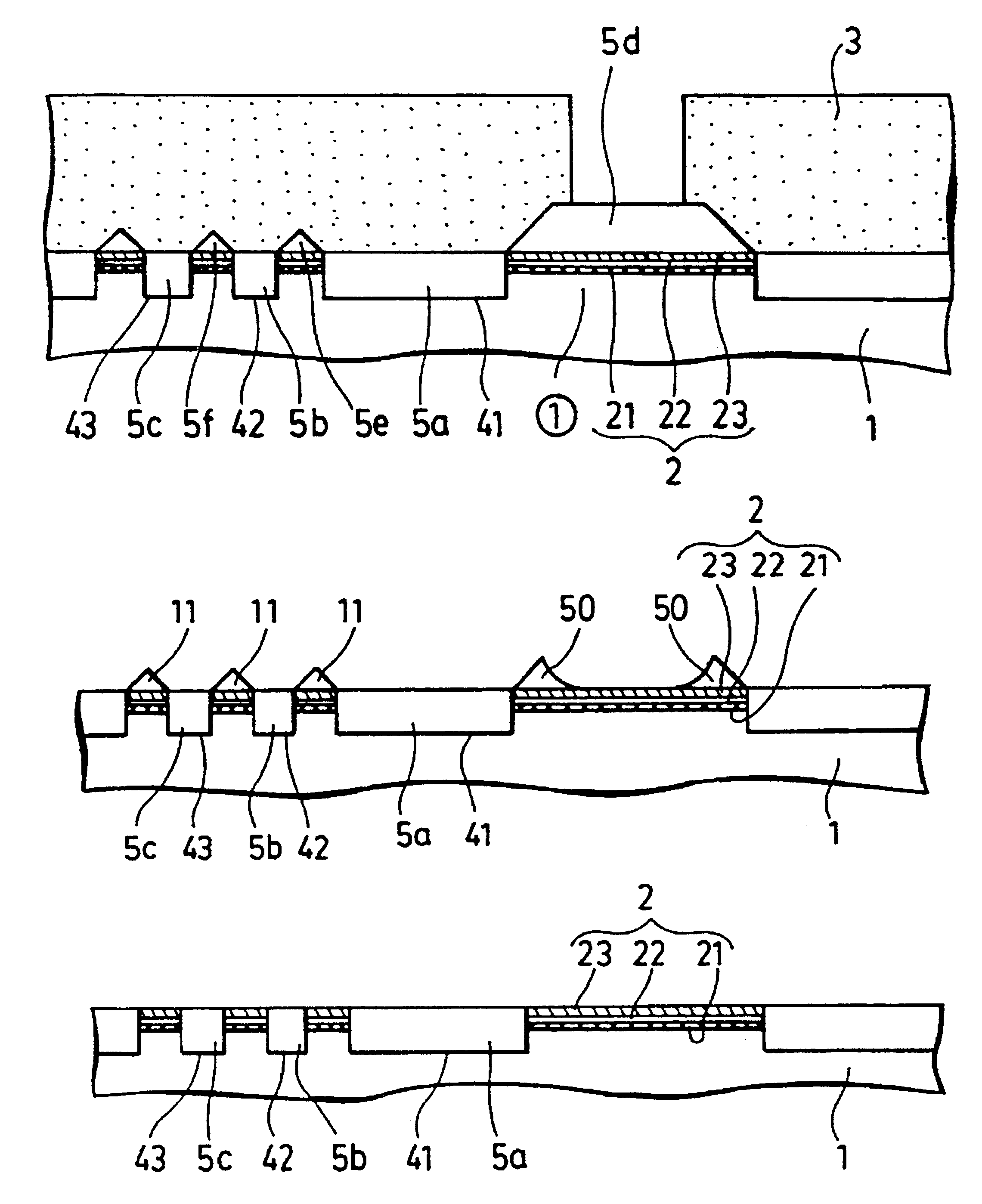

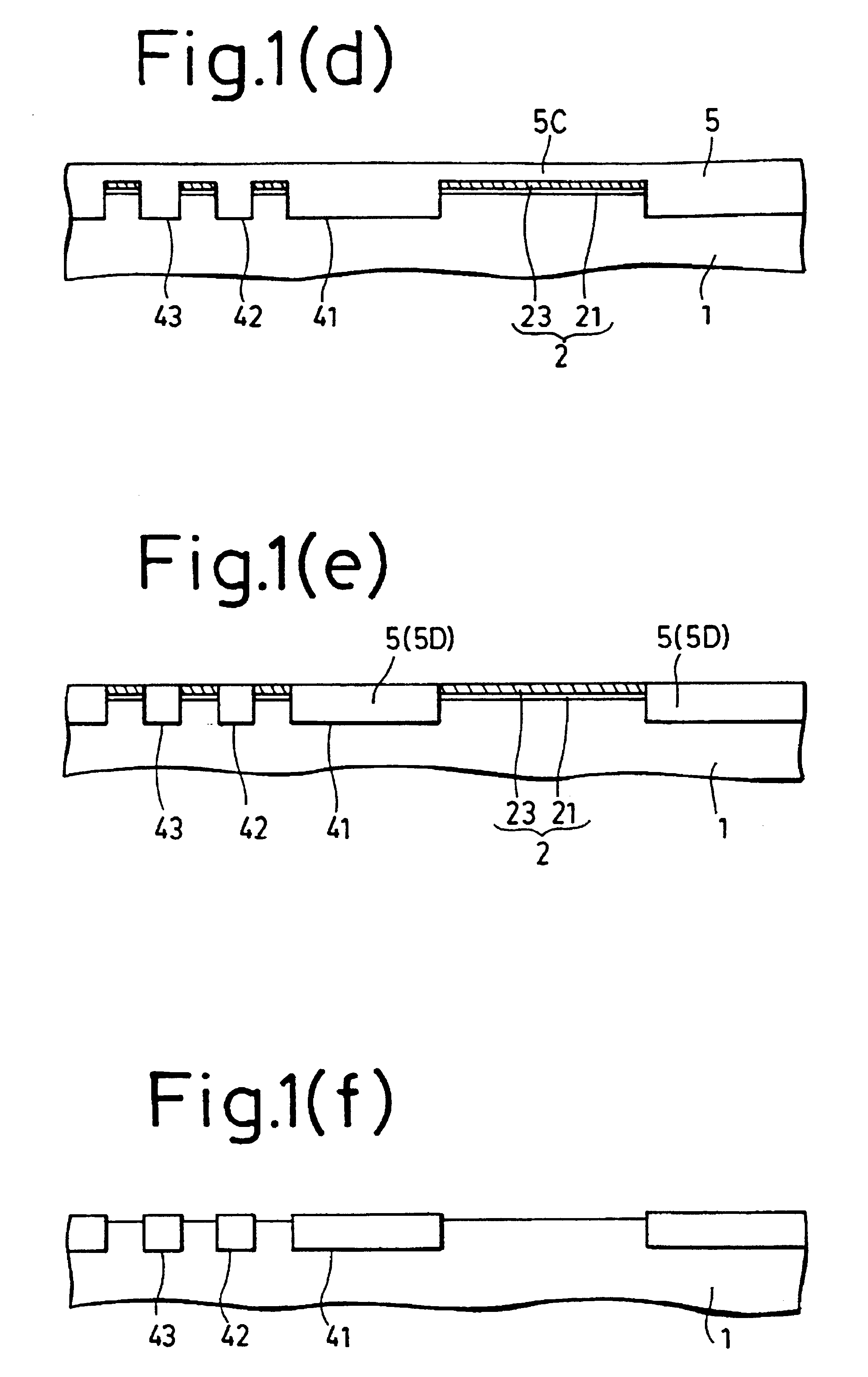

In this example, a structure as shown in FIG. 1(a) is obtained by burying trenches 41-43 by a deposition means that conducts etching and deposition simultaneously (a bias ECR-CVD process is used in this example). Then, an isotropic etching step for isotropically etching the burying material as shown by a broken line in FIG. 1(b) is performed to obtain a structure as shown in FIG. 1(c) before the polishing step. Subsequently, a flat structure as shown in FIG. 1(d) is obtained after the polishing step.

The burying material 5 on a wide protrusion region is etched by the isotropic etching step in FIG. 1(b) into a shape substantially uniform with other portions as shown in FIG. 1(c). Accordingly, a satisfactory flattening is attained by polishing the remaining protruding portions.

More specifically, t...

example 2

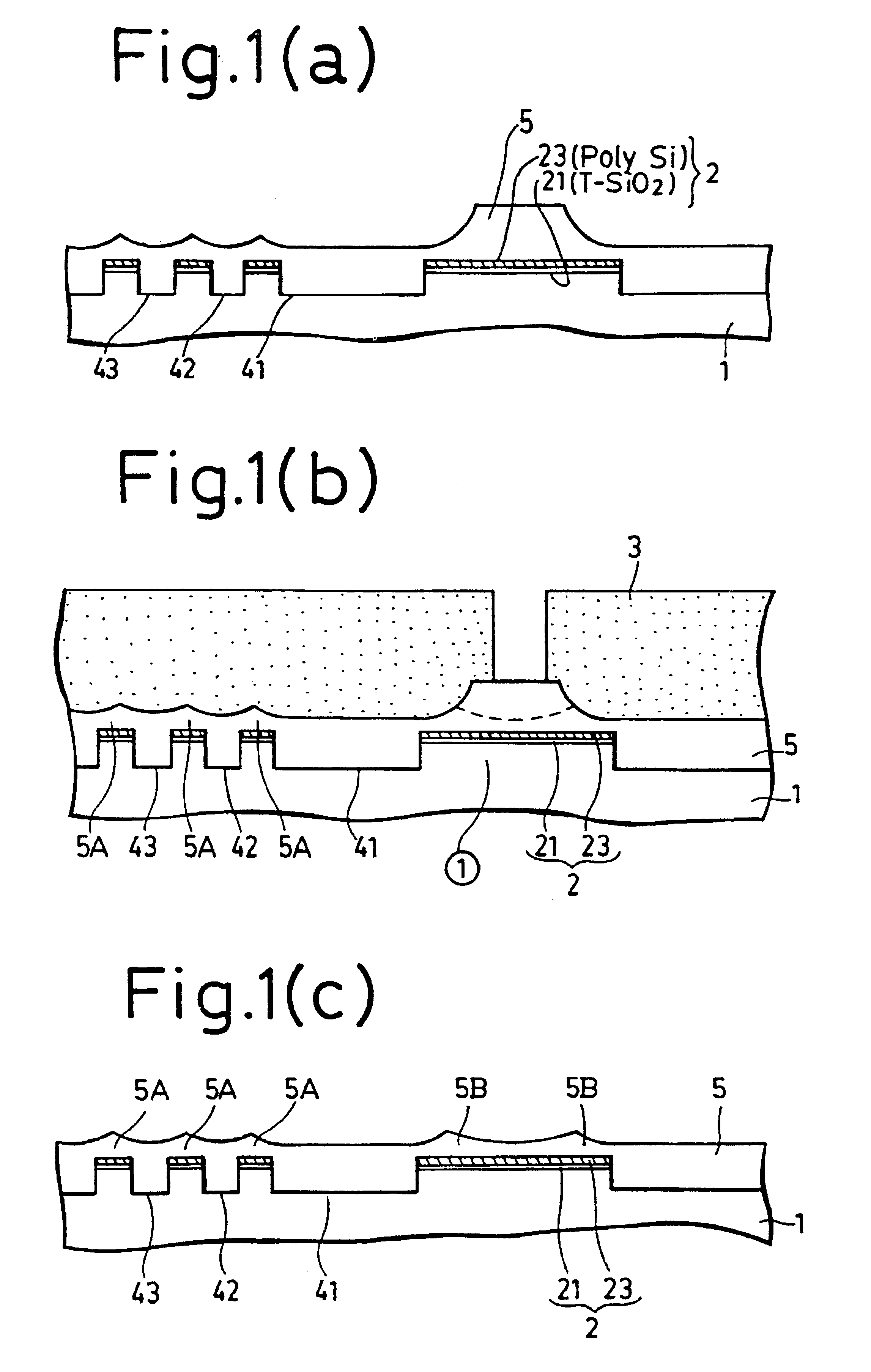

Descriptions will be made to Example 2 which includes formation of trench isolation and manufacture of a semiconductor device.

In Example 1, when the burying material is etched back as far as the upper portion of the trench opening in the state shown in FIG. 2(d), that is, when it is to be etched back by the thickness of the burying material on the protrusion region shown by 5C in FIG. 2(d), since the and point can not be judged, it is difficult to control the etching film thickness as the burying material 5 for the isolation portion shown in FIG. 2(e). Example 2 undertakes to overcome the problem.

In Example 2, since SiO.sub.2 which is the burying material after resist patterning can be etched as far as the surface of the support layer is exposed and the burying material (SiO.sub.2) on the protrusion region can be removed completely by polishing in the next step, etching back which is necessary in Example 1 is no longer required.

In this example, a substrate 1 to be formed with trench...

examples 3 , 4

EXAMPLES 3, 4

The following samples are modified from Examples 1-2 described above. While isotropic etching is applied by wet etching using an etching solution before the polishing of the burying material in Examples 1, 2, isotropic etching was conducted by means of dry etching in these examples.

In the examples, SiO.sub.2 as the burying material 5 was isotropically dry etched under the following conditions, instead of etching by hydrofluoric acid as in Examples 1 and 2:

Etching apparatus used: parallel flat type ether

Pressure: 2300 mtorr (306 Pa)

RF power: 550 W

Gas system used: NF.sub.3 = 300 cc / min He= 200 cc / min

Temperature: 80.degree. C.

Satisfactory isotropic etching could be attained by the conditions described above. The conditions were set in order to increase the power of the conducing reaction using fluoric acid radicals as a main etchant and increase the pressure for reducing the directionality of ions (to shorten the mean free path), thereby attaining isotropic etching.

Other p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More