Bitline precharging circuit and method

A charging circuit and bit line technology, applied in information storage, static memory, digital memory information, etc., can solve the problems of slow pre-charging speed of three-variable CAM memory array, not suitable for high-speed applications, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

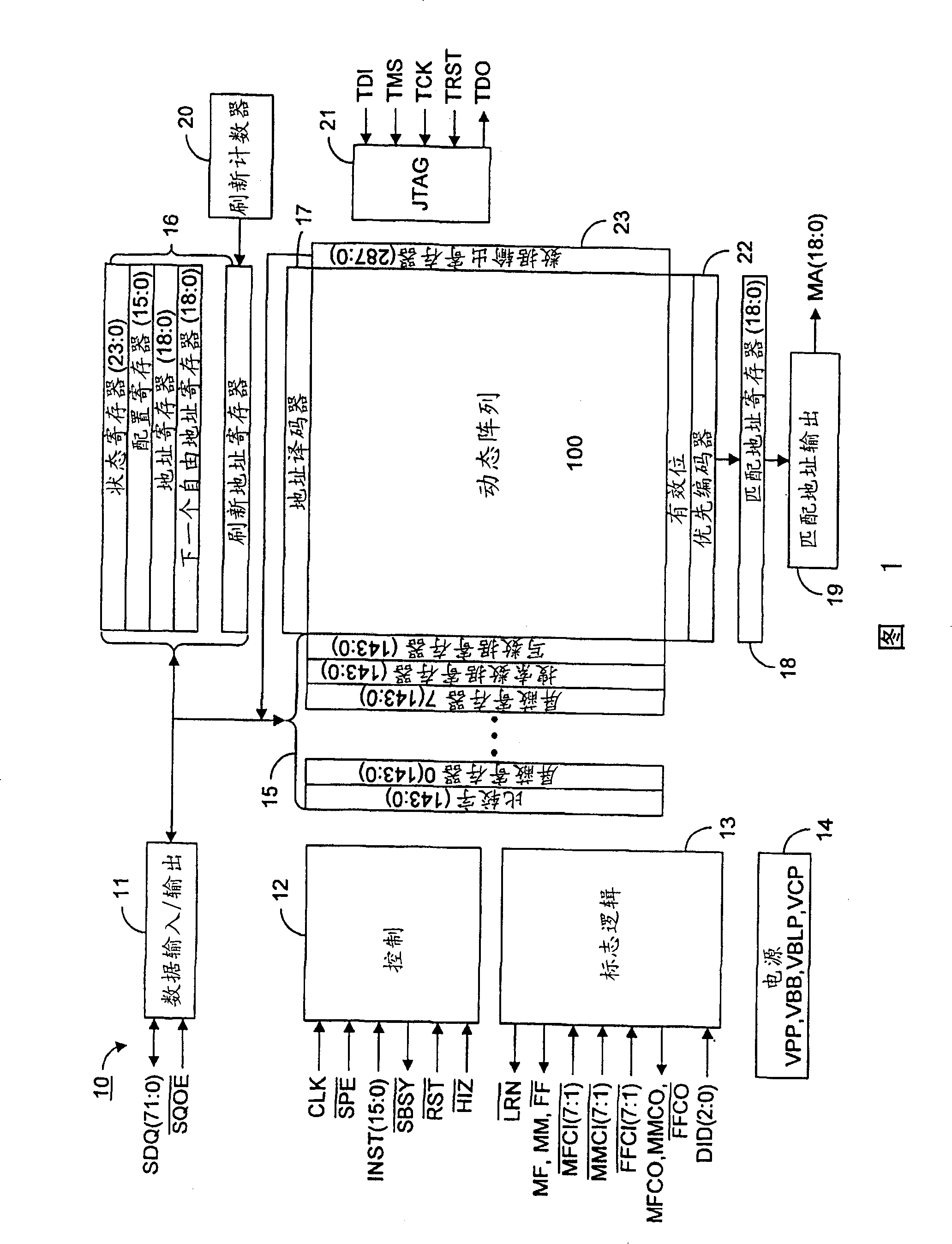

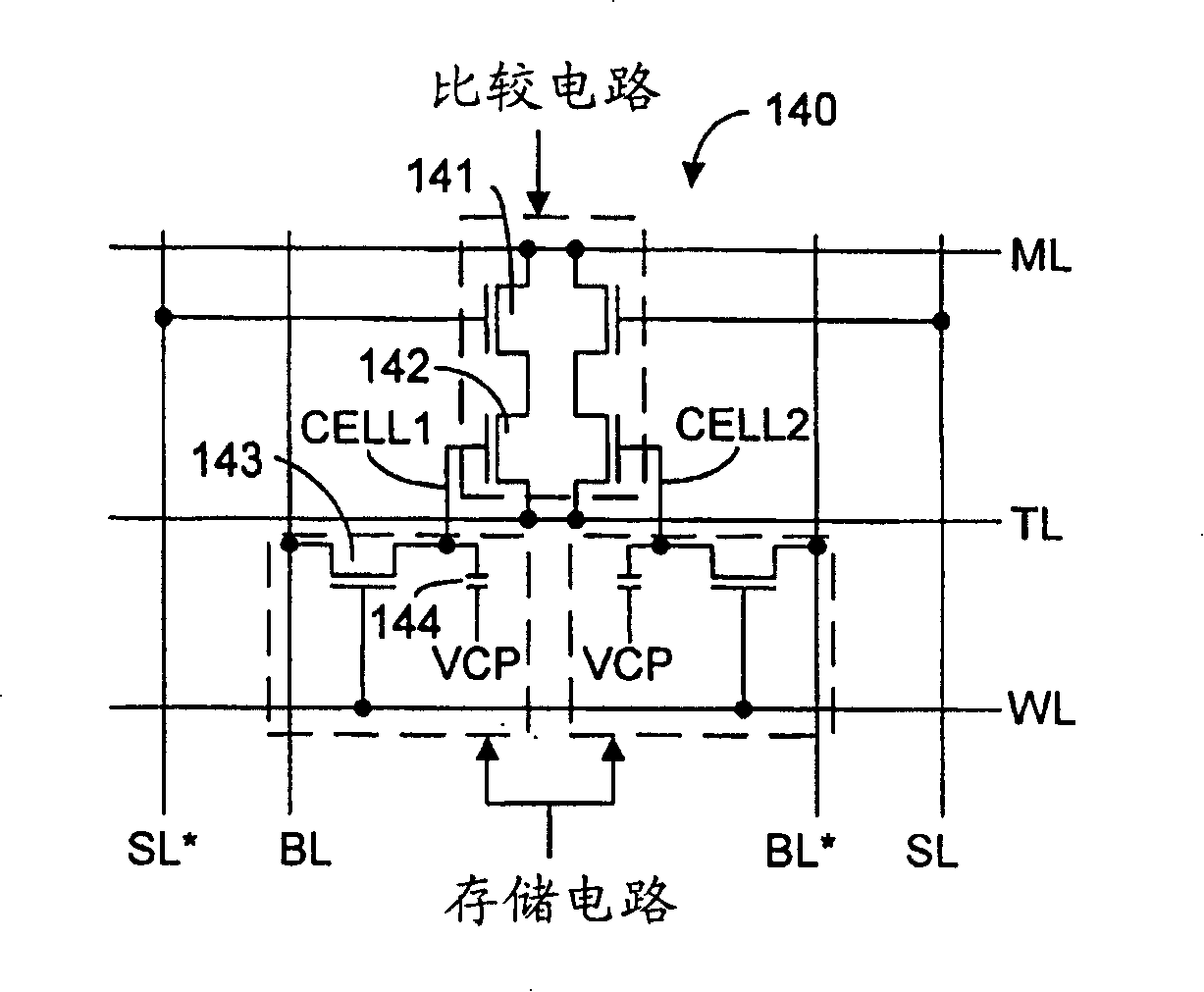

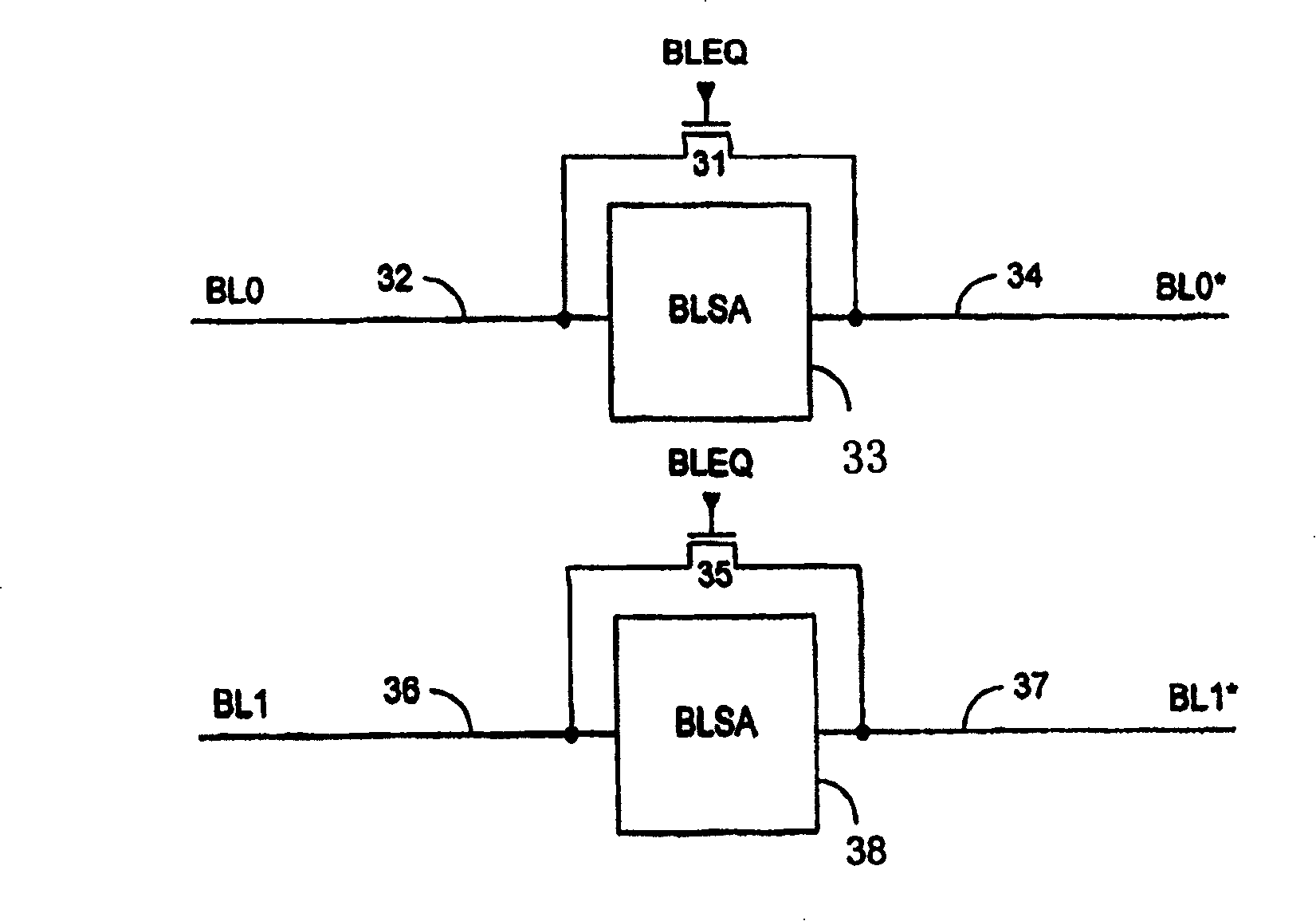

[0036] In general, the present invention provides a bitline structure and method for fast equalization of bitlines in a high density packaged trivariate content addressable memory. More specifically, the bit line structure of the present invention is a hybrid structure combining the high density of the open bit line structure and the high precharge speed of the folded bit line structure. Data read and write operations are performed in a manner consistent with conventional open bit line structures, while bit line precharging and equalization are performed in a manner consistent with conventional folded bit line structures.

[0037] Figure 5 shows a general circuit diagram of the hybrid structure of the present invention. Several control signals, word lines and read circuits have been omitted for simplicity of the schematic diagram. exist Figure 6A and 6B A more detailed circuit diagram showing omitted elements of the hybrid structure is shown in . A row 110 of trivariate C...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More