Metal insulating layer-metal capacitance structure and its manufacturing method

A technology of metal capacitors and manufacturing methods, applied to capacitors, fixed capacitor parts, fixed capacitor dielectrics, etc., can solve problems such as reducing product reliability, peeling, and affecting the electrical function of metal capacitors 26, so as to ensure product reliability. , to avoid the effect of upward or lateral diffusion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0027] refer to Figure 3-Figure 7 Shown is a schematic diagram of a method for forming the metal-insulator-metal (MIM) capacitor structure of the present invention.

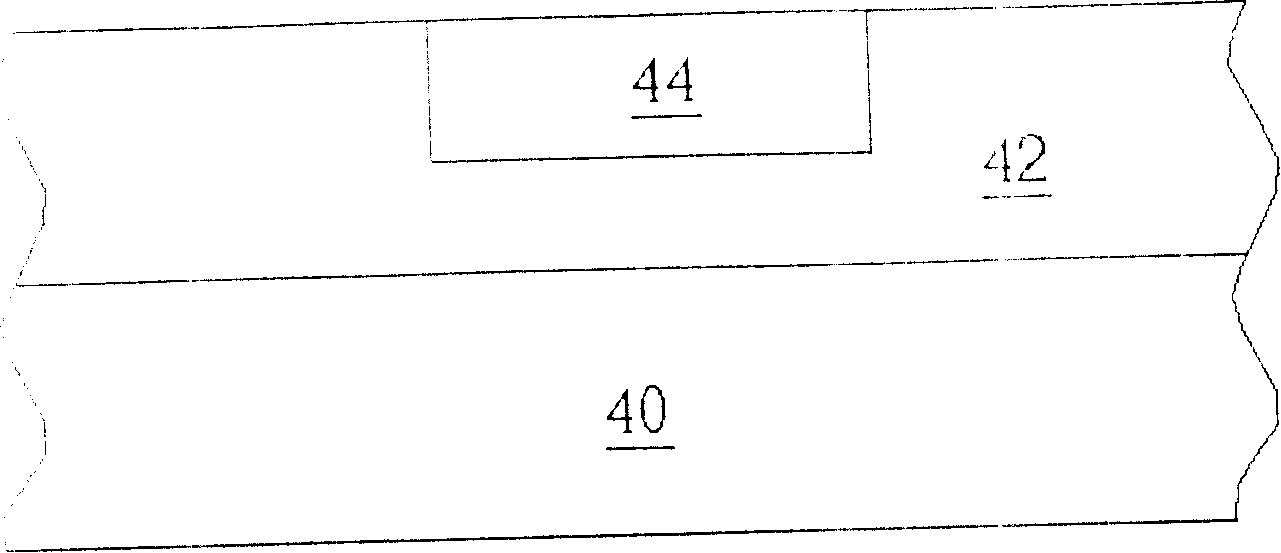

[0028] Such as image 3 As shown, a copper metal layer 44 is disposed in a dielectric layer 42 on a substrate 40 . In the preferred embodiment of the present invention, the copper metal layer 44 is a copper wire in a dual damascene structure (not shown).

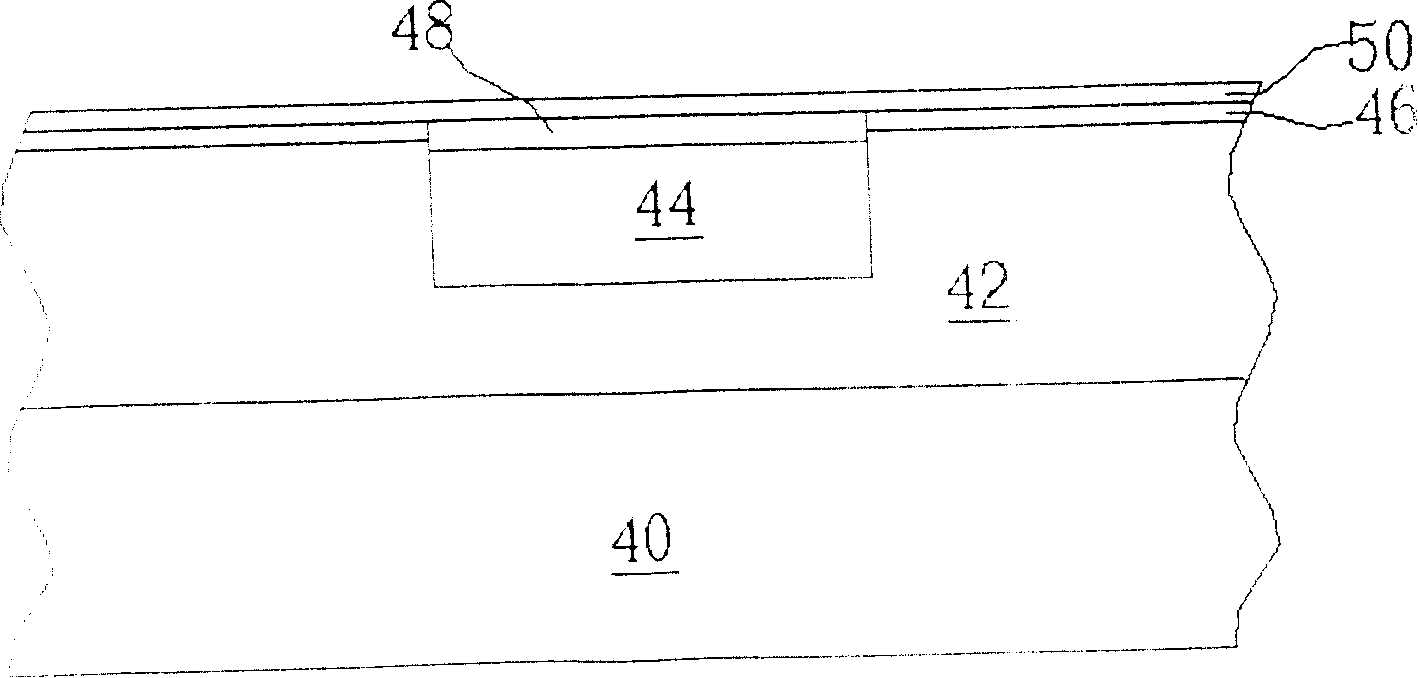

[0029] Such as Figure 4As shown, a sputtering process is first performed to form a first metal layer 46 completely covering the copper metal layer 44 on the copper metal layer 44 . Then perform a rapid thermal oxidation (rapidthermal oxidation, RTO) process, so that the first metal layer 46 in contact with the upper surface of the copper metal layer 44 reacts with the copper metal layer 44 to form an alloy layer 48, and at the same time, it is partially oxidized Or fully oxidize the remaining first metal layer 46 to form a metal oxide layer 50, which cover...

Embodiment 2

[0034] refer to Figure 8 As shown, is a schematic diagram of another embodiment of the MIM capacitor structure 56 of the present invention.

[0035] Such as Figure 8 As shown, the metal oxide layer 50 and the upper pad layer 52 may also only partially cover the alloy layer 48 and the copper metal layer 44 , and the top surface of the alloy layer 48 is roughly aligned with the top surface of the dielectric layer 42 . In subsequent processes, a first via plug 62 and a second via plug 62 may be formed after covering a dielectric layer 66 above the MIM capacitor structure 56 according to product specifications and electrical requirements. The plugs 64 are electrically connected to the upper pad layer 52 and the alloy layer 48 not covered by the metal oxide layer 50 . Since the formation methods and functions of the first metal layer 46 , the alloy layer 48 , the metal oxide layer 50 and the upper pad layer 52 in the second embodiment are the same as those in the preferred embo...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap