Chip testing mechanism and related method

A technology of chip testing and mechanism, applied in the direction of digital circuit testing, electronic circuit testing, measuring electricity, etc., can solve the problem of high manufacturing cost of electronic devices, expensive external high-frequency tester, high cost of high-frequency tester, etc. problems, to achieve the effect of saving manufacturing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings.

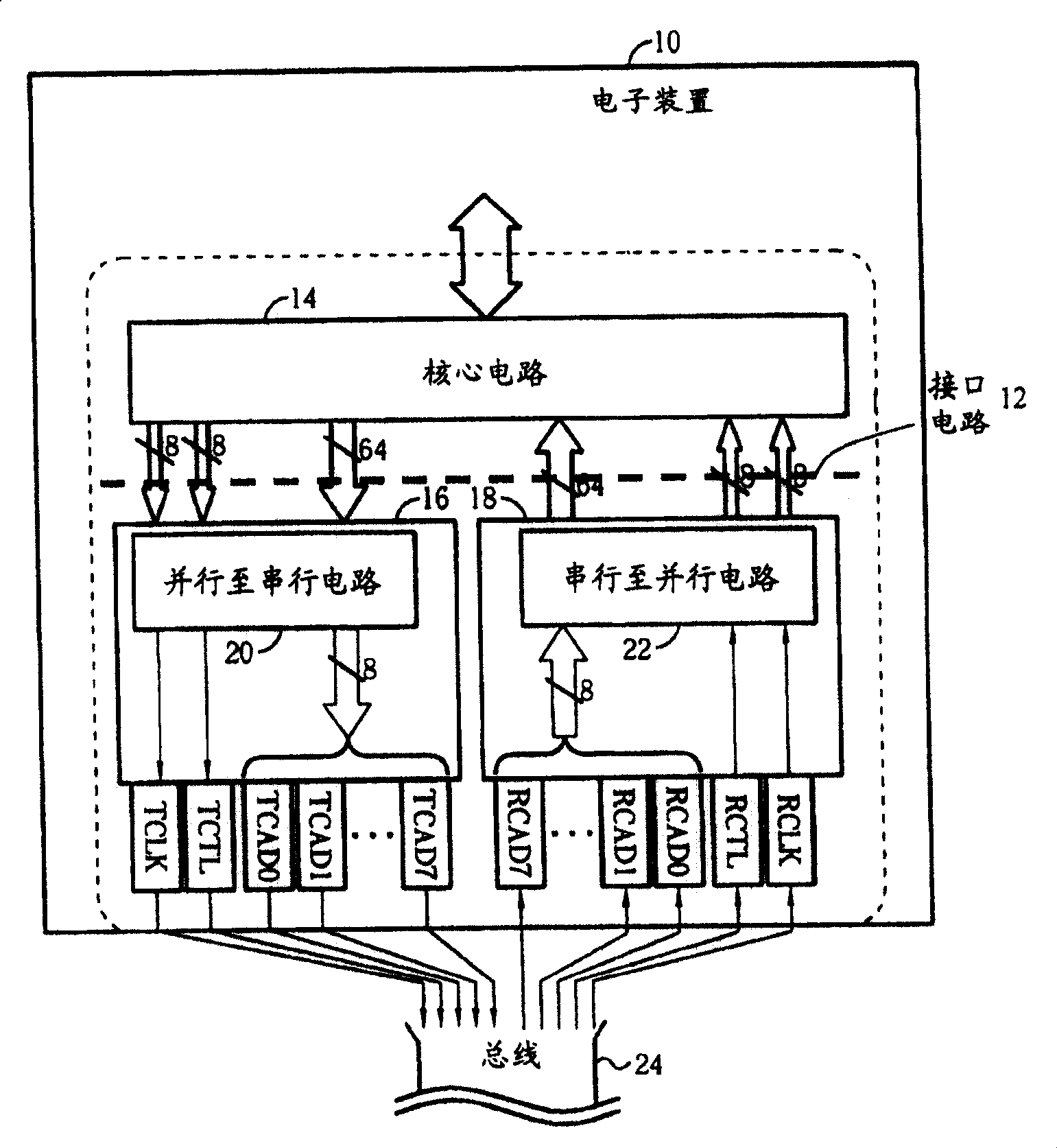

[0018] Please refer to figure 1 ; figure 1 is a schematic diagram of an electronic device 10 with a high-speed bus interface circuit. The electronic device 10 includes a high-speed bus interface circuit 12 and a core circuit 14 . The electronic device 10 may be a chip in an electronic system, such as a chipset in a computer system, and the high-speed bus interface circuit 12 enables the electronic device 10 to exchange information with other electronic devices (not shown) via the high-speed bus 24 with signal. The core circuit 14 is used to master encoding / decoding and control matters related to bus access (eg, determine whether to respond and when to respond after receiving an access request from the bus). In the present invention, the high-speed bus 24 can be a Hyper Transport Bus. In the high-speed bus interface circuit 12, a transmission circuit 16 an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More