Manufacturing method of wafer level testing circuit board and structure thereof

A technology for testing circuit boards and manufacturing methods, which is applied in the direction of measuring electricity, measuring electrical variables, and electronic circuit testing, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] Hereinafter, a preferred embodiment is enumerated in conjunction with some accompanying drawings, in order to further illustrate the components and effects of the present invention as follows:

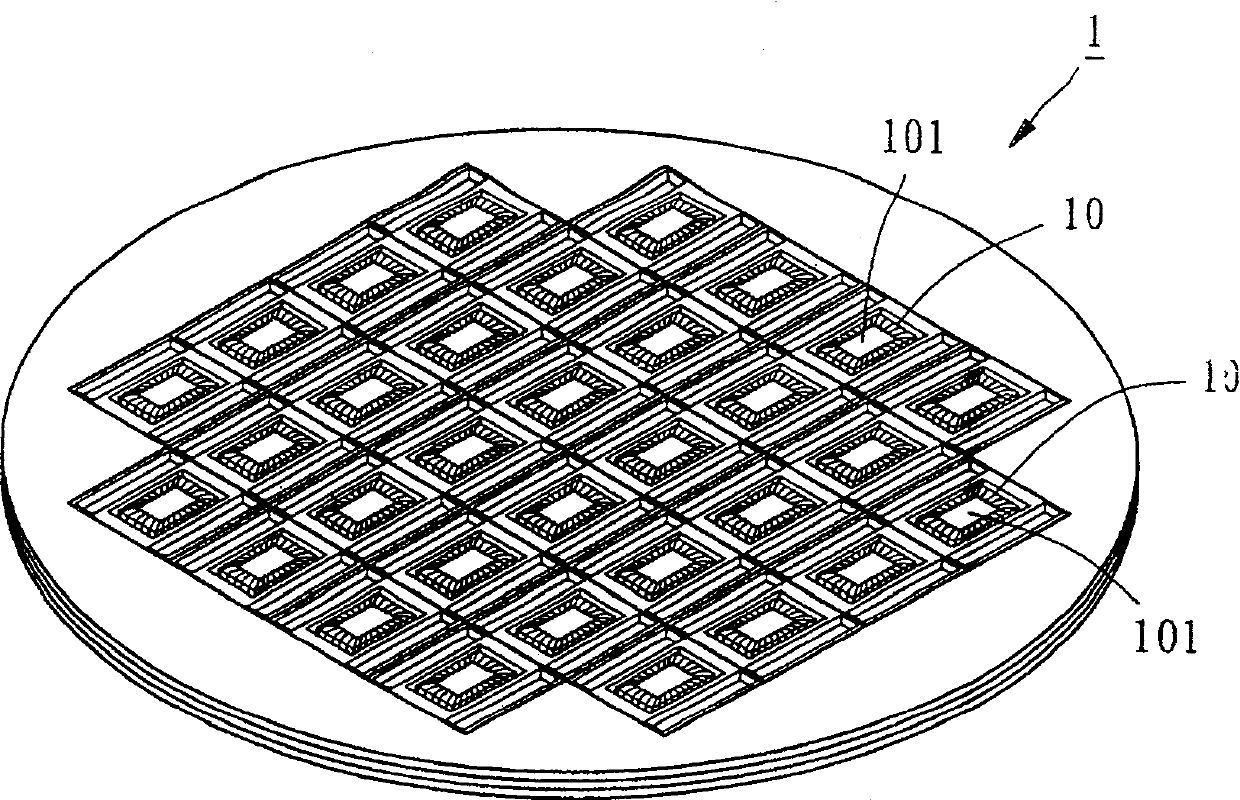

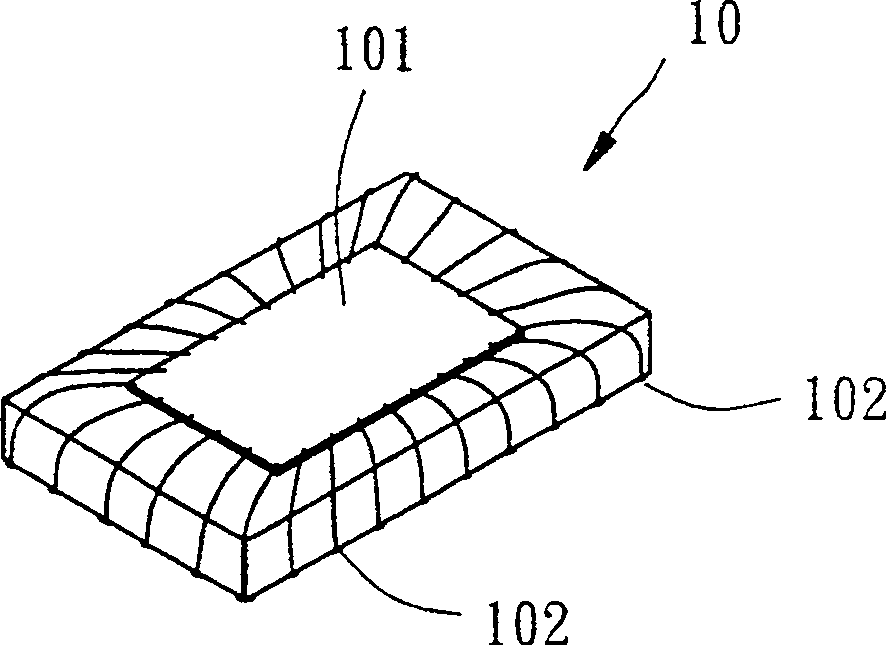

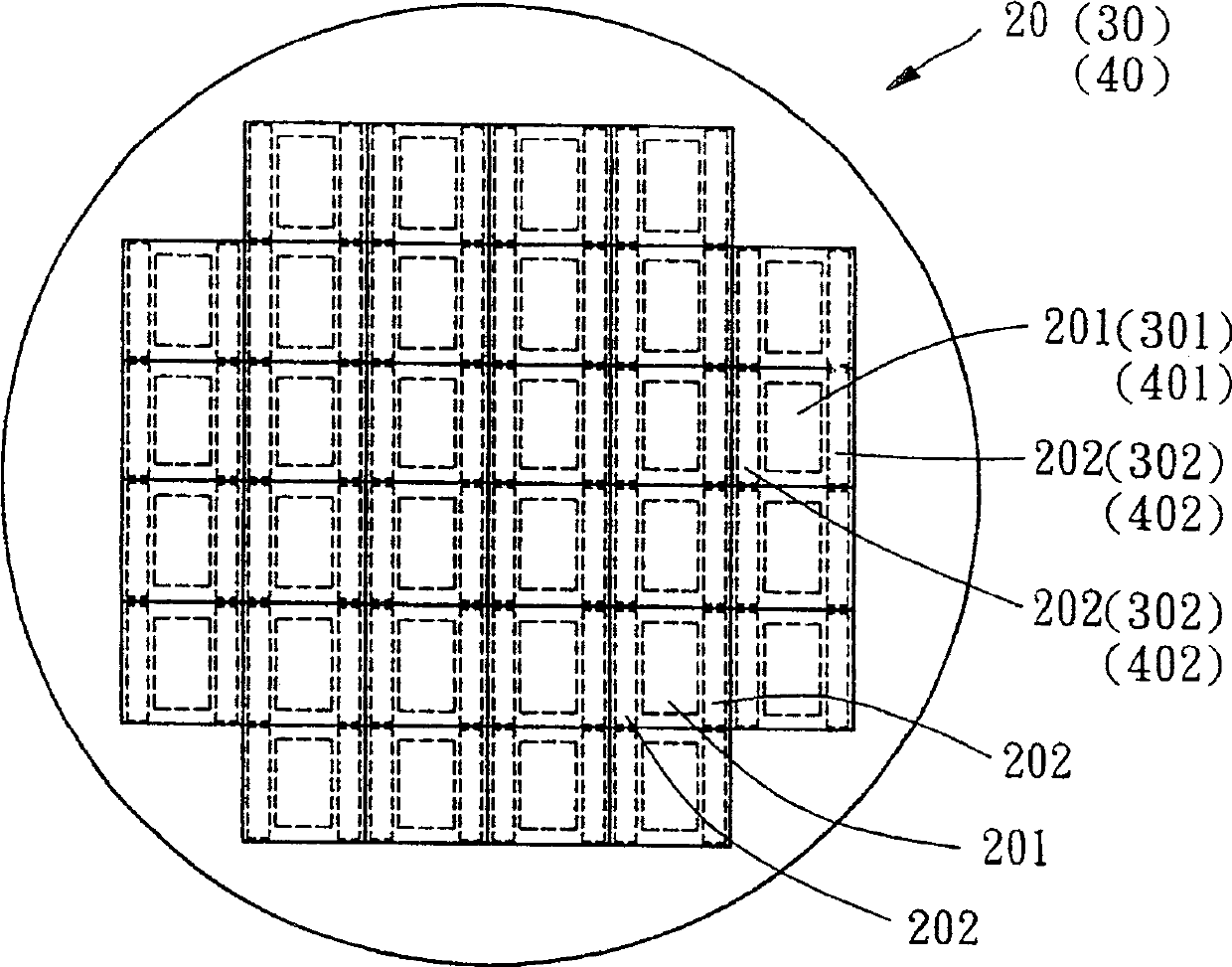

[0022] see Figure 1 to Figure 7 Shown is a test circuit board 1 of the first preferred embodiment provided by the present invention, which can perform wafer-level testing on a plurality of electronic components 10 packaged in modules. These electronic components 10 exemplified in this embodiment are fabricated The integrated circuit chip of each image sensor chip 101 is a modular package assembly after the chip size package (Chip Size Package, CSP) manufacturing process, refer to figure 2 , and there are a plurality of conductive bumps 102 on it, as a connection medium for each image sensor chip 101 to be electrically connected to the external circuit; the following is a further description of the manufacturing steps of the test circuit board 1:

[0023] a. Please see if im...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More