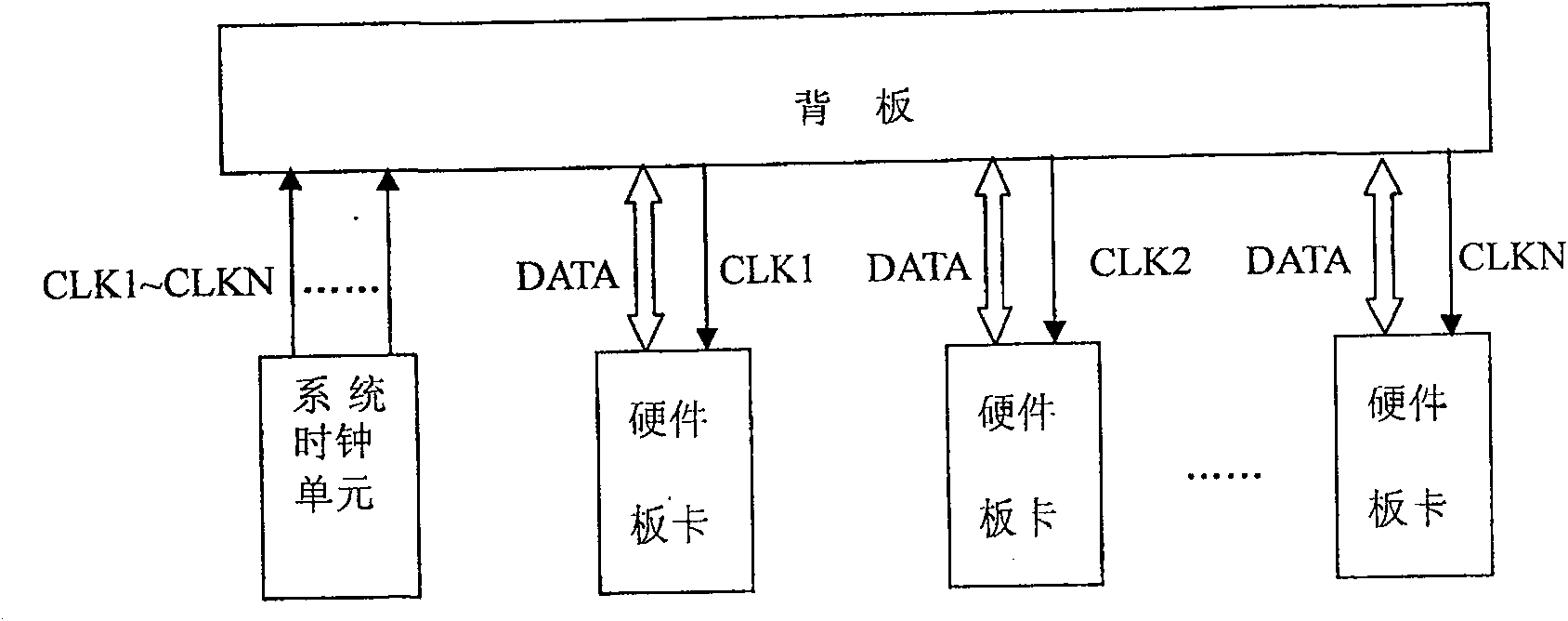

Hardware board backboard interface

A hardware board and backplane technology, applied in the field of communication, can solve problems such as increasing the workload of post-debugging, failing to achieve the desired effect, and unable to ensure reliable data reception, etc., to achieve consistent delay, consistency, and reliable reception The effect of data

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

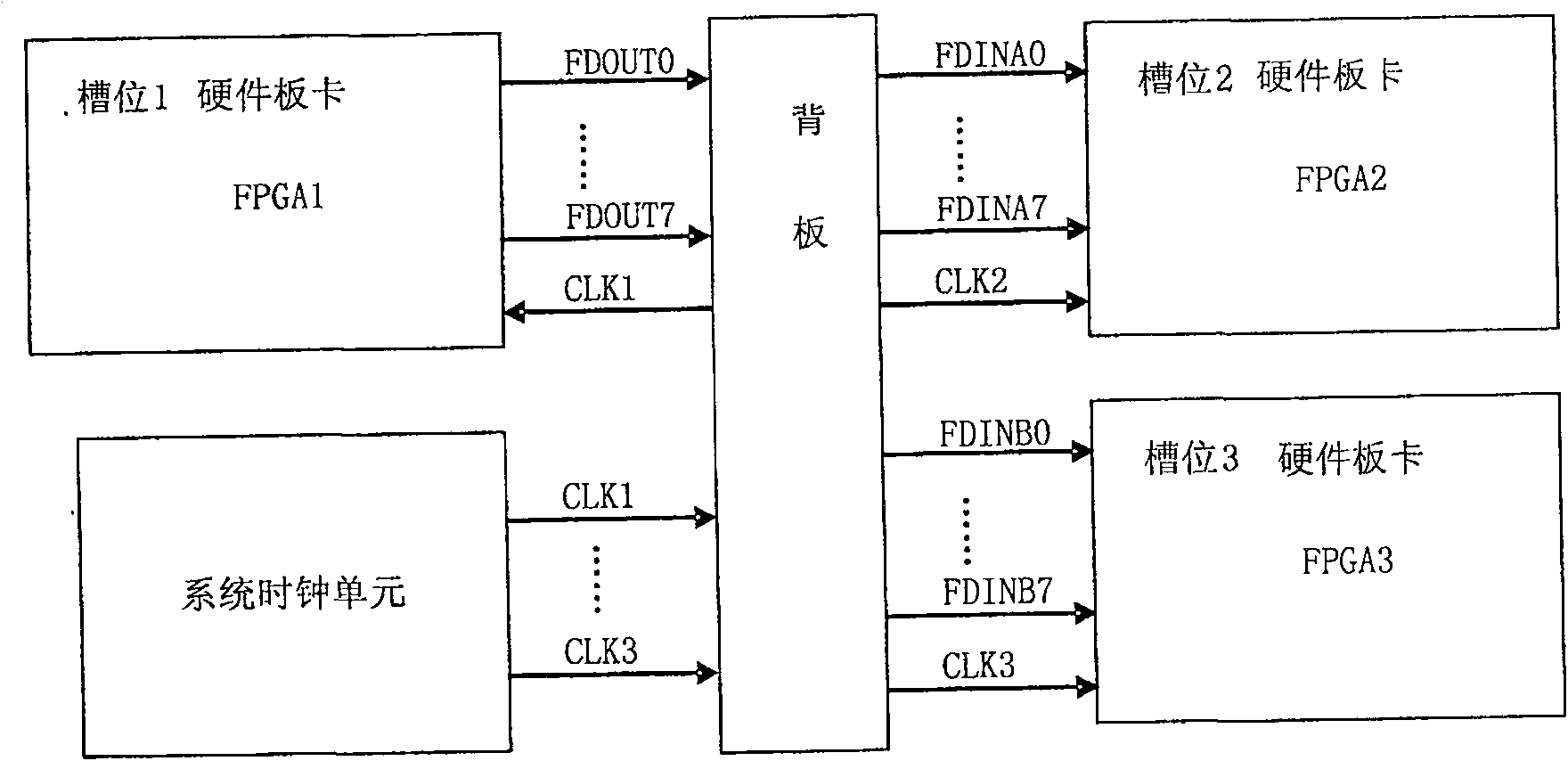

[0019] Various preferred embodiments of the present invention will be described in detail below.

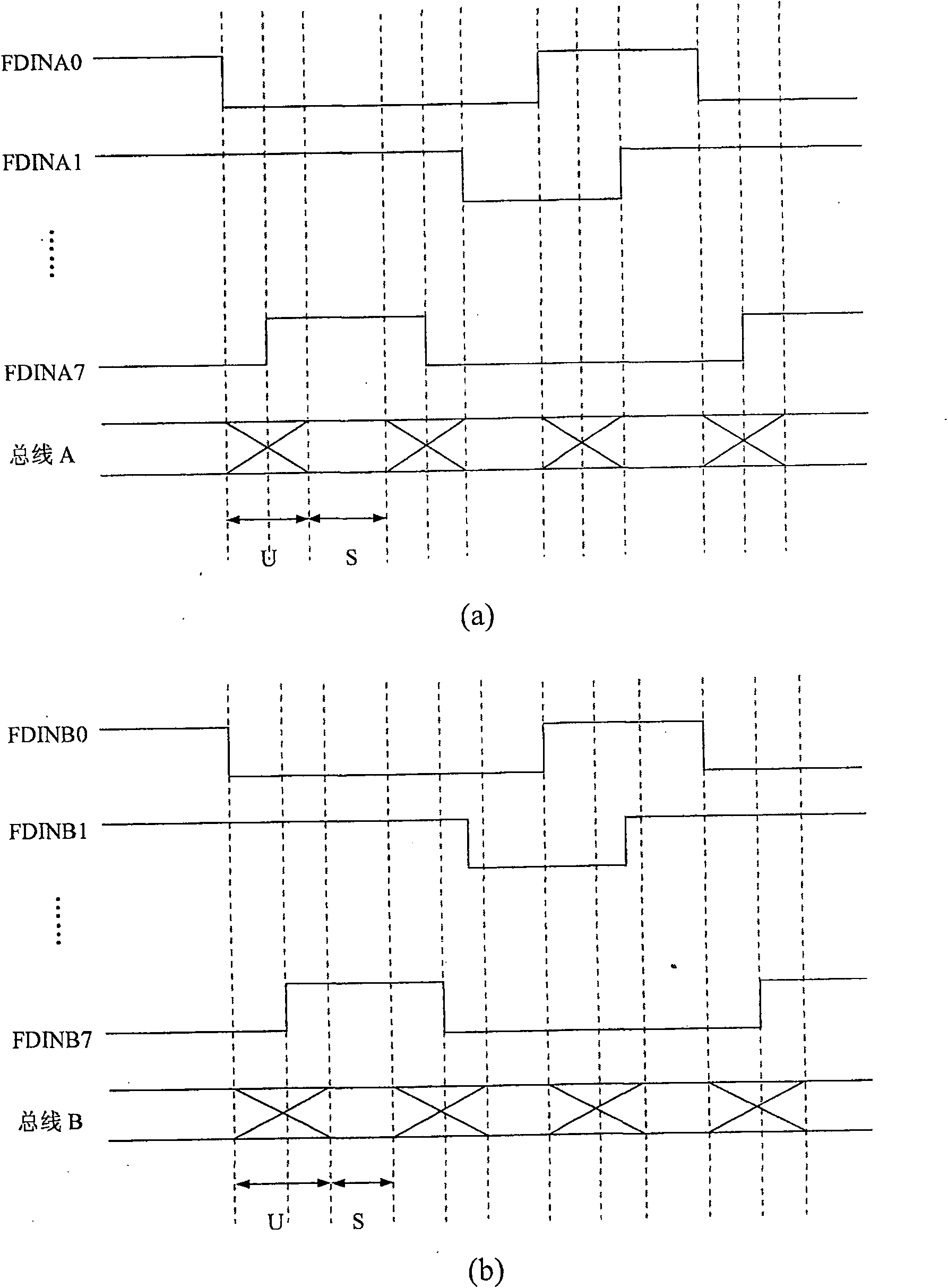

[0020] The design idea of the present invention is to add two sets of sending and receiving triggers on the backplane side of the hardware board, and these two sets of triggers will cut the time delay from the sending end to the receiving end, so that the time delay will not accumulate, and the system timing During the design, we only need to pay attention to the reliability of the transceiver trigger and the delay of the backplane, and the delay coordination of the own devices on the hardware board is controlled by the hardware board. By adopting this design method, the data delay fluctuation range from the sending end to the receiving end can be reduced, and the system synchronization design becomes easy to realize, thus providing a simple structure, easy to implement, Effective backplane interface with low cost and guaranteed data transmission quality, see below Figure 4 B...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More