Level shifter

A mover and level technology, applied in the field of microelectronics, can solve the problems of slow processing speed and high power consumption, and achieve the effect of increasing processing speed, reducing power consumption, and increasing conversion speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

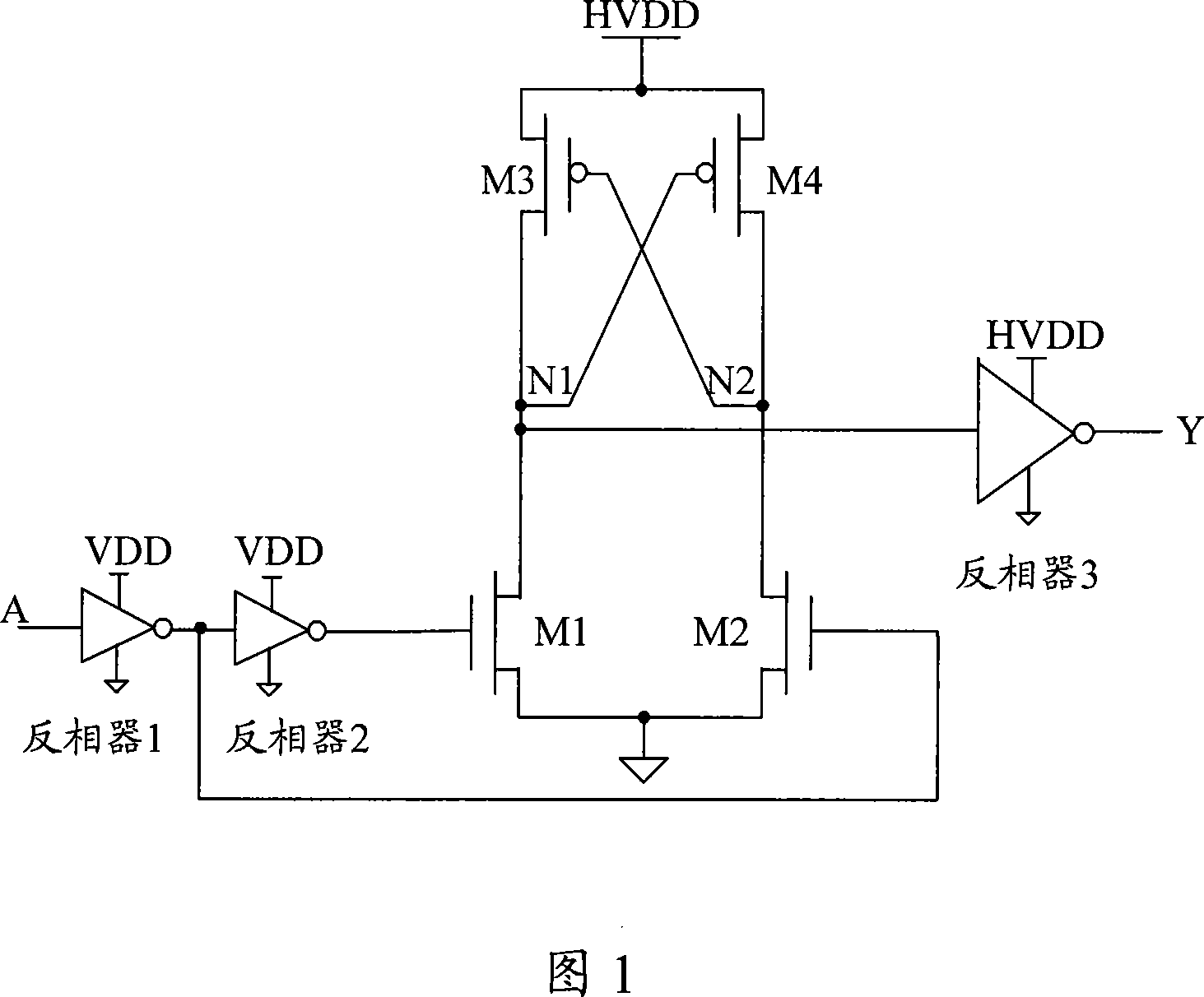

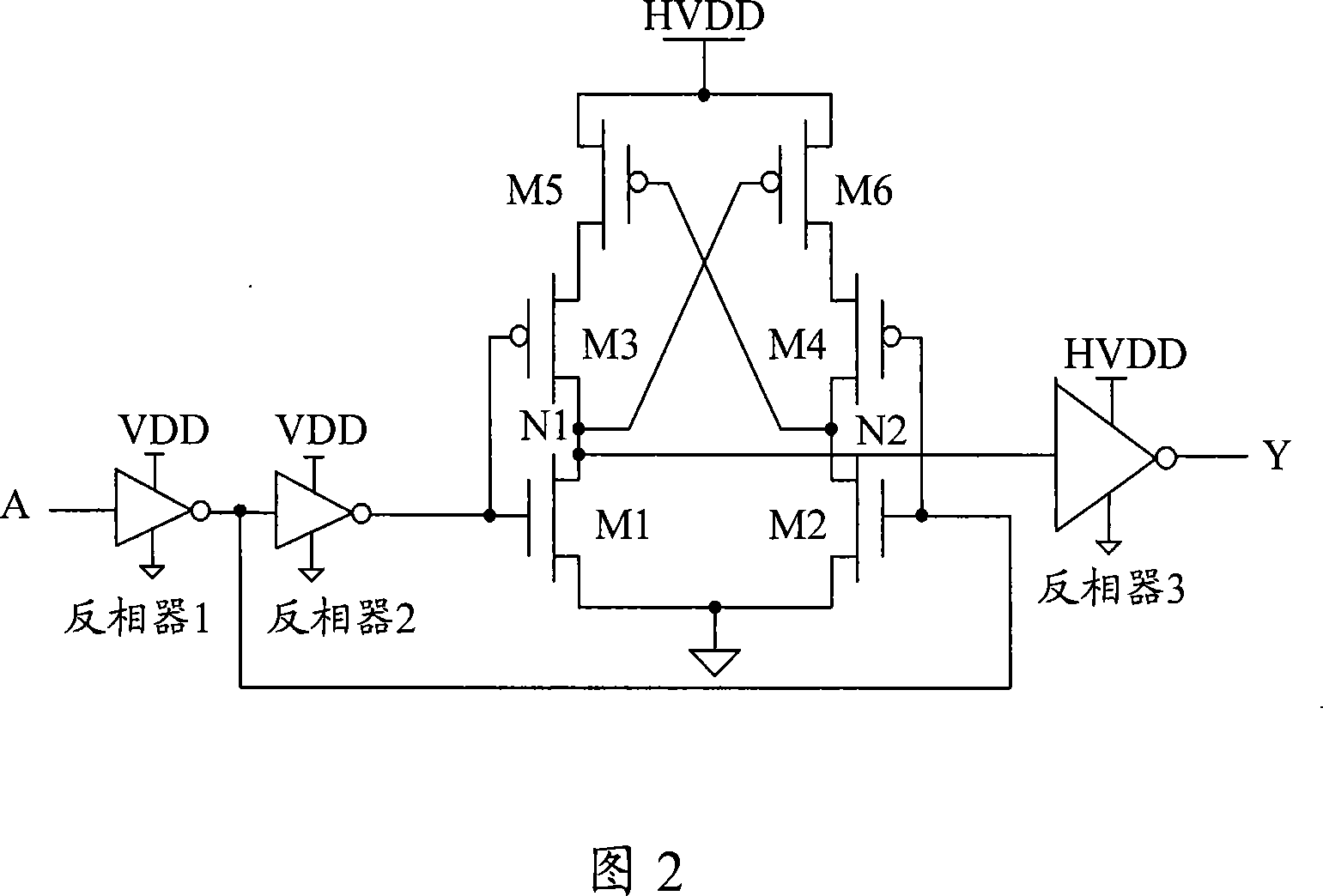

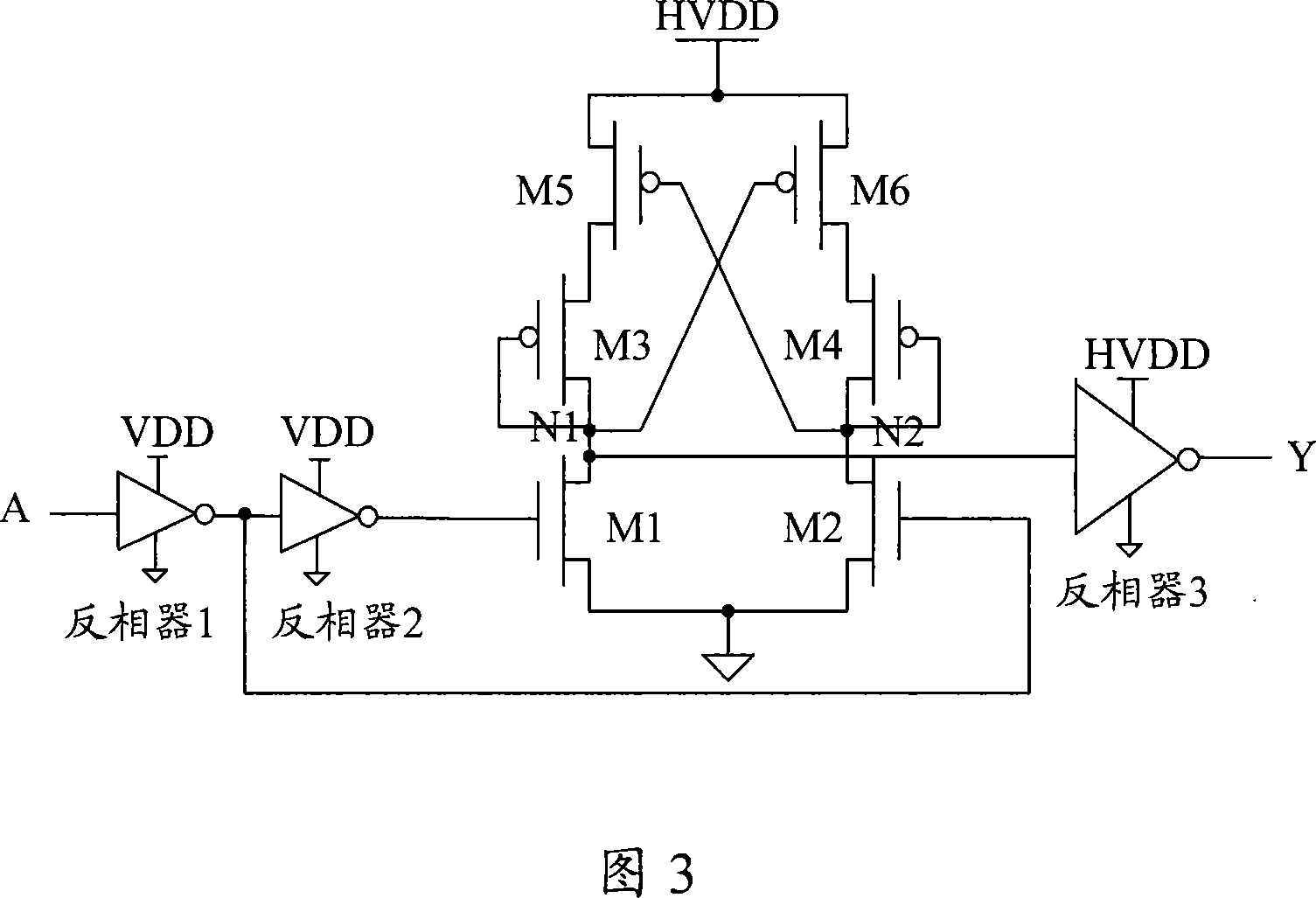

[0025] In order to solve the problems of slow processing speed and high power consumption during conversion in the level shifter in the prior art, in the embodiment of the present invention, in the two groups of circuits of the level shifter, the current limiting circuit in each group of circuits is The gate of the MOS transistor is connected to the drain to realize a high-speed, low-power level shifter.

[0026] The level shifter in the embodiment of the present invention includes first and second groups of circuits; wherein, each group of circuits includes a switch circuit and two MOS transistors;

[0027] In each group of circuits, the gate of the first MOS transistor is connected to the drain, and the source is connected to the drain of the second MOS transistor; the source of the second MOS transistor is connected to the second power supply; the second MOS transistor in each group of circuits The gate of the gate is connected to the drain of the first MOS transistor in an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More