Lead frame chip-level encapsulation method

A chip-level packaging and lead frame technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., to achieve the effect of low height, high stability and good heat dissipation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

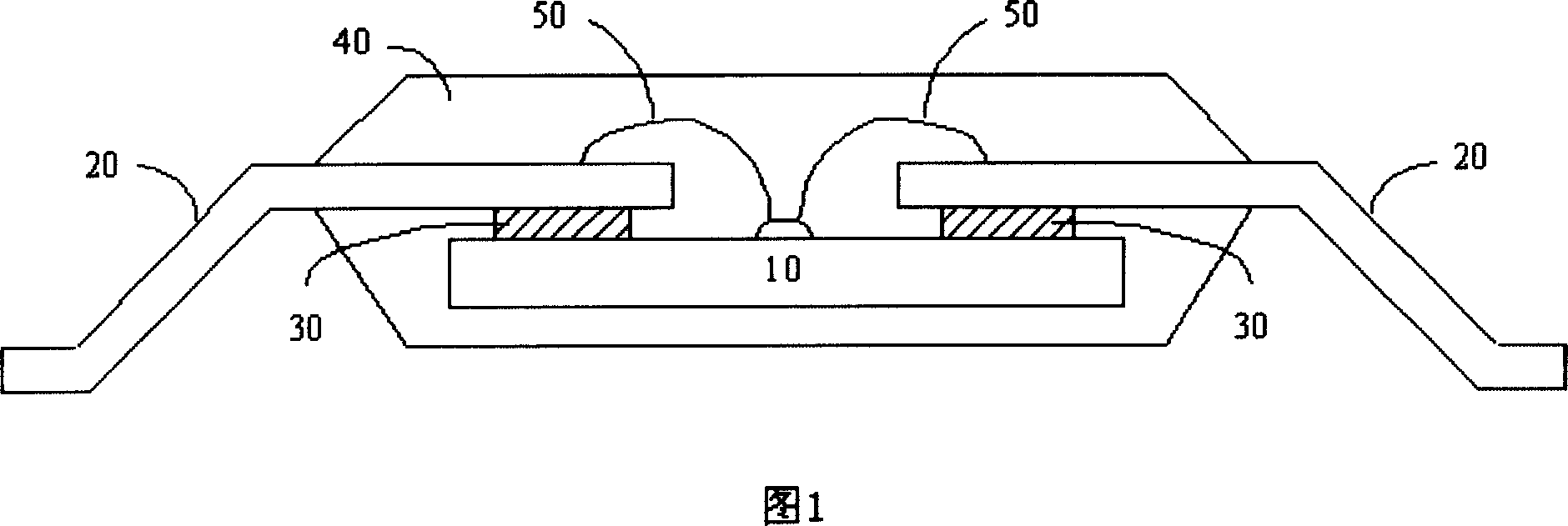

[0021] The invention provides a lead frame type chip level packaging method. This method is roughly similar to the traditional LOC process, but there are significant differences in some steps. Hereinafter, this specification will mainly describe the differences, and the same parts as those in the prior art will not be repeated.

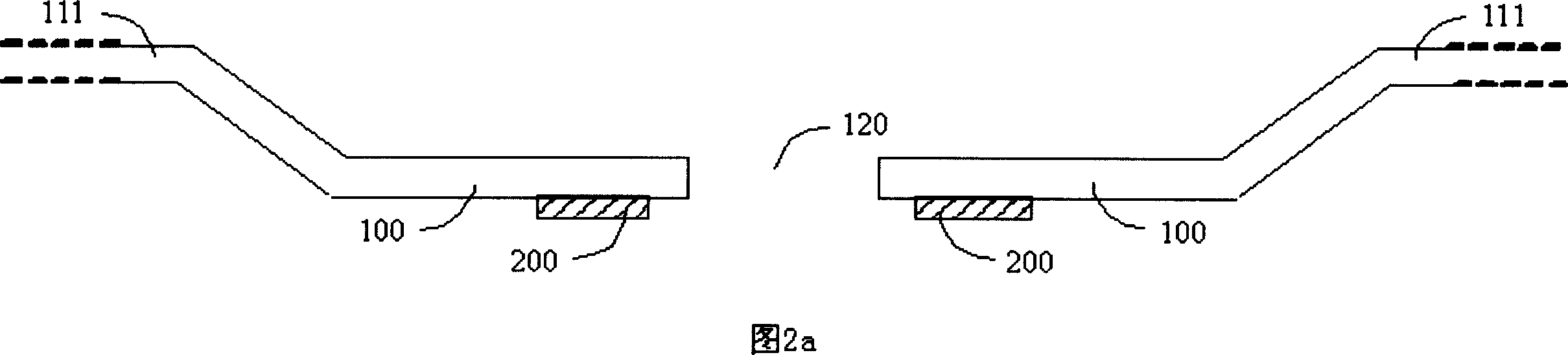

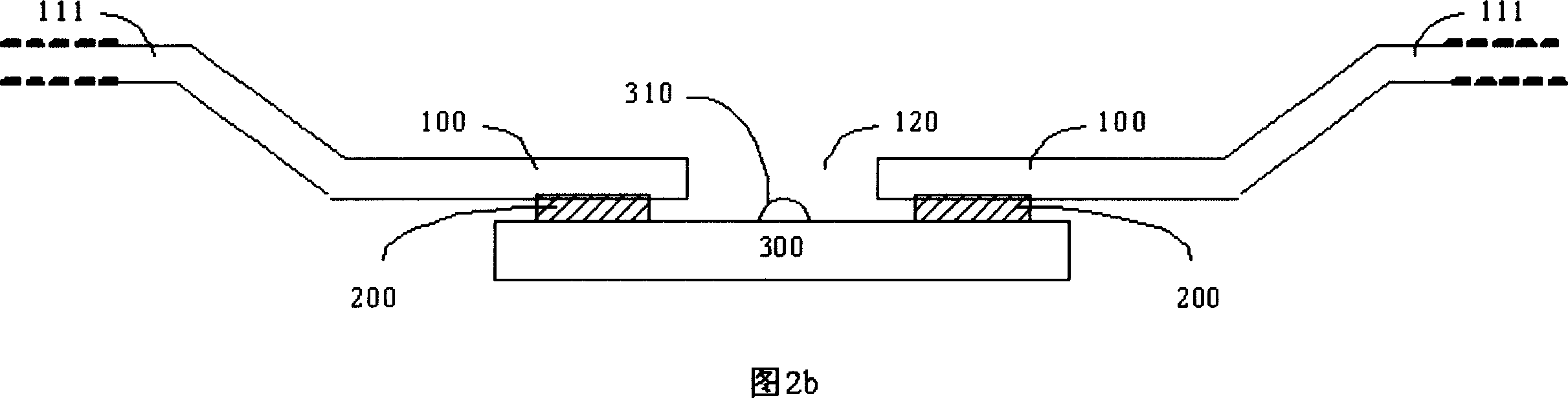

[0022] In the first step of the method, a suitable lead frame 100 is provided as shown in Figure 2a. This lead frame can be customized according to different applications after packaging. It is characterized in that the multiple pins (including internal pins 110 and external pins 111 ) of the lead frame 100 are at least located on opposite sides, and the lead frame 100 is located on the other side. Appropriate openings 120 are left at appropriate distances around. Chips to which the present invention is applicable have bond pads located at appropriate positions on the front side. The opening 120 is mainly to expose the soldering pads for wire bondi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More