Symmetrical multiple processor blade server

A symmetric multi-processor and blade server technology, applied in the field of blade servers, can solve the problems of insufficient number of server CPUs and inability to meet application requirements, and achieve the effects of convenient expansion, low price, and increased computing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

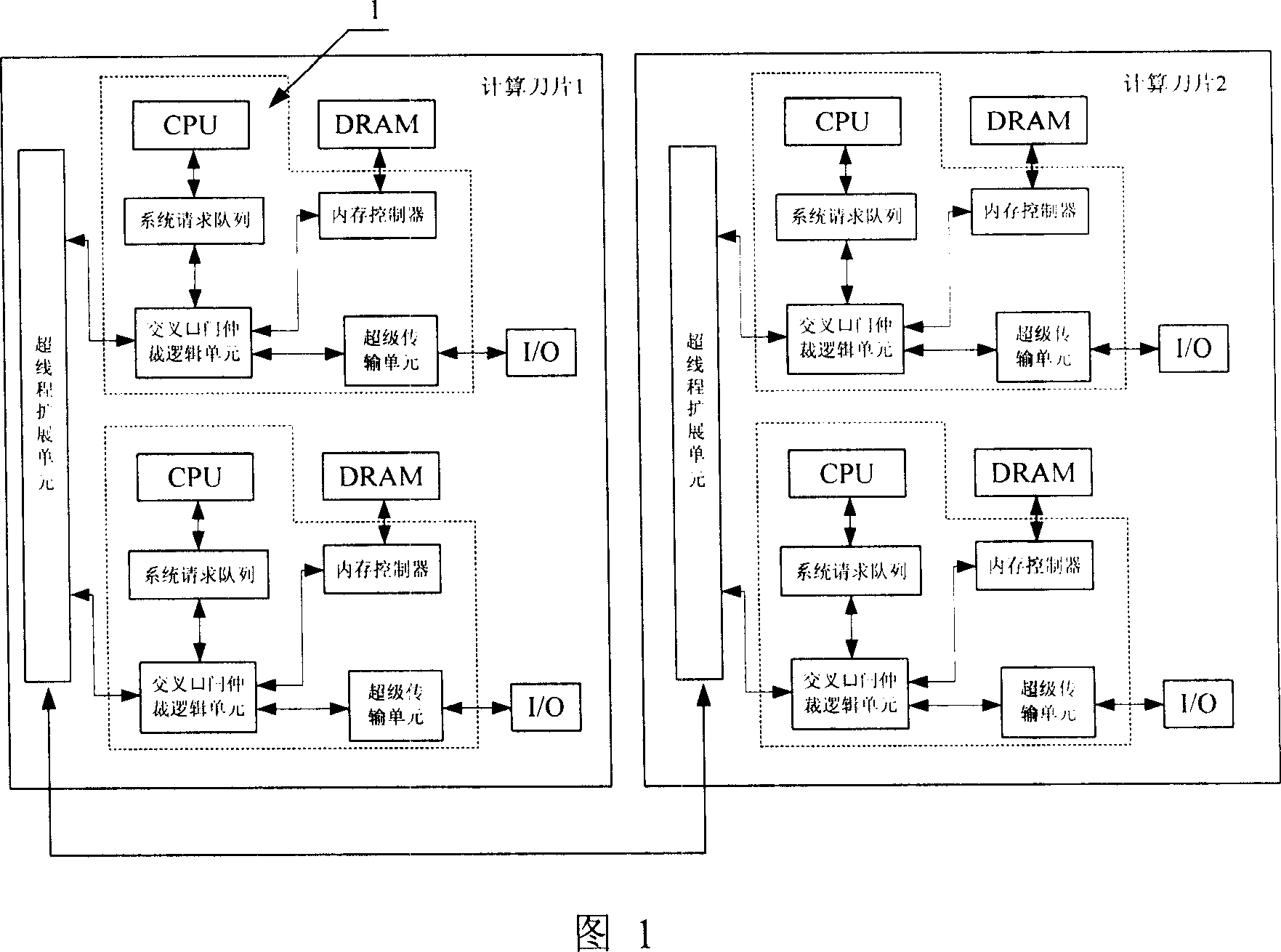

[0018] An embodiment of the present invention, as shown in Figure 1, includes two computing blades, two CPU chipsets 1 are arranged on each computing blade, a hyper-threading extension unit is arranged on each computing blade, each computing The CPU chipsets on the blades and the CPU chipsets of different computing blades are connected to each other through hyper-thread extension units.

[0019] In this embodiment, the CPU chipset and the hyper-thread extension unit adopt the Intel Xeon product EM64T, and the specified instructions in the blade server memory are extracted by the CPU chipset, and the CPU chipset interacts with other components in the blade server through the hyper-thread extension unit. The CPU chipset communicates and arbitrates, selects the CPU chipset that executes the specified instruction, and transmits the specified instruction to the selected CPU chipset through the hyper-thread extension unit, and the selected CPU chipset executes the specified instructi...

Embodiment 2

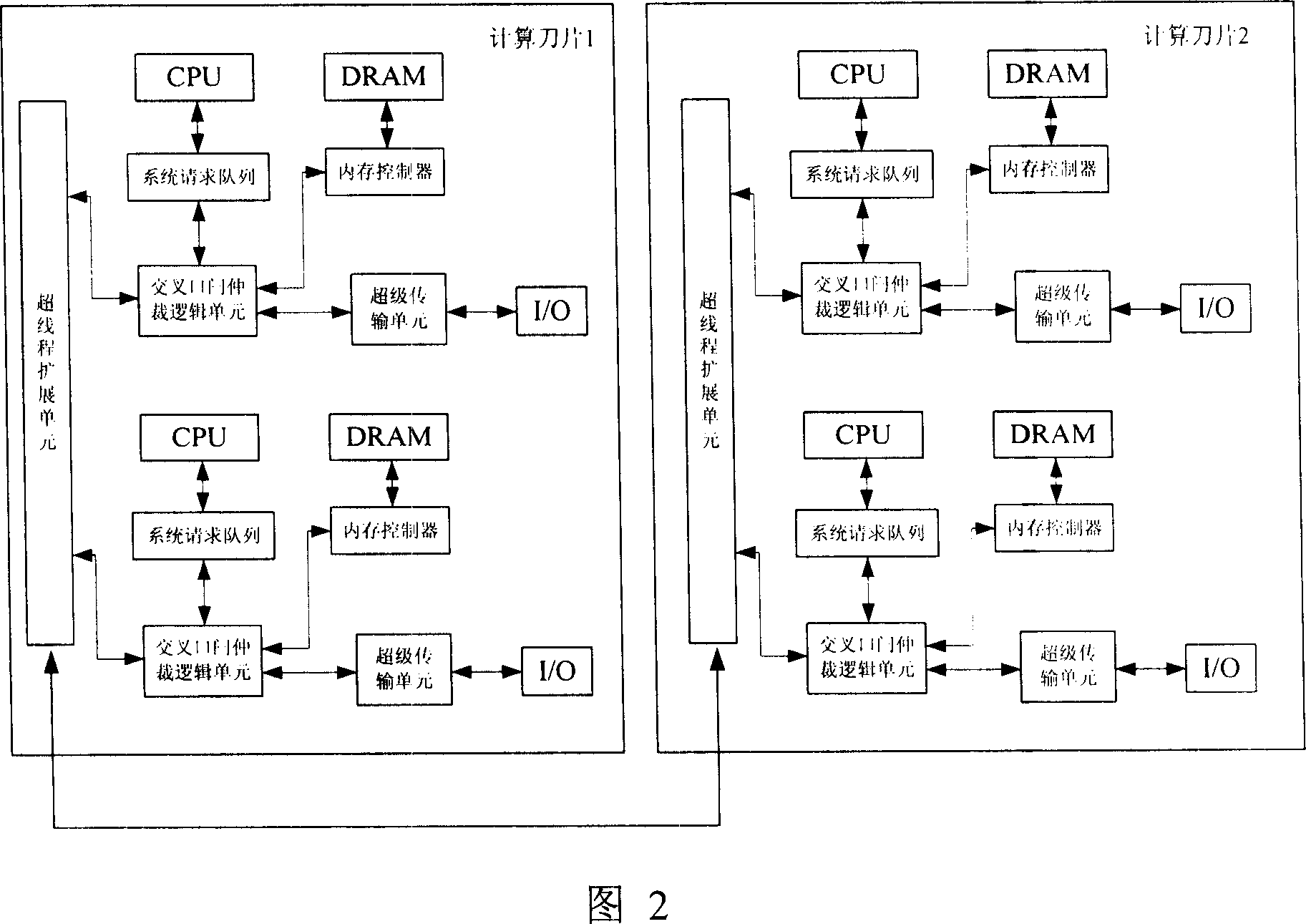

[0021] A preferred embodiment of the present invention, as shown in Figure 2, includes two computing blades, and two CPU chipsets are arranged on each computing blade, and the CPU chipset includes a CPU chip, a system request queue, and an intersection latch. Arbitration logic unit, the CPU chip is bidirectionally connected to the system request queue, the arbitration logic unit is bidirectionally connected to the system request queue, and the hyperthread extension unit is bidirectionally connected to the intersection latch arbitration logic unit.

[0022] In this embodiment, the CPU chipset and the hyper-thread extension unit adopt AMD Opteron product AMD64, and the specified instructions in the blade server memory are extracted by the CPU chipset through the memory controller, and the CPU chipset is connected to the blade through the hyper-thread extension unit. Other CPU chipsets in the server communicate and arbitrate, select the CPU chipset that executes the specified inst...

Embodiment 3

[0024] Another preferred embodiment of the present invention, as shown in Figure 2, includes two computing blades, and two CPU chipsets are set on each computing blade, and the CPU chipset includes a CPU chip, a system request queue, an intersection A latch arbitration logic unit, a super transfer unit and a memory controller, the CPU chip is bidirectionally connected to the system request queue, the arbitration logic unit is bidirectionally connected to the system request queue, and the hyperthreading extension unit is bidirectionally connected to the intersection latch arbitration logic unit connected, the super transfer unit and the memory controller are bidirectionally connected to the intersection latch arbitration logic unit respectively.

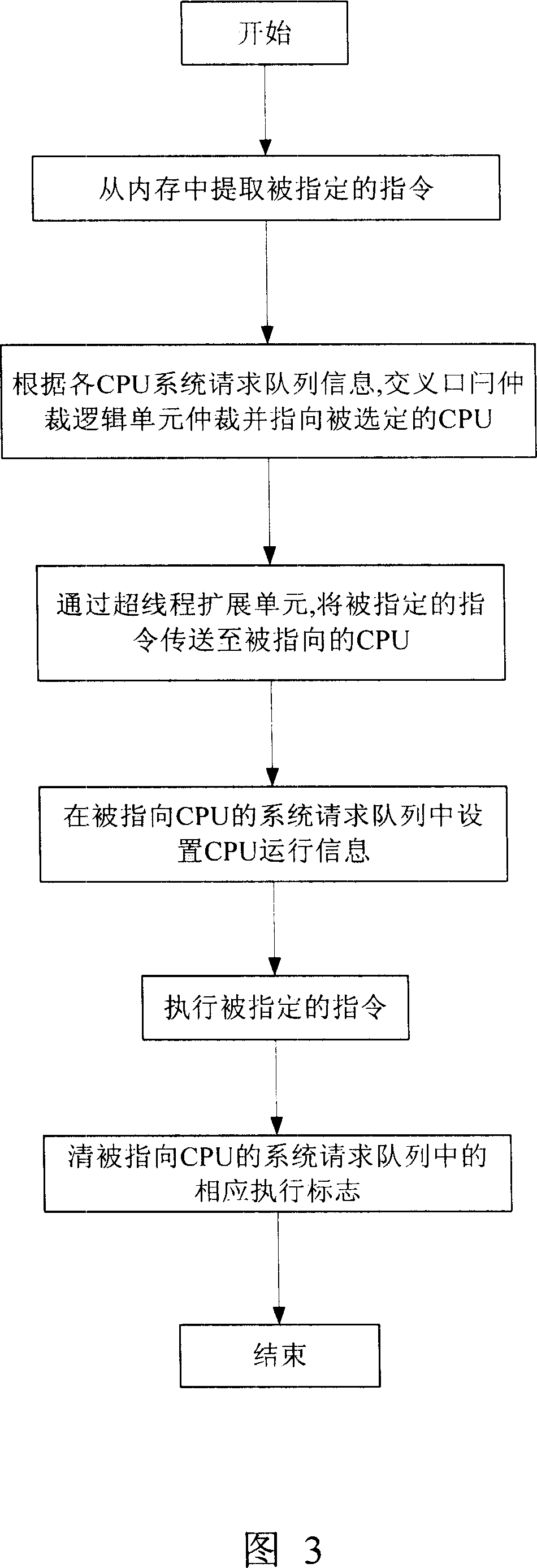

[0025] In this embodiment, the CPU chipset and hyper-threading expansion unit adopt AMD Opteron product AMD64, as shown in Figure 3, the specified instruction in the blade server memory is extracted by the CPU chip through the memory c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More