Layout structure of non-volatile memory

A non-volatile, layout structure technology, applied in information storage, static memory, read-only memory, etc., can solve the problems of short circuit, affecting the reliability of the process yield, poor process yield and reliability, etc., to save the process cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to make the above and other objects, features and advantages of the present invention more comprehensible, preferred embodiments are described below in detail with accompanying drawings.

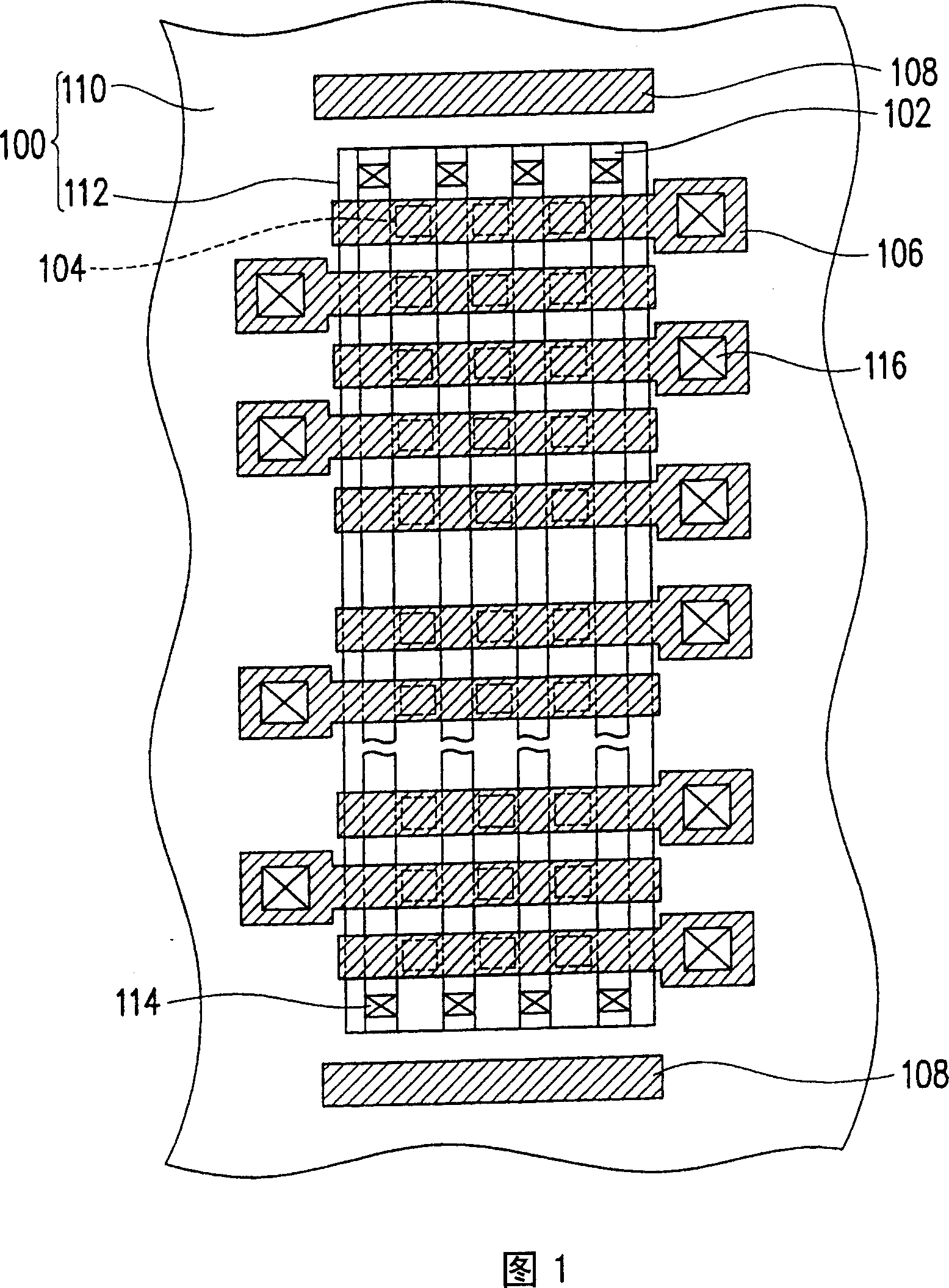

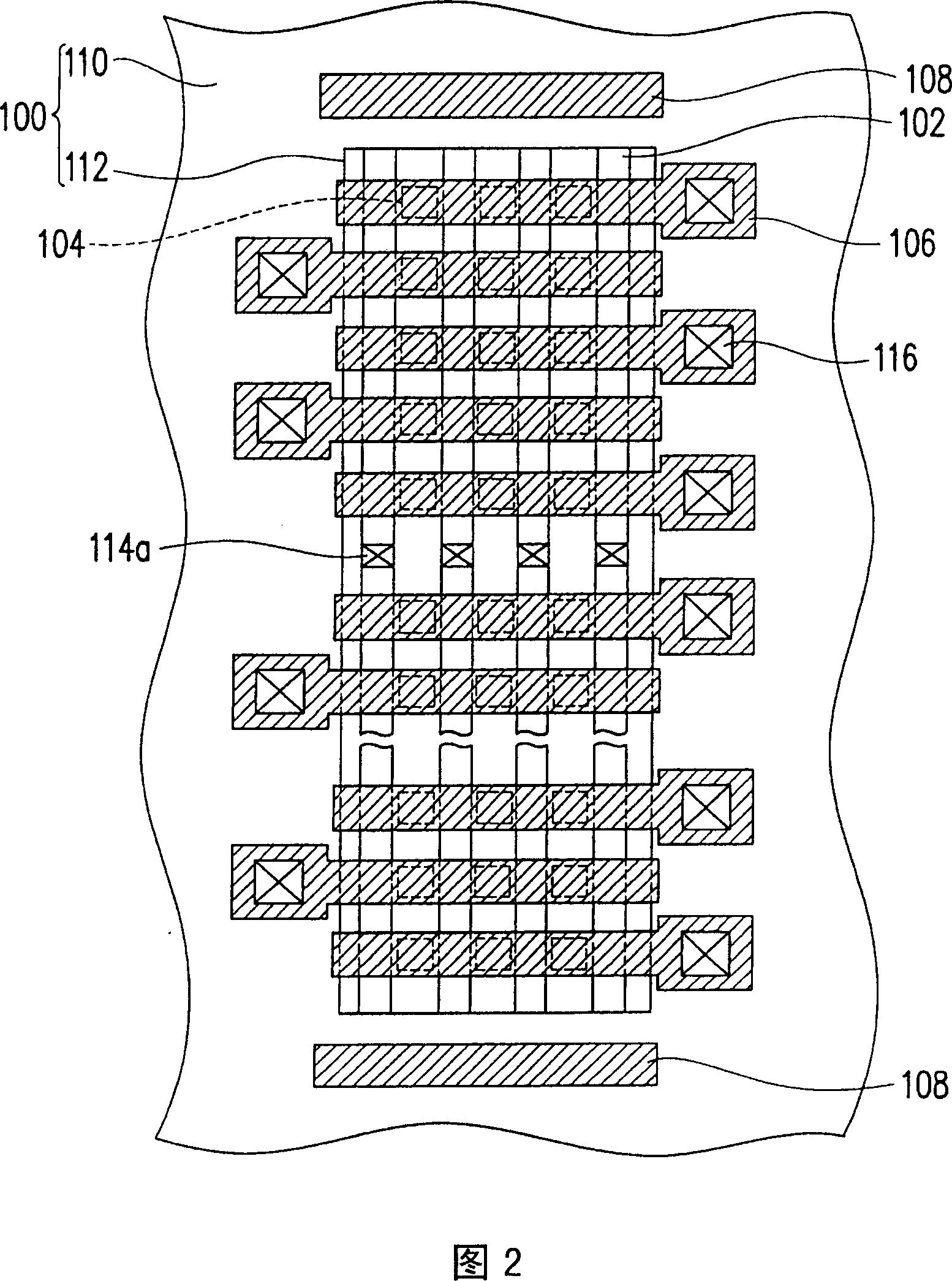

[0041] FIG. 1 is a top view of a layout structure of a non-volatile memory according to an embodiment of the present invention. There are 3 memory cells in each memory cell column in FIG. 1 , but the present invention is not limited thereto.

[0042] Please refer to FIG. 1, the layout structure of the non-volatile memory of the present embodiment mainly includes: a substrate 100, a plurality of buried bit lines (buried bit lines) 102 in the row direction, a plurality of transistors 104 as memory cells, and columns A plurality of word lines (word lines) 106 and dummy word lines (dummy word lines) 108 in the direction. Wherein, the row direction is generally perpendicular to the column direction. An isolation structure 110 is disposed in the substrate 100 to define an active ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More