An encapsulated chip and its encapsulation method for chip

A technology for packaging devices and chips, which is applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve problems such as time-consuming, unfavorable FPGA modular design, inconvenience, etc., to facilitate testing and debugging, and realize The effect of visibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

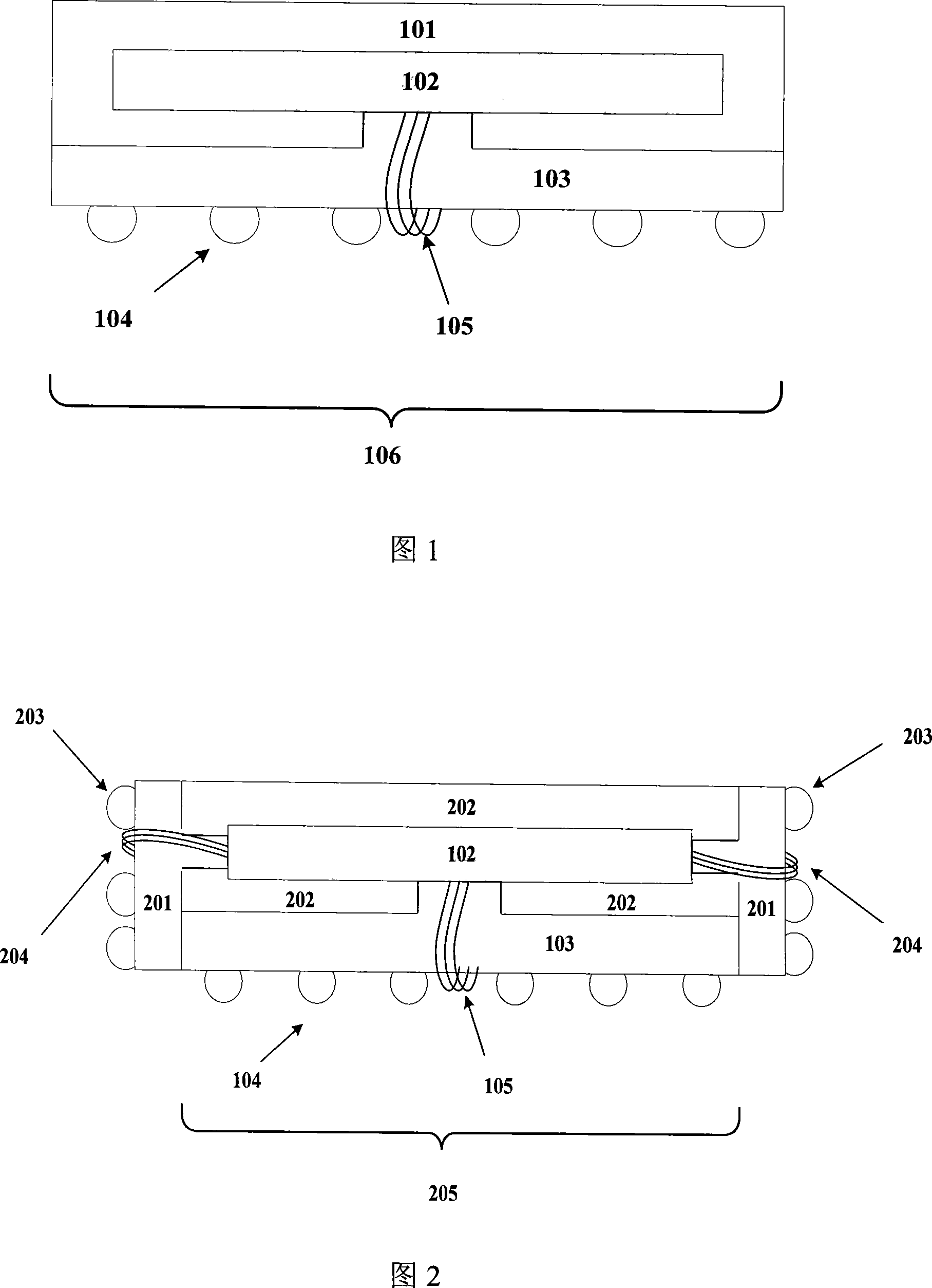

[0032] The present invention will be further described below in conjunction with the accompanying drawings and preferred embodiments.

[0033] The main idea of the present invention is: when the chip is packaged, the same signal pin is simultaneously led to the lower surface and the side surface of the chip for physical packaging. In this way, when using the packaged chip after packaging, if the packaged chip is soldered on the PCB (printed circuit board) to be used, the chip pins on the bottom of the soldered chip are invisible to the user. When debugging and testing the packaged chip, when the signal pin needs to be measured, it only needs to measure the exposed signal pin on the side of the chip.

[0034] Still taking BGA packaging as an example, Fig. 2 shows a BGA packaging method of a chip realized in the present invention: the packaged chip 205 includes: chip 102, substrate 103, lower surface solder ball 104, wire bridge 105, test Substrate 201, mold cap 202, side sol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com