Method for manufacturing single level polysilicon electric removal and programmable read only memory cell

A single-layer polysilicon, read-only storage technology, applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as difficulties, multiple photomasks, and complicated process steps, so as to reduce the difficulty of integration and reduce the initial cost. voltage and erase voltage, effect of wide voltage operating range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

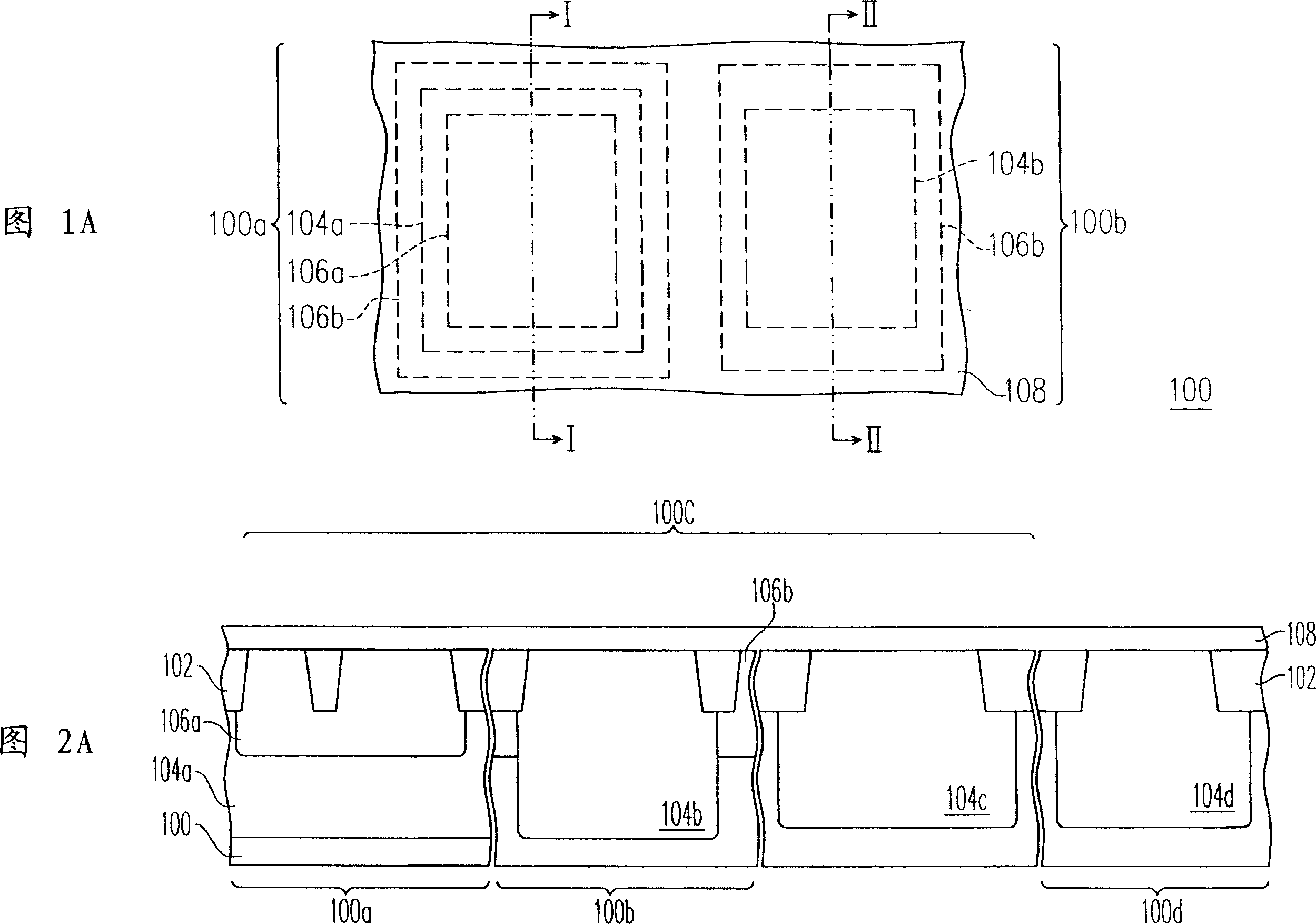

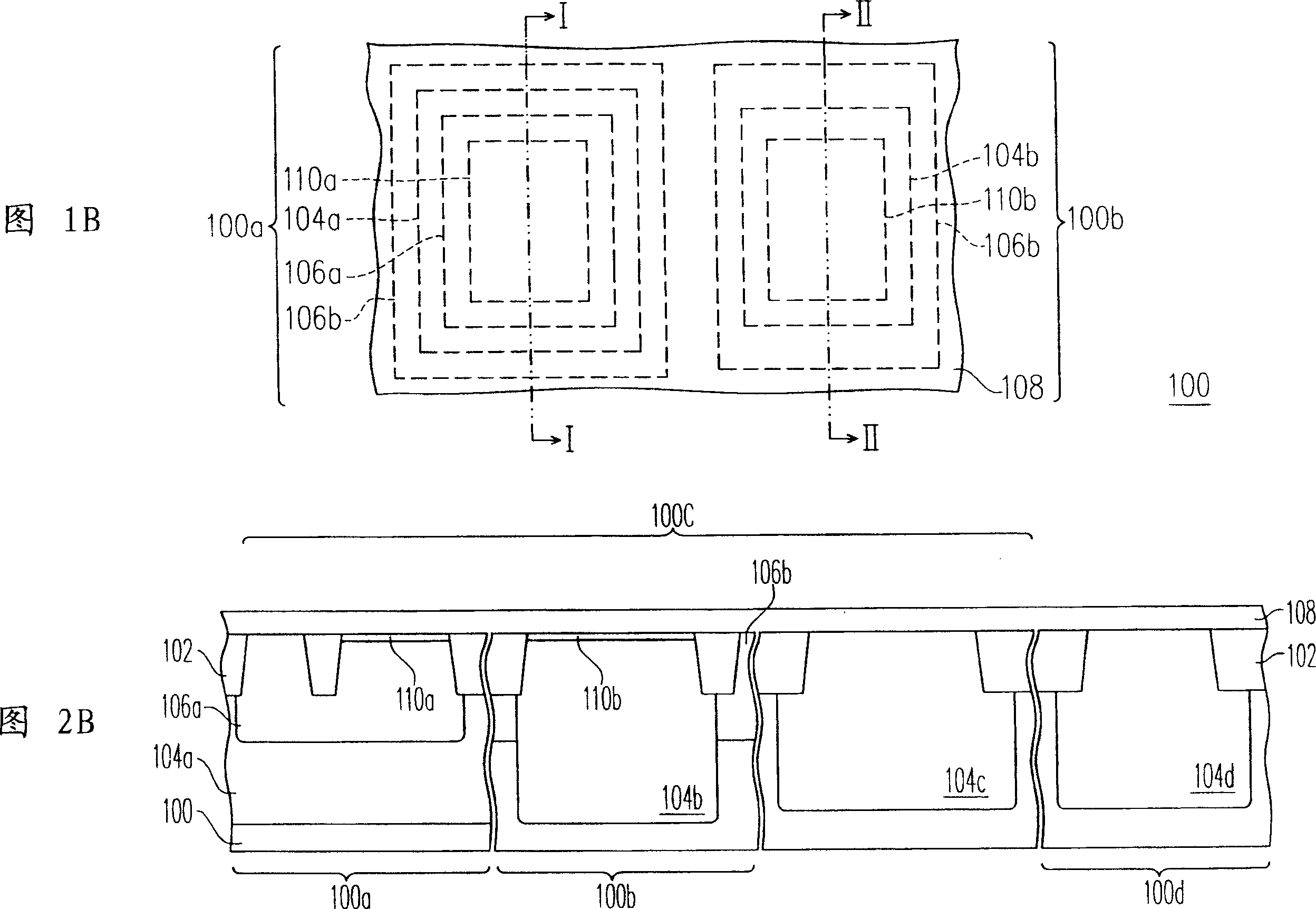

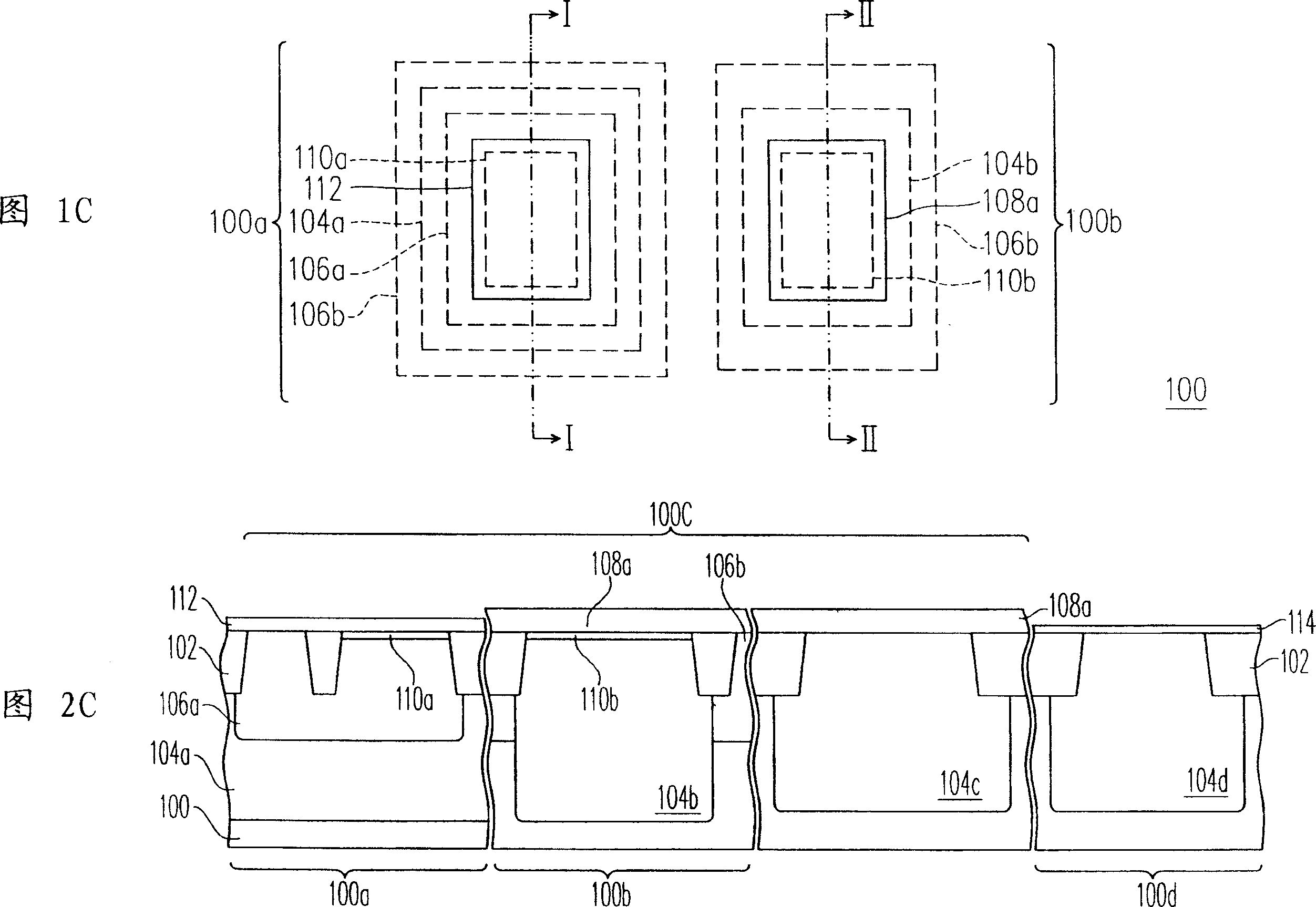

[0061] 1A to FIG. 1D are schematic top views of a method for forming a depleted single-layer polysilicon electrically erasable programmable read-only memory cell according to a preferred embodiment of the present invention. 2A to 2D are schematic cross-sectional views of FIGS. 1A to 1D along line I-I and line II-II, respectively.

[0062] Referring to FIG. 1A and FIG. 2A, a substrate 100 is provided, wherein the substrate 100 has a floating region 100a and a control region 100b. It should be noted that both the floating region 100 a and the control region 100 b are located in a high voltage device region 100 c of the substrate 100 . In addition, the substrate 100 includes a low-voltage device region 100d in addition to the high-voltage device region 100c. Moreover, each device region in the substrate 100 is isolated from each other by an isolation structure 102 . The isolation structure 102 is, for example, a shallow trench isolation structure.

[0063] After that, an isola...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More