Preparation method of silicon transistor on source body Ohm contacting isolator

A silicon-on-insulator and ohmic contact technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of reducing circuit speed and increasing circuit dynamic power consumption, so as to reduce dynamic power consumption and reduce leakage-induced potential Barrier lowering effect, effect of improving breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the objectives, technical solutions, and advantages of the present invention clearer, the following further describes the present invention in detail in conjunction with specific embodiments and with reference to the accompanying drawings.

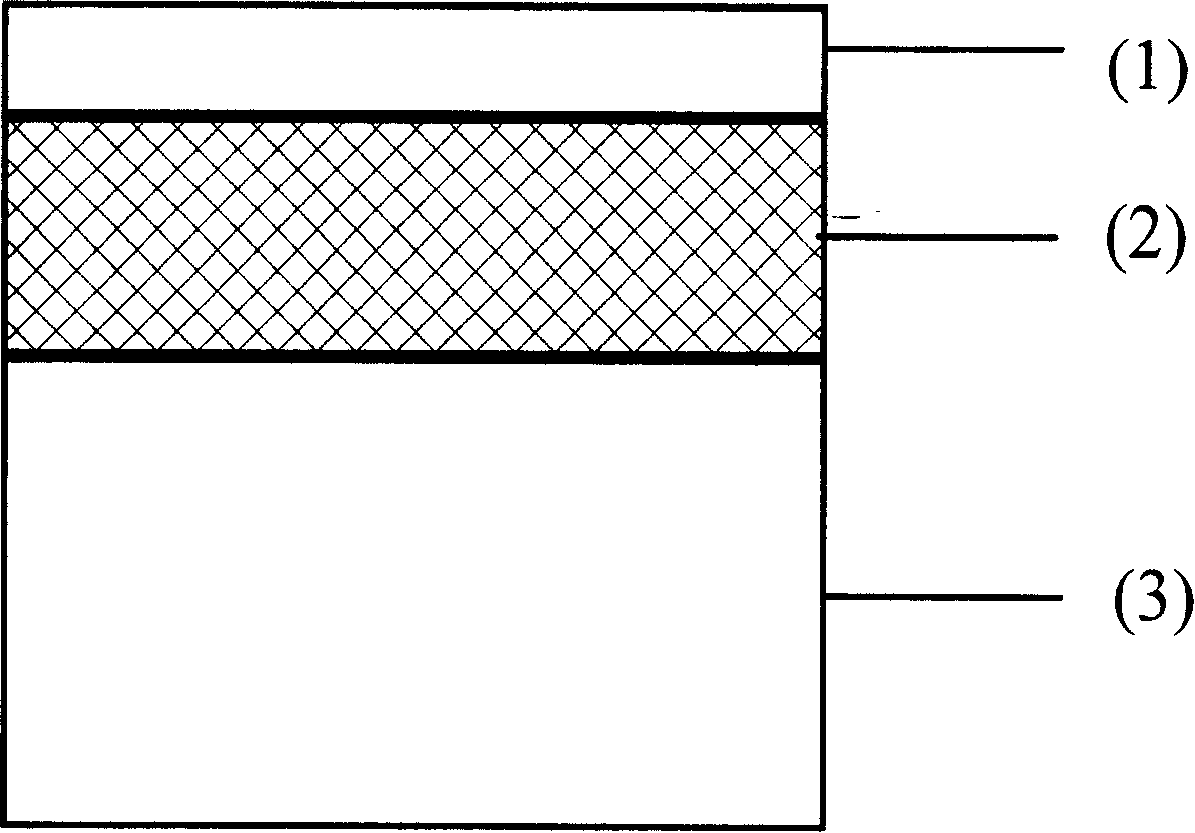

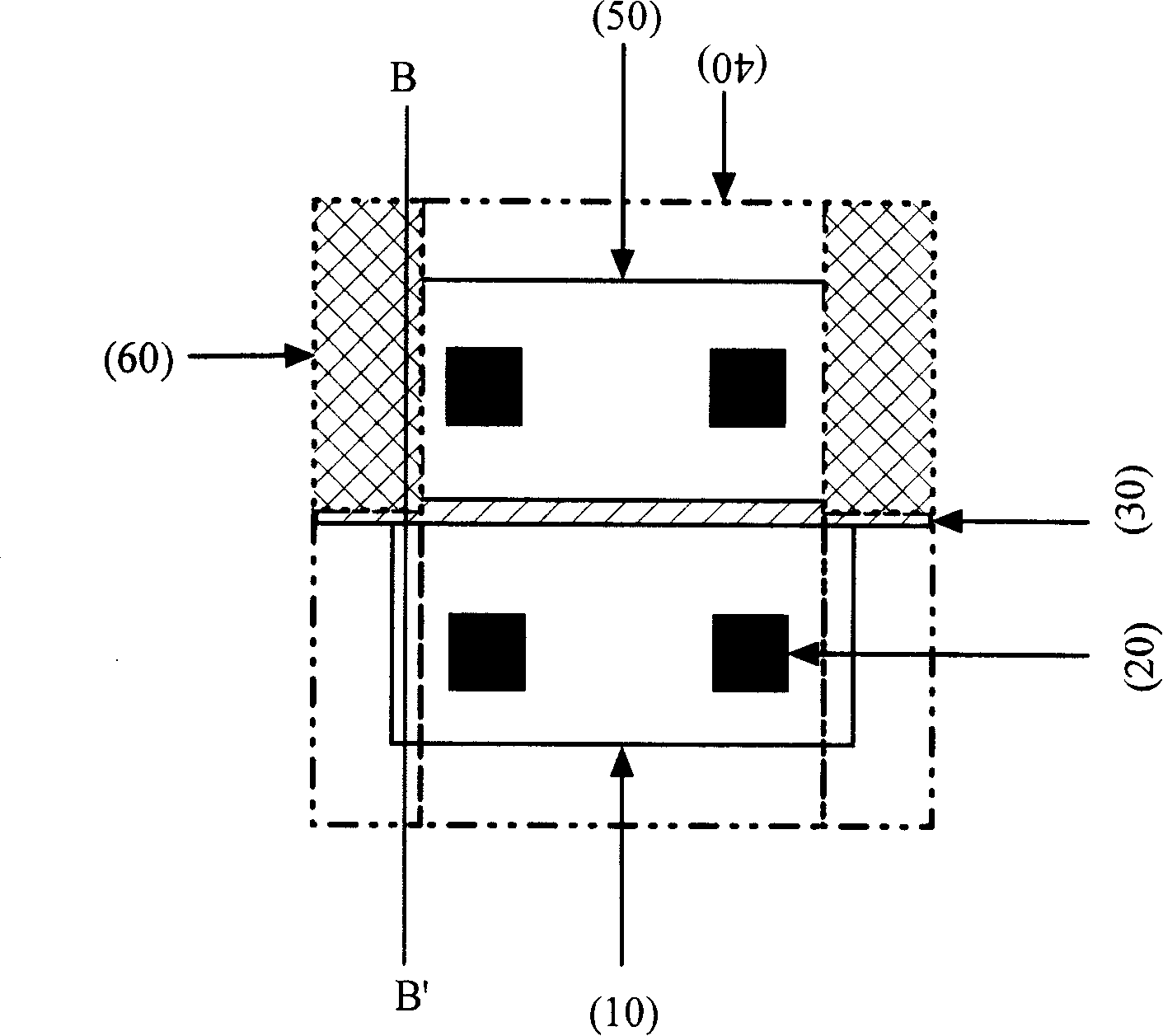

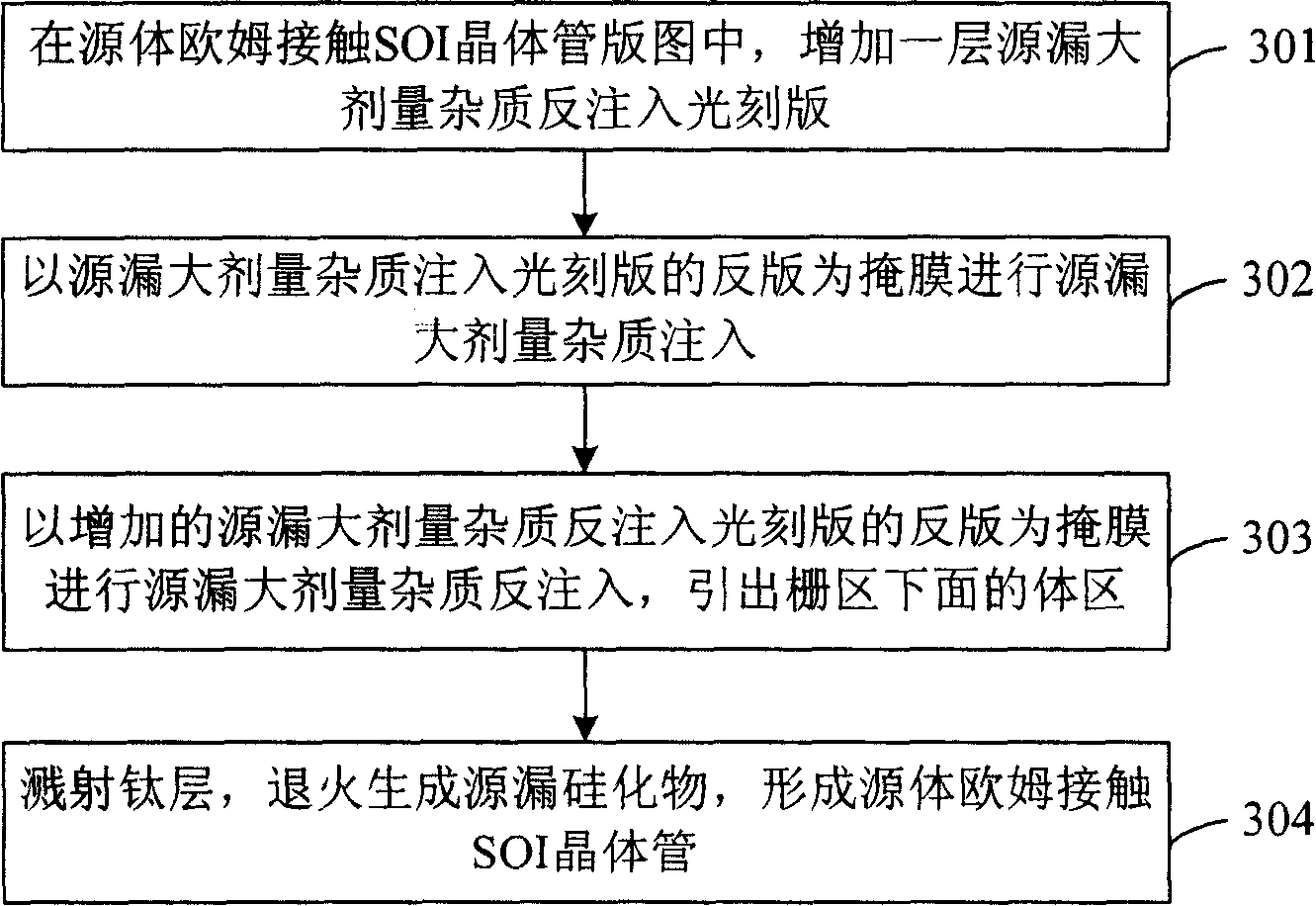

[0034] The working principle of the source-body ohmic contact SOI transistor of the present invention is that a layer of source-drain high-dose impurity back-injection photolithography plate 60 is added to the source-body ohmic contact SOI transistor layout; the photolithography plate 40 is used as a mask. Source and drain high-dose impurity implantation; source and drain high-dose impurity back-implantation of the photolithography plate 60 as a mask for source-drain high-dose impurity back implantation to lead out the body region 54 under the gate; sputtering titanium layer, annealing The source and drain silicides fix the body region and the source region at the same potential, thus eliminating the floating body effec...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com