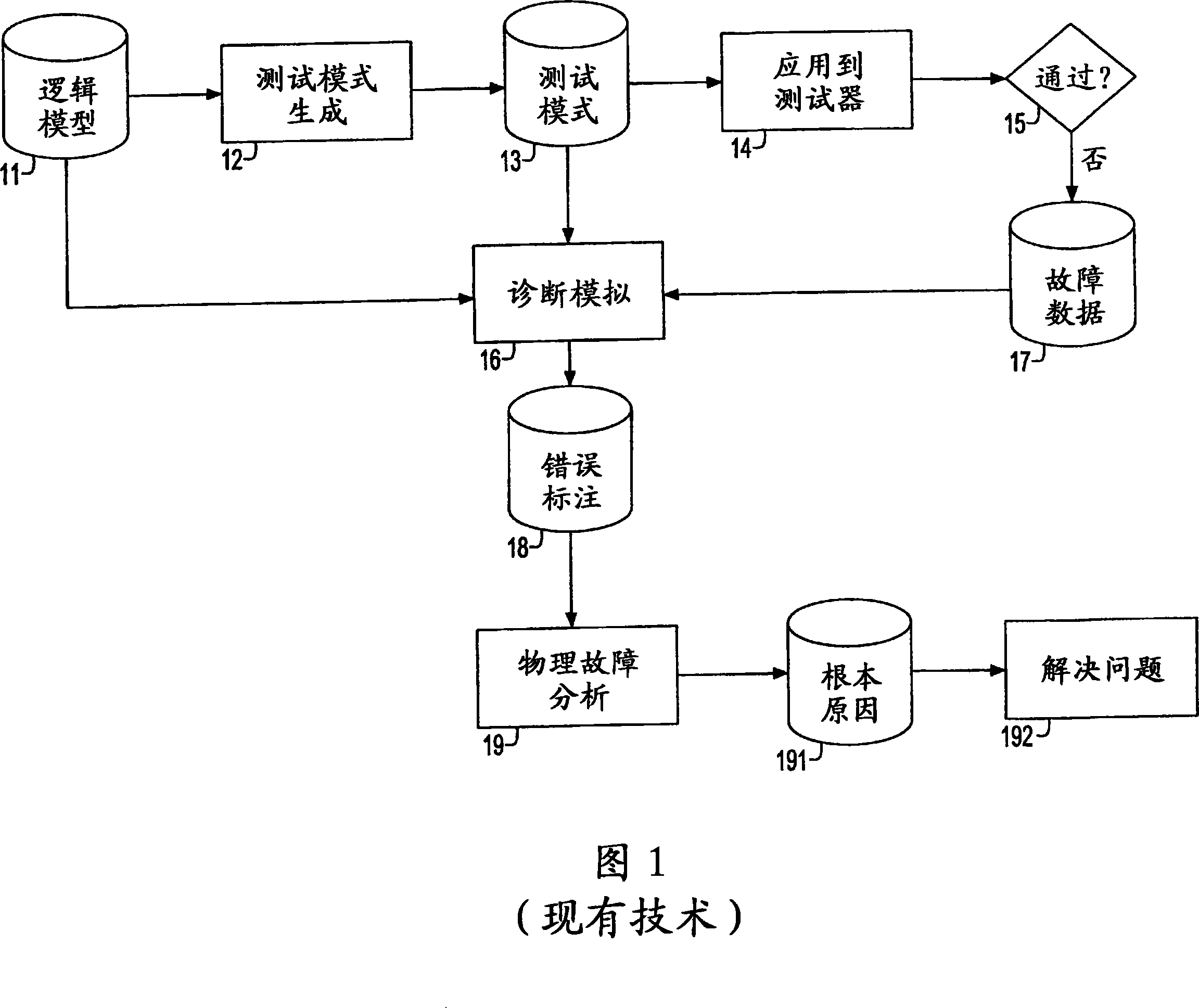

Iterative test generation and diagnostic method based on modeled and unmodeled faults

A modeling and error technology, applied in the direction of error detection/correction, electronic circuit testing, digital circuit testing, etc., can solve the problems that conventional technology is not enough to effectively deal with test problems, test time cannot be managed, etc., to improve tester time , Improve the effect of error resolution ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

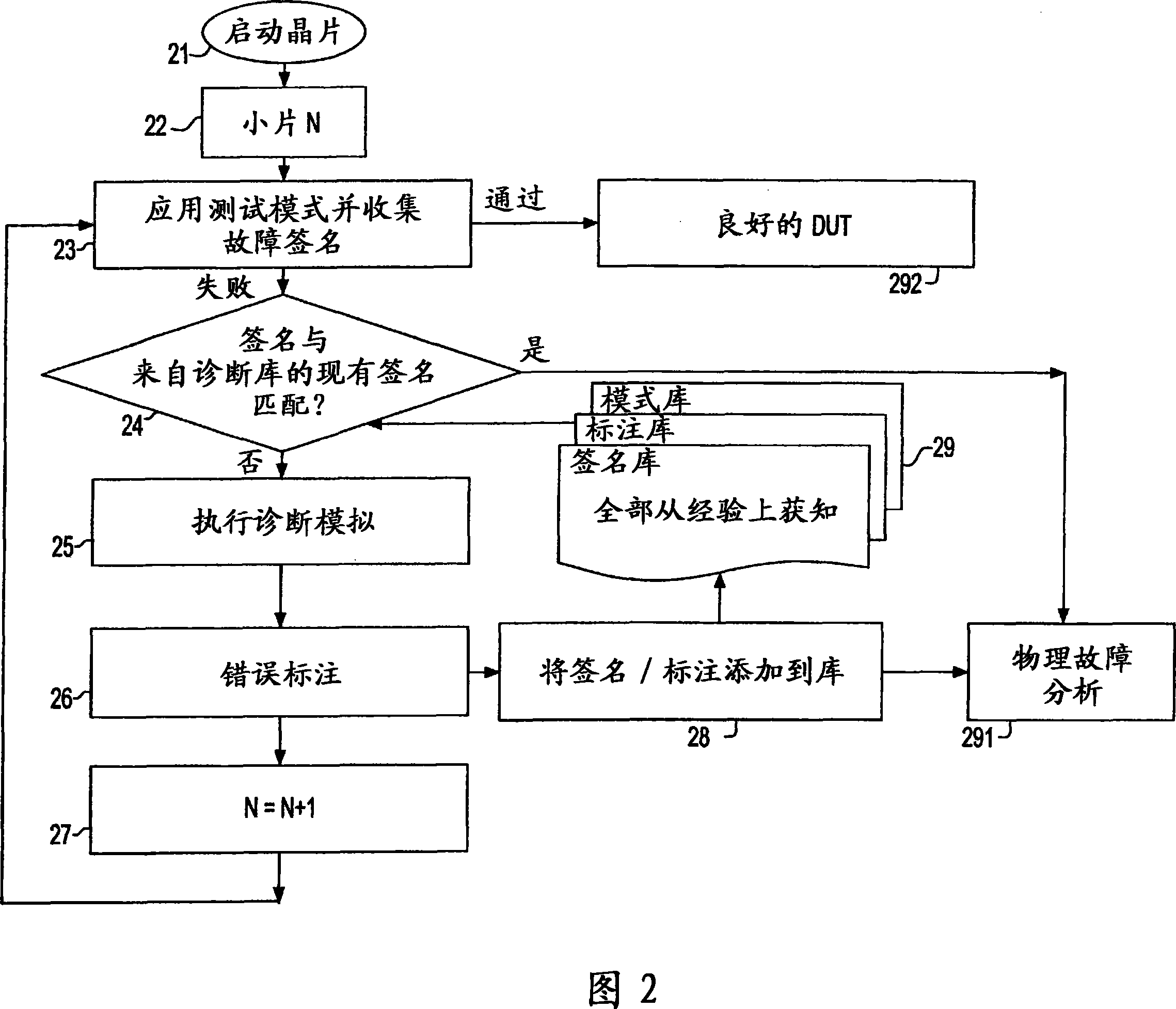

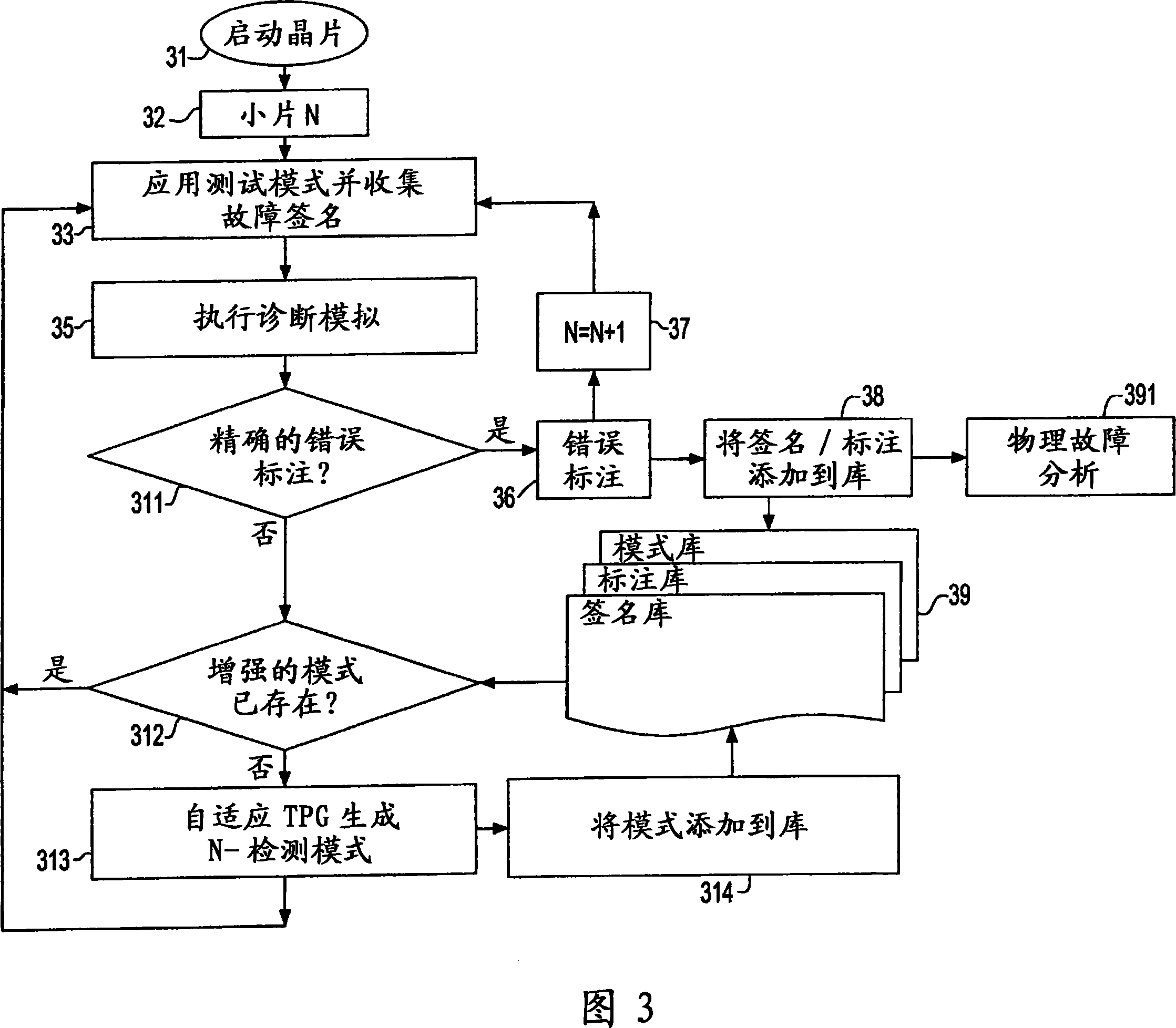

[0038] In the following, a preferred embodiment of the invention is described, showing several system components that are closely and interactively linked to the test pattern generation and tester execution process.

[0039] Referring to Figures 2-5, the flow and functional components of the iterative diagnosis process are shown. Test generation, error simulation, and diagnostic simulation blocks have inputs from logic design and error models. The test generation block provides a production test mode and a custom repeat diagnostic mode, labeled N-detection mode in the corresponding figure. Other specialized algorithms are also invoked to generate custom patterns, which are described below.

[0040] The diagnostic and test execution process is repeated calling the adaptive fault device specific iterative process multiple times until the desired diagnostic resolution is achieved.

[0041] The process steps preferably include:

[0042] 1. Use standard diagnostic techniques to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More