Wafer multi-test object parallel test system

A test system and test object technology, used in semiconductor/solid-state device testing/measurement, electronic circuit testing, single semiconductor device testing, etc., and can solve problems such as wafer fluctuation disturbance, unsolved wafer signal interference, distortion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

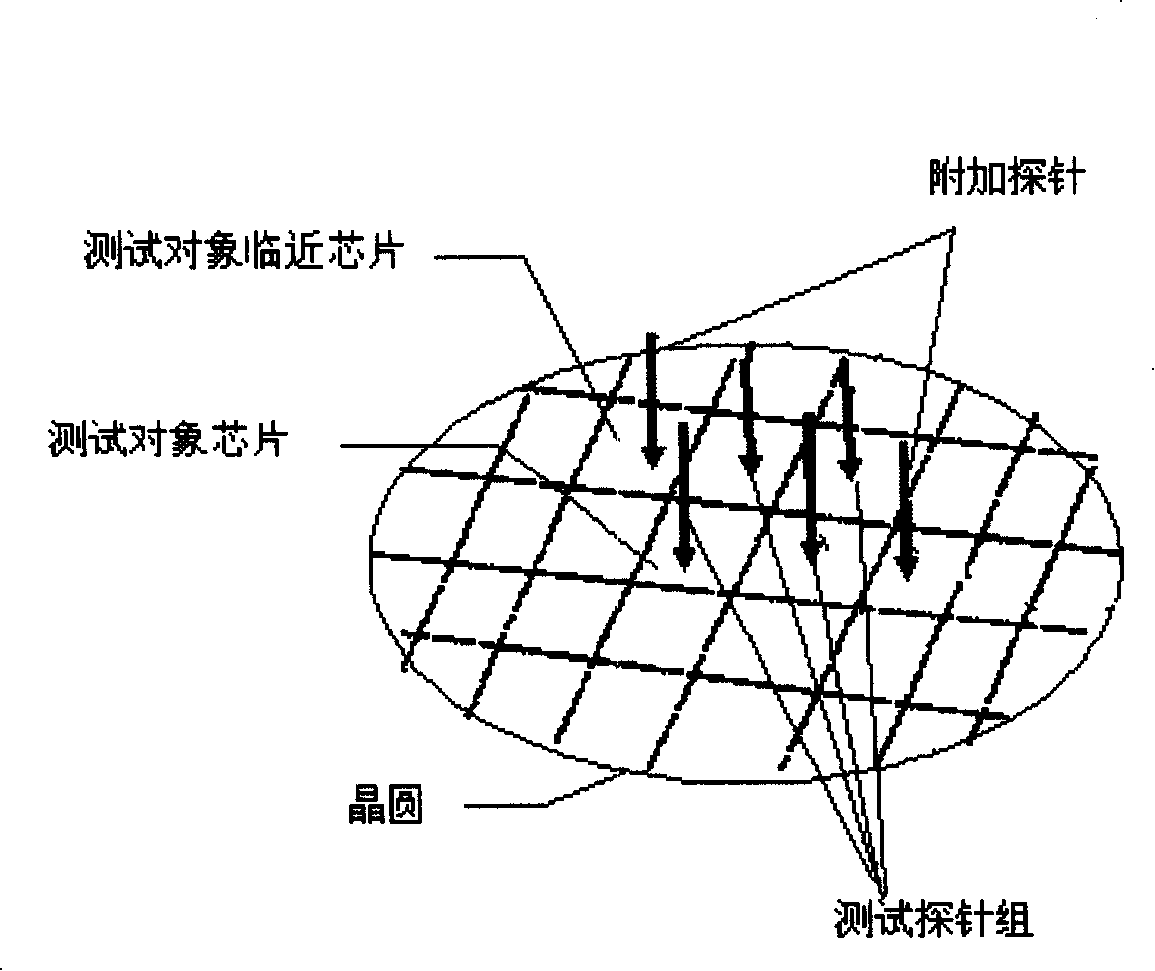

[0010] The invention reduces the test stability problem of the parallel test object caused by the fluctuation of the ground potential during the parallel test by enhancing the ground connection of the area near the test object on the wafer.

[0011] As shown in the figure, in addition to configuring the probe sets of multiple test objects required for parallel testing on the probe card, additional probes corresponding to the test objects adjacent to the chip are additionally configured. Ease of decision.

[0012] The type of chip pin terminal corresponding to the additional probe, first, consider the GND terminal (ground terminal) of the chip. If the chip does not have enough GND terminals, it can also correspond to ordinary signal terminals. On the probe card, additional probes can be connected directly to the tester's ground terminal or to the tester's test channel. If it is connected to the test channel, it needs to be set to the ground level by controlling the ATE through...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More