Testable integrated circuit, system in package and test instruction set

A system-in-package and integrated circuit technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

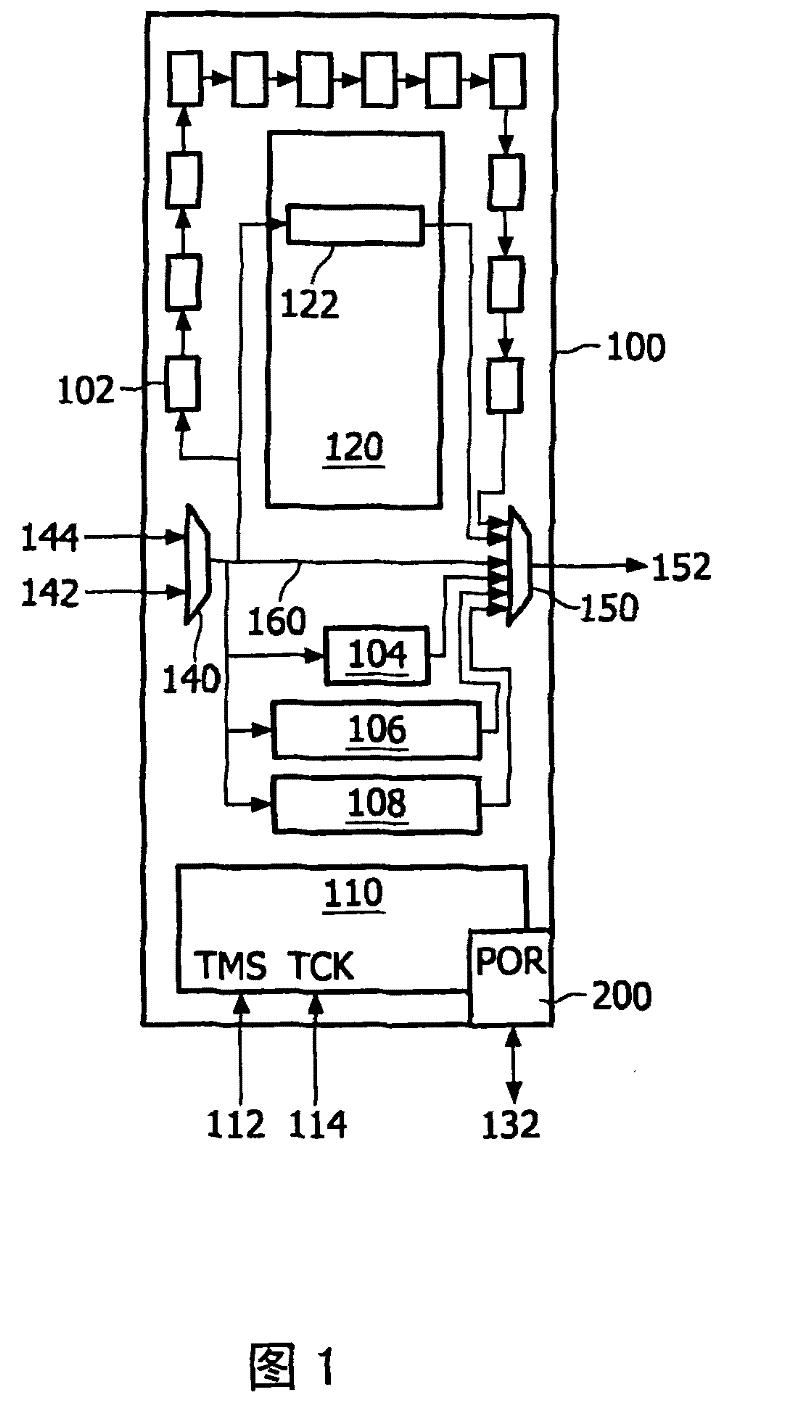

[0032] figure 1 The IC die is shown with a test configuration including a test access port (TAP) 100 and a test access port controller 110 . TAP 100 includes a plurality of shift registers, such as boundary scan or external test (extest) register 102, bypass register 104, optional identification register 106 and instruction register 108, identification register 106 typically carries the identification of the IC die code. There may be other registers, such as one or more scan chains 122, for feeding test patterns into the core logic 120 of the IC die. The TAP 100 also includes a first multiplexer (MUX) 140 and a second MUX 150 under the control of the TAP controller 110 . A first MUX 140 is arranged to receive a first input 142 and a second input 144 via respective interconnects of the IC die, while a second MUX 150 is arranged to output a test data output (TDO) via another interconnect of the IC die Signal.

[0033] Between the first MUX 140 and the second MUX 150 there i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com