Method for enhancing pattern uniformity

A uniformity and pattern technology, applied in the field of semiconductor structure manufacturing, can solve the problems of poor pattern uniformity, unresolvable pattern size difference, lower component operation efficiency and electrical performance, etc., to improve pattern uniformity and reduce size poor effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

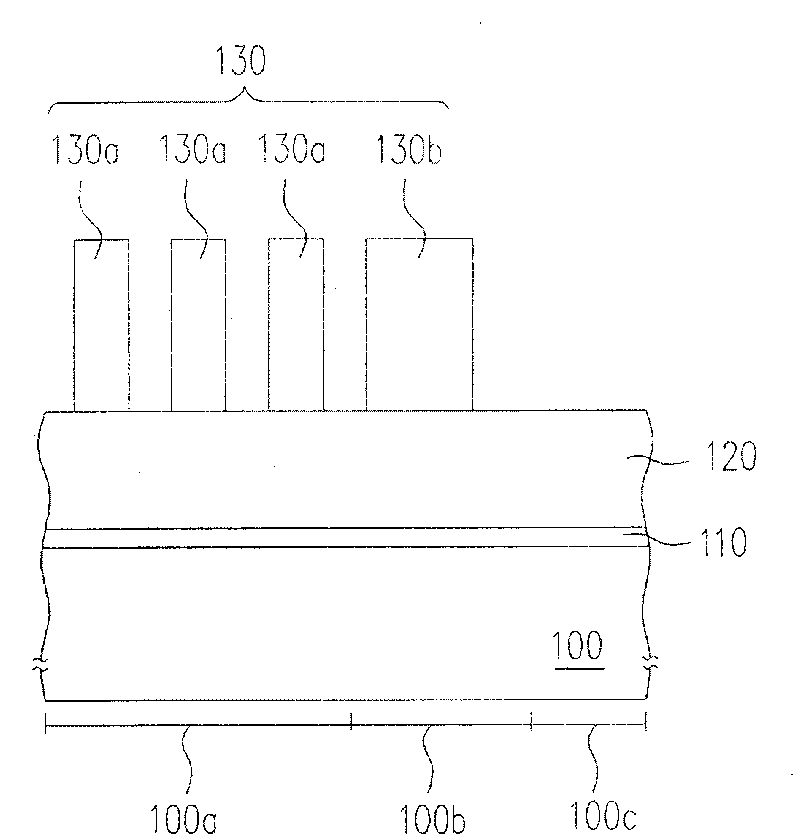

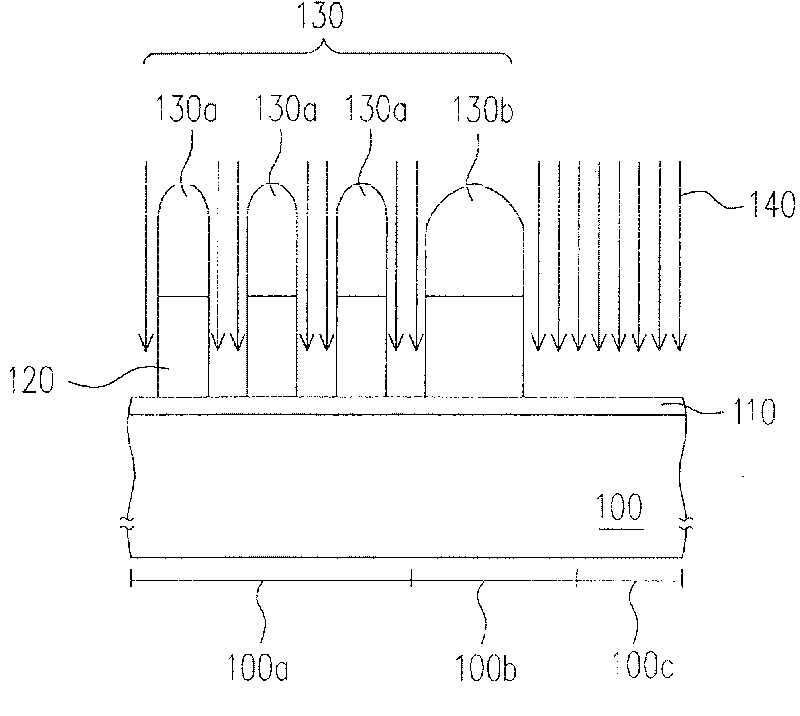

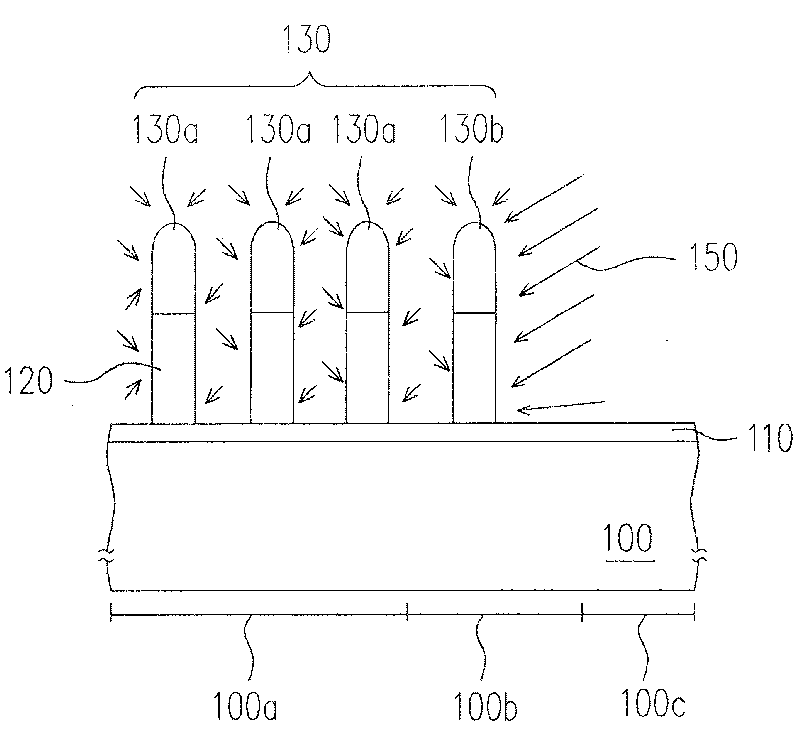

[0027] Figure 1A to Figure 1C is a cross-sectional flow diagram illustrating a method for improving pattern uniformity according to an embodiment of the present invention.

[0028] see Figure 1A , this method is applicable to the substrate 100, and the substrate 100 includes a pattern dense area 100a, a pattern semi-empty area 100b and a pattern empty area 100c. Wherein, the pattern semi-empty area 100b refers to the boundary area between the pattern dense area 100a and the pattern empty area 100c. In one embodiment, the substrate 100 may be a semiconductor wafer, the pattern dense area 100a is, for example, a memory cell area, the pattern empty area 100c is, for example, a logic element area, and the pattern semi-empty area 100b is, for example, a memory cell area and a logic element area the middle area. Wherein, for example, memory cells have been formed on the pattern dense area 100 a , and general logic elements have been formed on the pattern empty area 100 c , for e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More