Method of manufacturing a semiconductor device

A semiconductor and device technology, applied in the field of manufacturing semiconductor devices, can solve problems such as reliability, reduce injection damage, and facilitate in-depth access

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

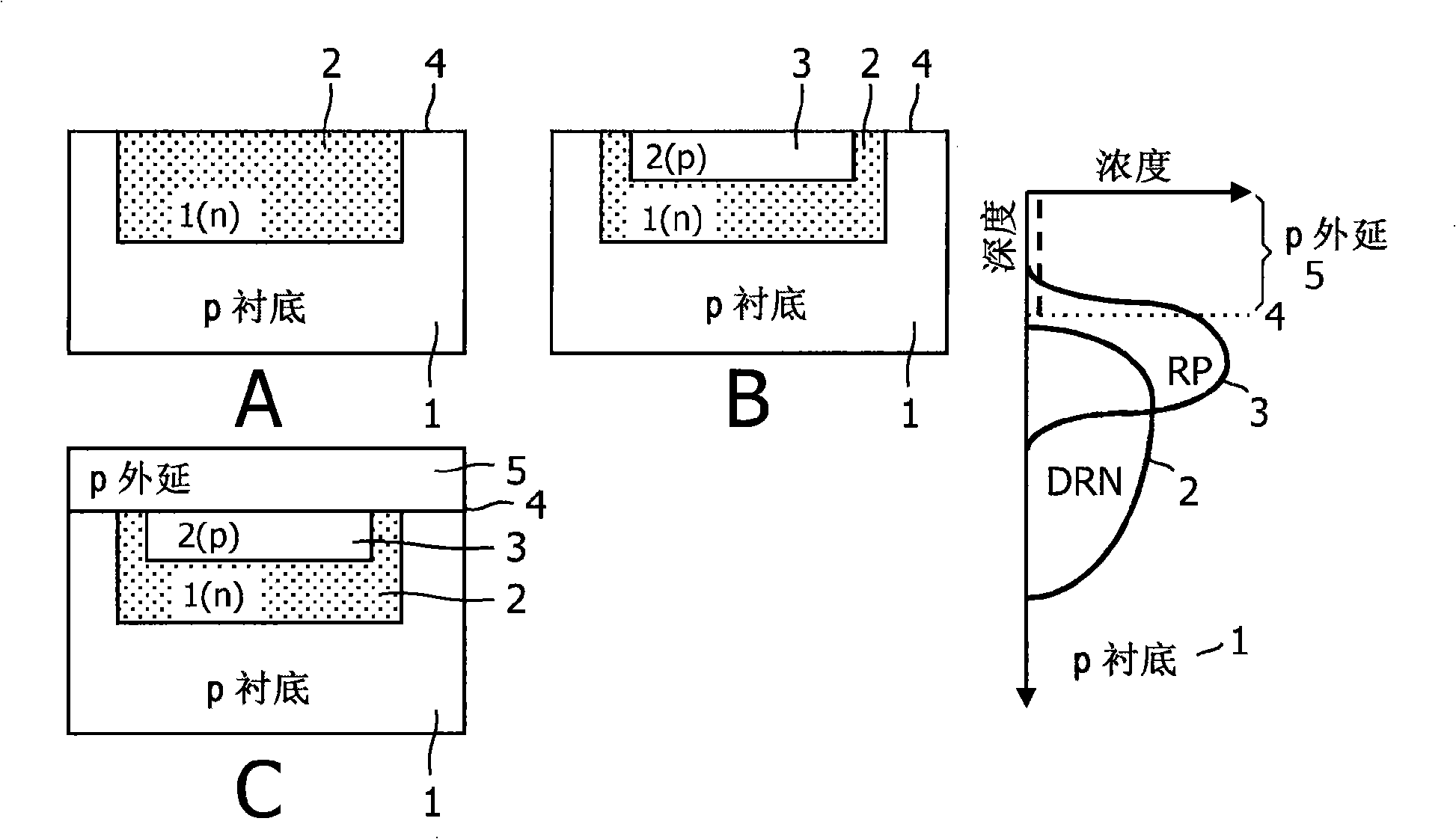

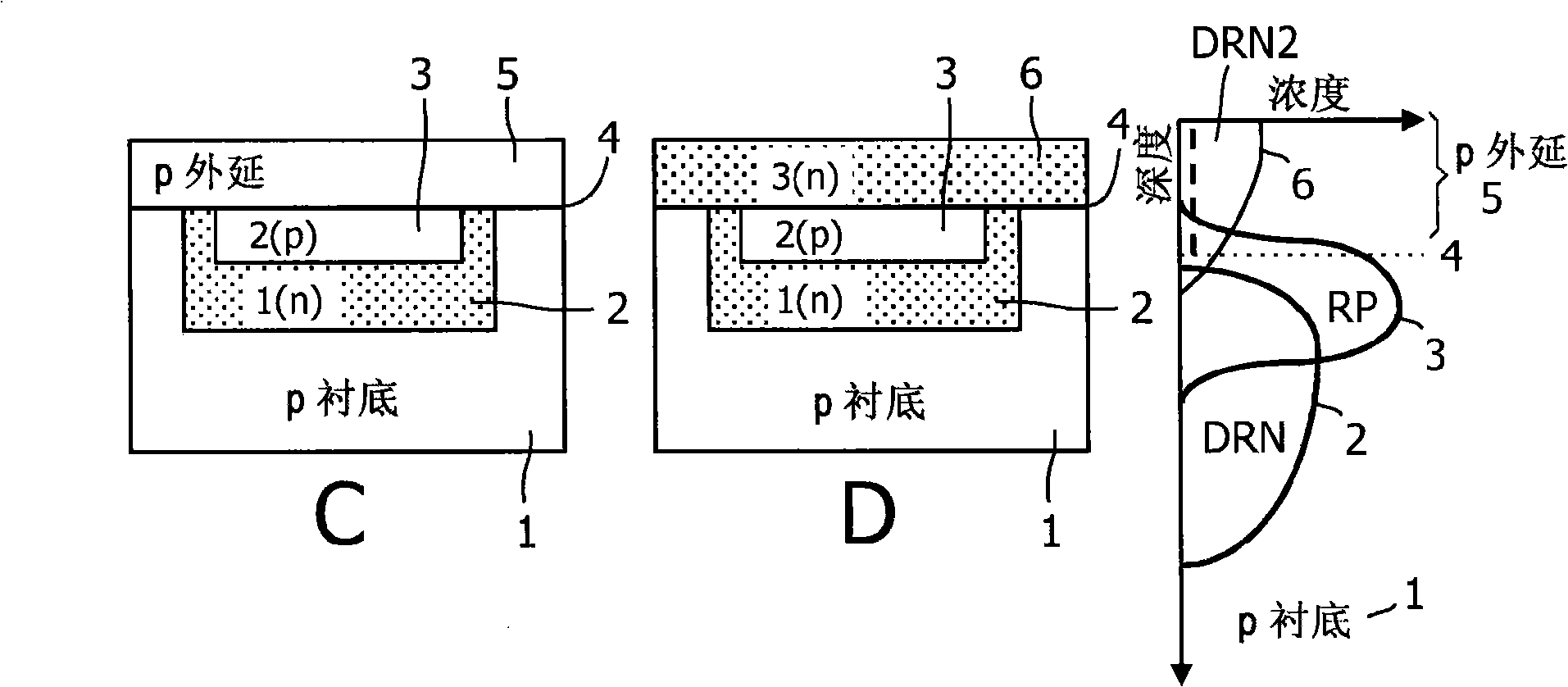

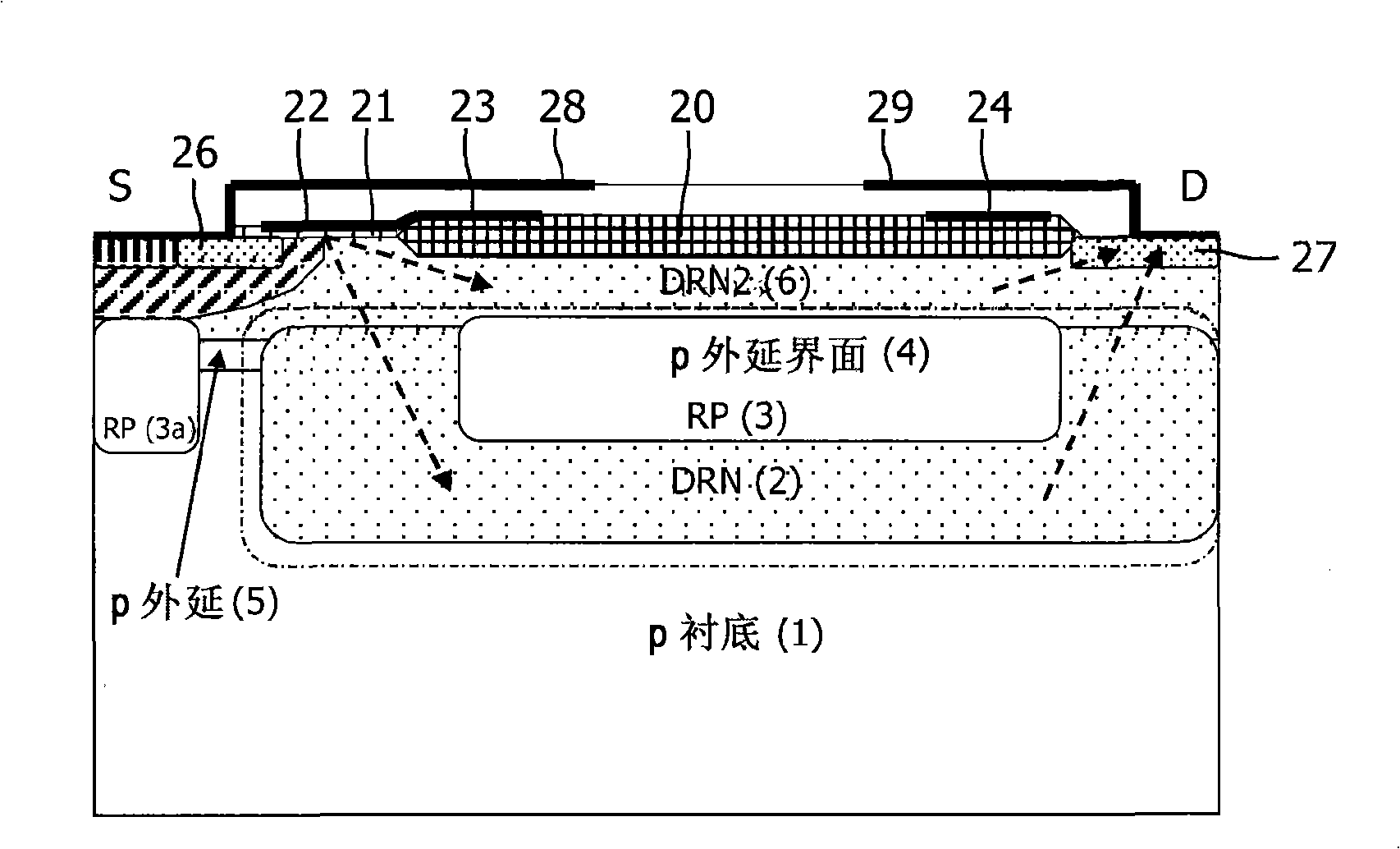

[0039] Figure 1 shows a first preferred embodiment of the method according to the invention. A p-type Si substrate 1 is implanted with an n-type dopant atom mask to form a first region 2 . In this example, P atoms are used with an implant energy of 100keV and a dose of approximately 6×10 16 at / cm 2 . For RESURF, the implant dose is preferably at 1×10 12 and 1×10 13 at / cm 2 range between. A high temperature diffusion step of 540 minutes at 1150° C. allows the n-type dopant atoms to penetrate deeper into the substrate, thereby forming a deep n-type region 2 (labeled here Deep Resurf n, DRN, see FIG. 1A ).

[0040] The second region 3 is formed by implanting a p-type dopant, such as boron or indium, using a mask, on the surface 4 ( FIG. 1B ) of the substrate 1 . Here, boron is implanted at an energy of 100-180keV, and its dose is about 6×10 12 at / cm 2 . For Resurf, the injection dose is preferably at 1×10 12 and 1×10 13 at / cm 2 range between. Therefore, a p-type lay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More