Low-voltage difference linear voltage stabilizer without off-chip compensation capacitor

A technology of low-dropout linearity and capacitor compensation, which is applied in the direction of instruments, electric variable adjustment, control/regulation systems, etc., can solve problems such as poor precision and achieve high-precision results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The low-dropout linear voltage regulator without off-chip compensation capacitor of the present invention will be further described below in conjunction with the accompanying drawings.

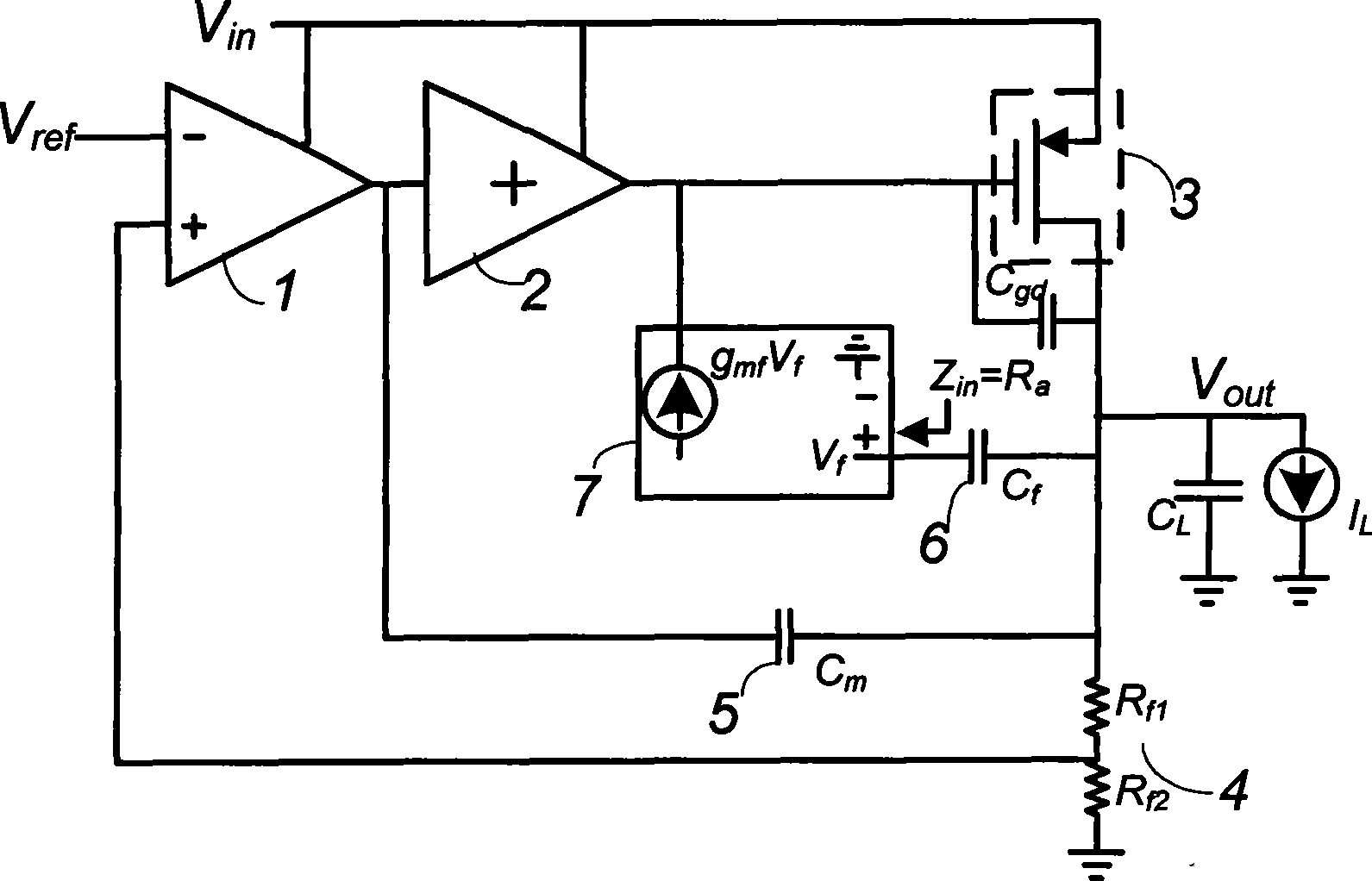

[0019] The block diagram of LDO without off-chip compensation capacitor proposed by the present invention is as follows: figure 1 As shown, the first-stage amplifier (1) and the second-stage amplifier (2) constitute the error amplifier; the power PMOS transistor (3) is connected in series with the two-stage error amplifier, and its size is larger than that of a power transistor with the same load current in general much smaller; the input voltage V in It is connected with the source of the power PMOS transistor (3), and is used as the power supply of the error amplifier (1, 2) at the same time; the resistor divider network (4) is used to form negative feedback; in addition, two compensation capacitors (5, 6 ), wherein the first compensation capacitor (5) is connected between the output...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More