Dynamic binary translation method for cooperation design of software and hardware

A technology of dynamic binary and software-hardware collaboration, which is applied in the field of binary translation and process-level virtual machines, can solve the problems of not being suitable for general-purpose processor instruction sets, not having dynamic characteristics, and high hardware overhead, etc., and achieving Misss time mitigation and Tcachemiss rate Reduced, start-up time mitigation effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to better understand the technical solution of the present invention, the following specific examples are used for further description. The following examples are not intended to limit the present invention.

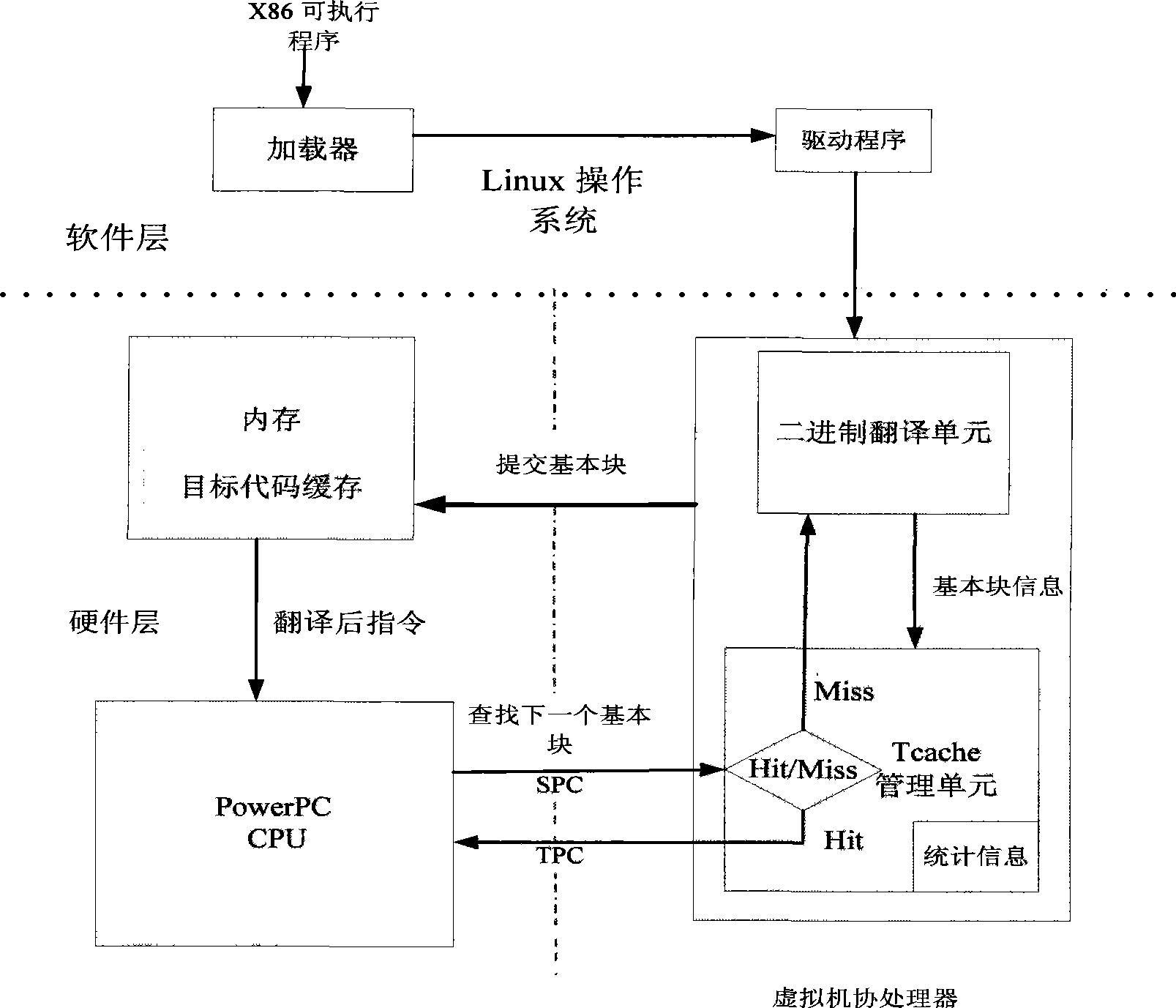

[0023] The present invention selects x86 as the source instruction platform of specific implementation mode, and PowerPC is as the target platform, and the overall structure of the system is divided into three parts as figure 1 Shown: the software layer includes the loader of the x86 executable file, the virtual machine coprocessor driver and the Linux operating system, and the hardware part includes the PowerPC processor, the memory and the virtual machine coprocessor. The virtual machine coprocessor is mainly composed of two parts: a binary translator and a Tcache manager.

[0024] figure 1 is the overall structure of the system, such as figure 1 As shown, the specific steps of the dynamic binary translation method of the software-hardware co-design ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More