Method for implementing assist nuclear task dynamic PRI scheduling with hardware assistant

A dynamic priority, hardware-assisted technology, applied in the direction of resource allocation, multi-programming devices, etc., can solve problems such as the performance bottleneck of the scheduler system, and achieve the effect of eliminating performance bottlenecks, reducing burden, and avoiding starvation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

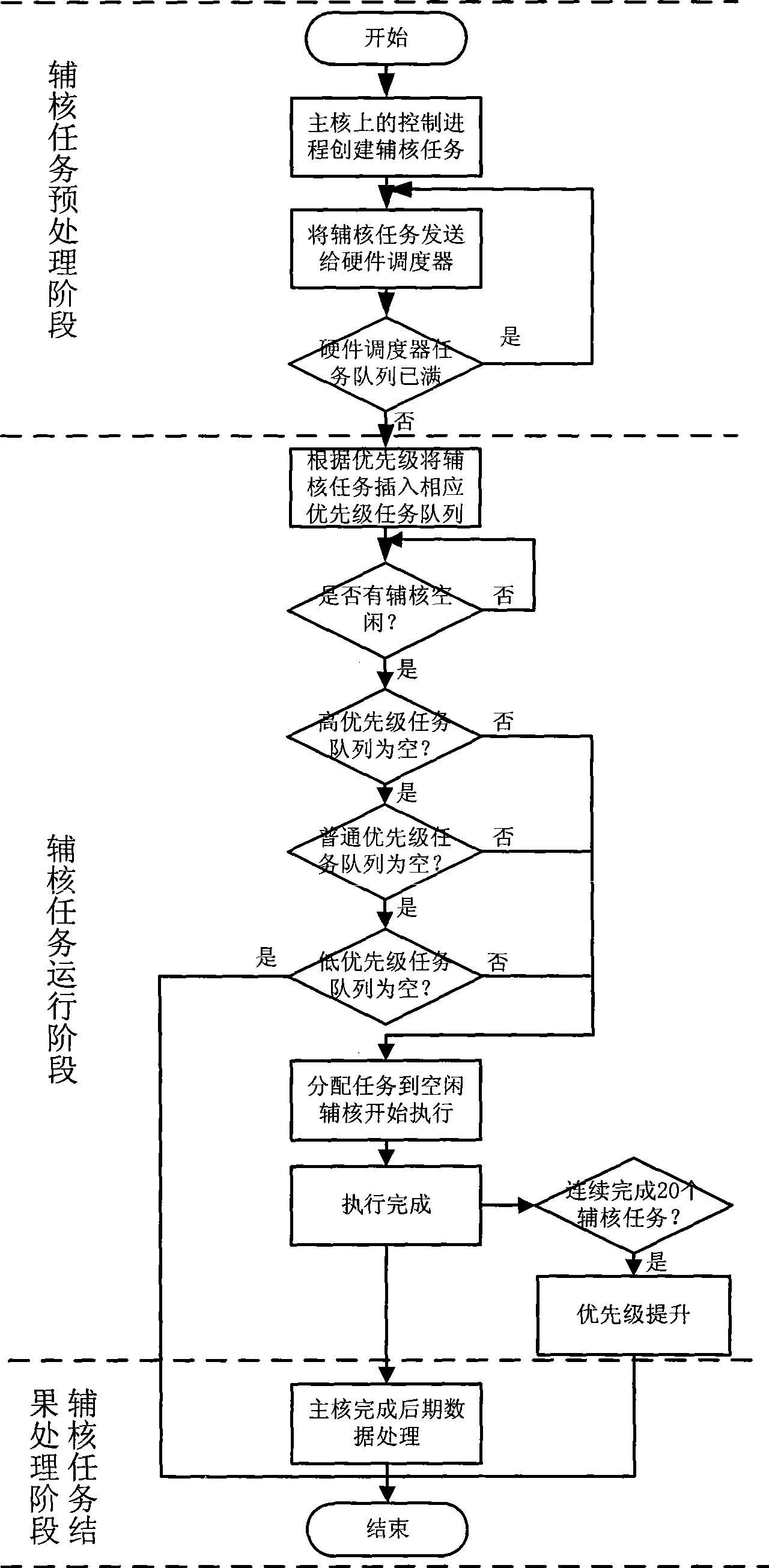

[0027] In the present invention, the execution of the auxiliary core task is divided into the above three stages. In each stage of the task, the hardware scheduler assists the operating system scheduler running on the main core to manage and schedule the auxiliary core task correspondingly. The implementation of the present invention will be described in detail below.

[0028] 1. An implementation method of hardware-assisted auxiliary core task dynamic priority scheduling, characterized in that:

[0029] 1) Three phases of the auxiliary nuclear mission:

[0030] ① Auxiliary core task preprocessing stage

[0031] The main core is responsible for the preprocessing stage of the auxiliary core task. The process running on the main core that needs to be accelerated by the auxiliary core will create an auxiliary core task running on the auxiliary core to accelerate the application program. The main creation is the auxiliary core The context of the task includes the instruction seq...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More