Electronic circuit that comprises a memory matrix and method of reading for bitline noise compensation

A technology of memory, memory unit, applied in the direction of static memory, digital memory information, information storage, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

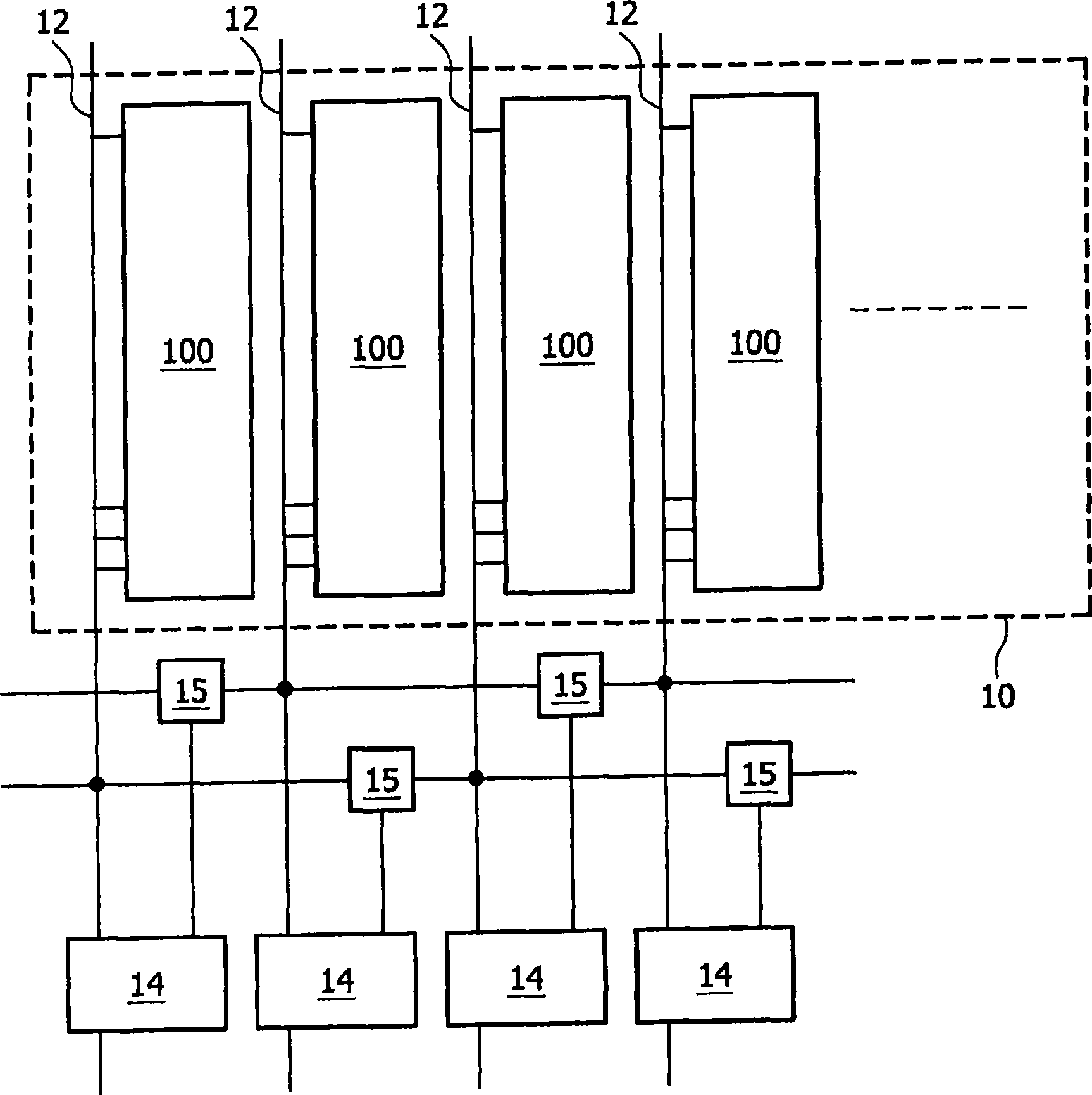

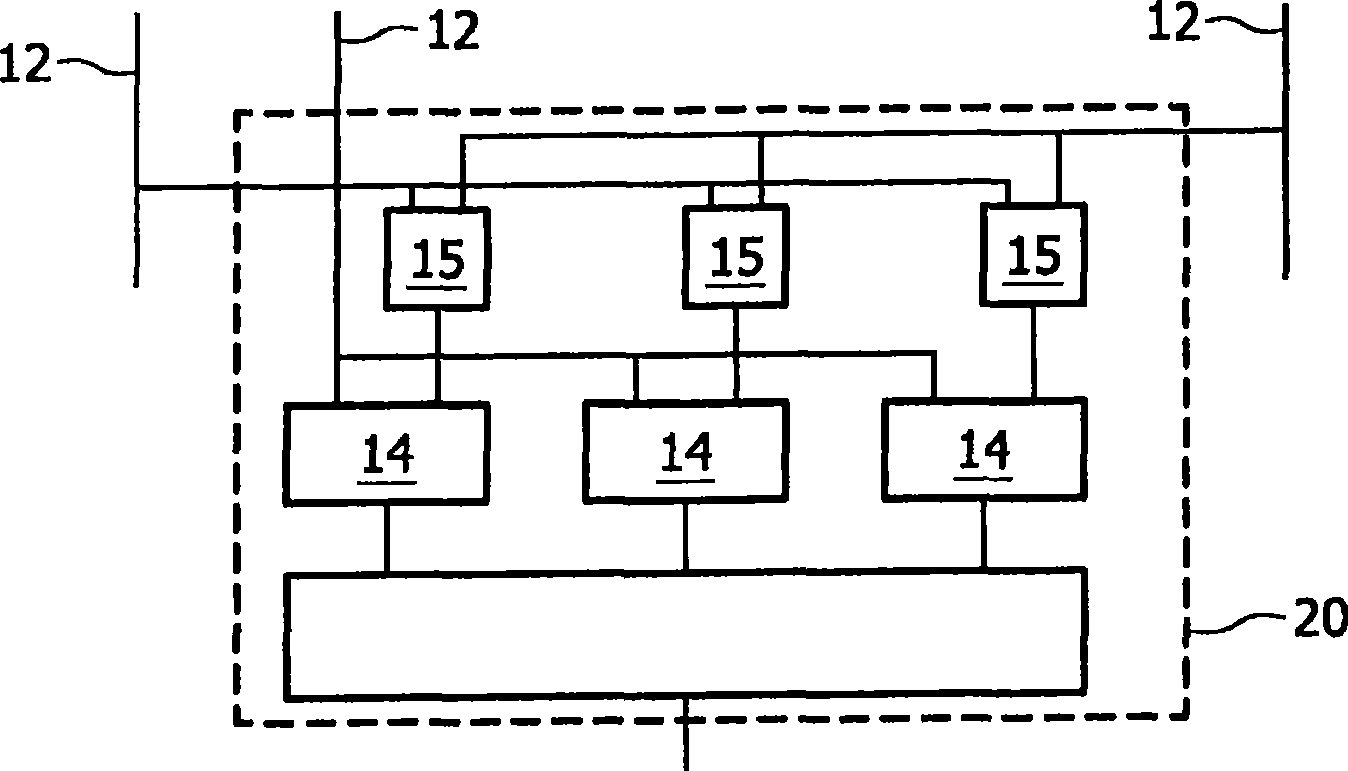

[0014] figure 1 A circuit is shown having a memory matrix 10 comprising a plurality of columns 100 of memory cells. For each column 100 , the circuit includes a respective bit line 12 , differential sense amplifier 14 and reference circuit 15 . For each column 100 , the bit line 12 of the column 100 is the conductor coupled to the memory cells in the column 100 . For each column 100 , the differential sense amplifier 14 for the column 100 has a first input coupled to the bit line 12 of the column 100 and a second input coupled to the output of the reference circuit 15 for the column 100 . For each column 100, the input of the reference circuit 15 for the column 100 is coupled to the bit line 12 for the adjacent column 100 (or the column if the column is at the edge of the matrix).

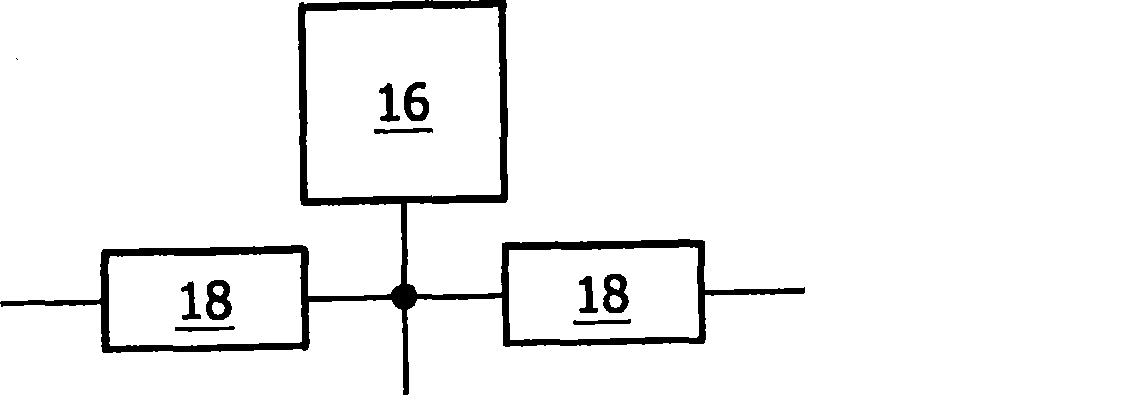

[0015] Figure 1a One of the reference circuits 15 including a core reference circuit 16 (which is not dependent on a signal on a bit line) and a resistive element 18 coupling the output of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More