Virtual FPGA structural modeling and mapping method thereof

A technology of structural modeling and modeling methods, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of low logic resource utilization, low evolution efficiency, poor versatility, etc., and achieve good flexibility and Versatility, improving evolutionary efficiency and the effect of

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

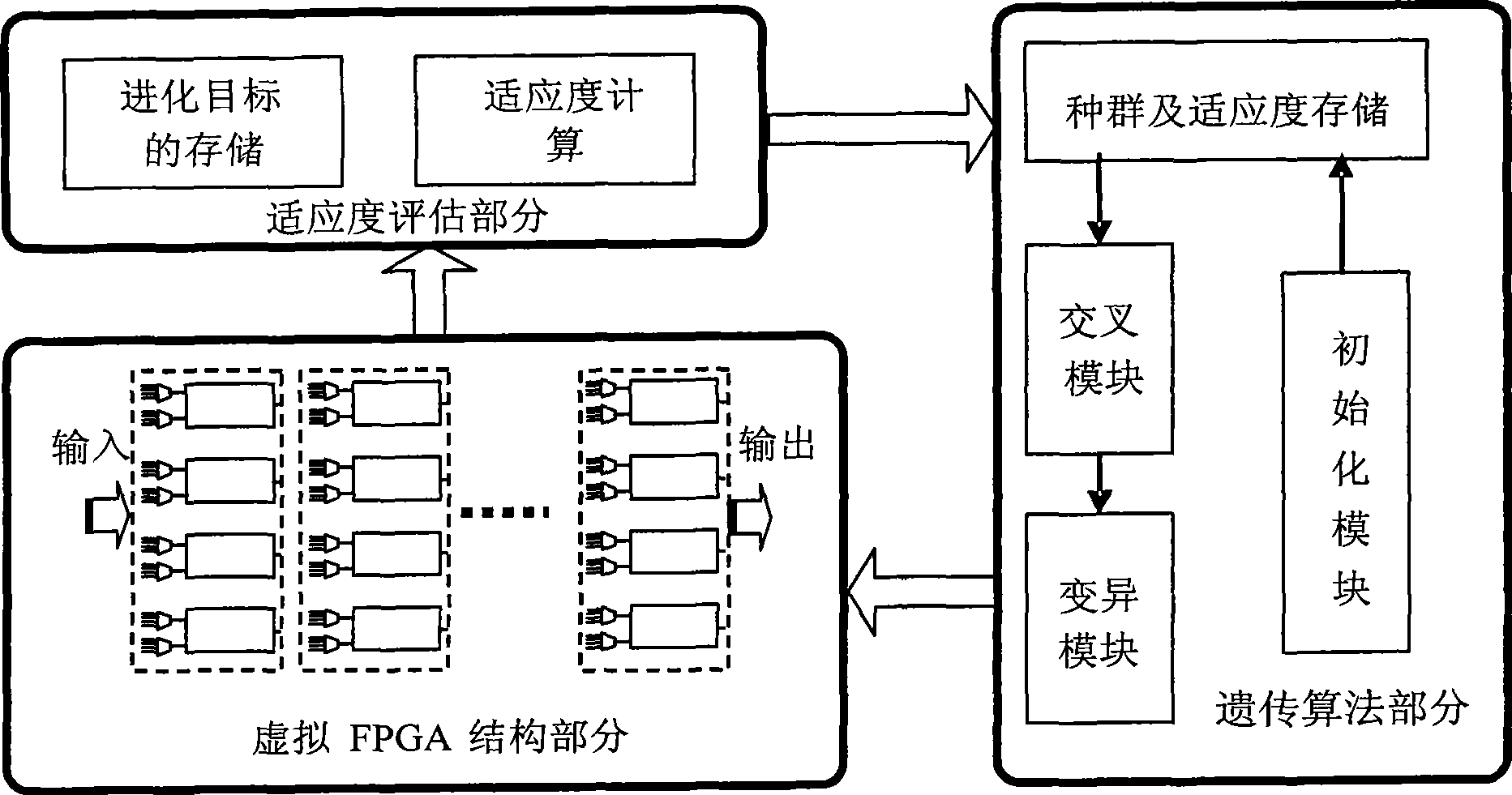

[0031] The virtual FPGA structure modeling and mapping method of the present invention will be further described below in conjunction with the accompanying drawings.

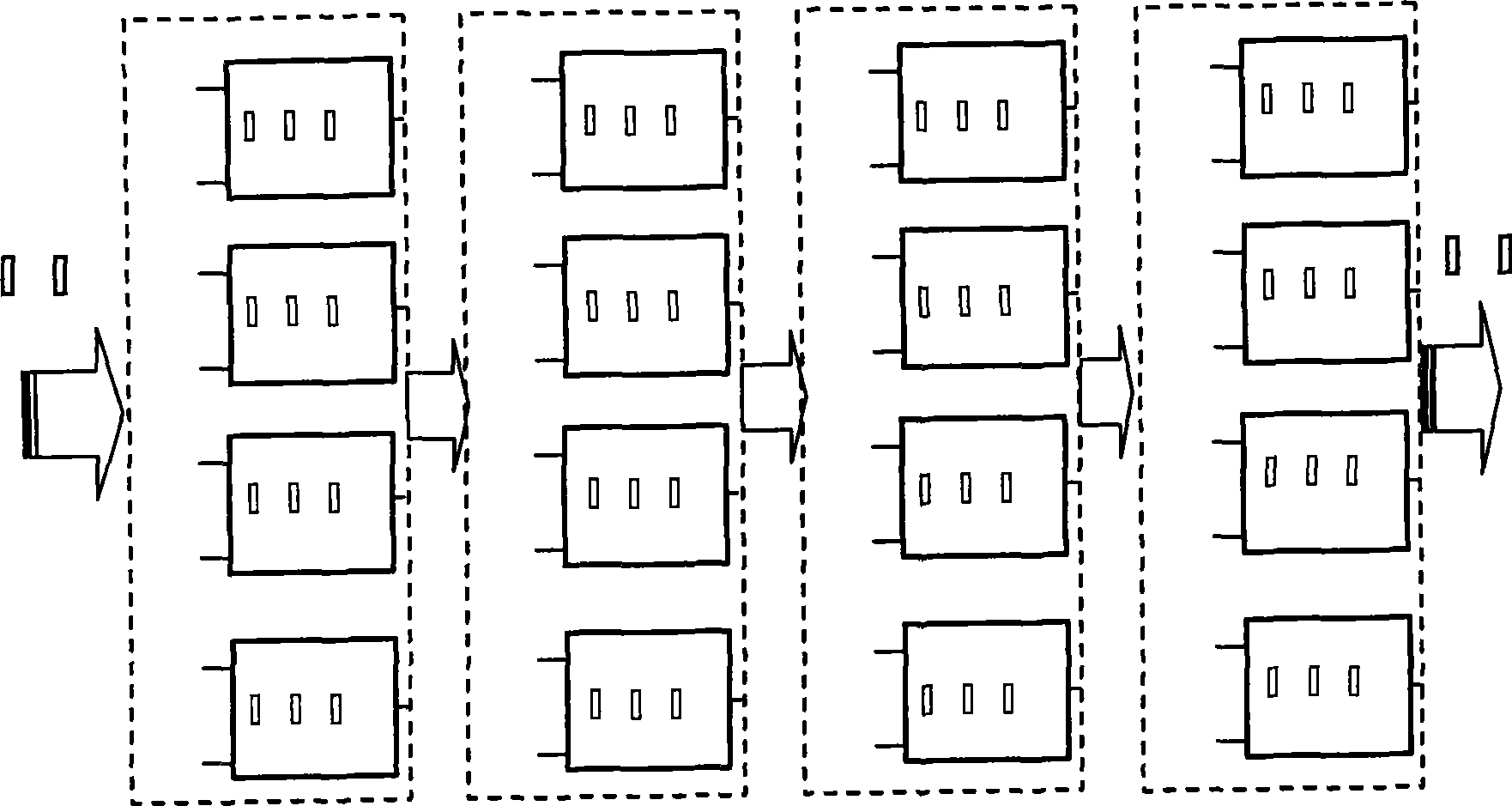

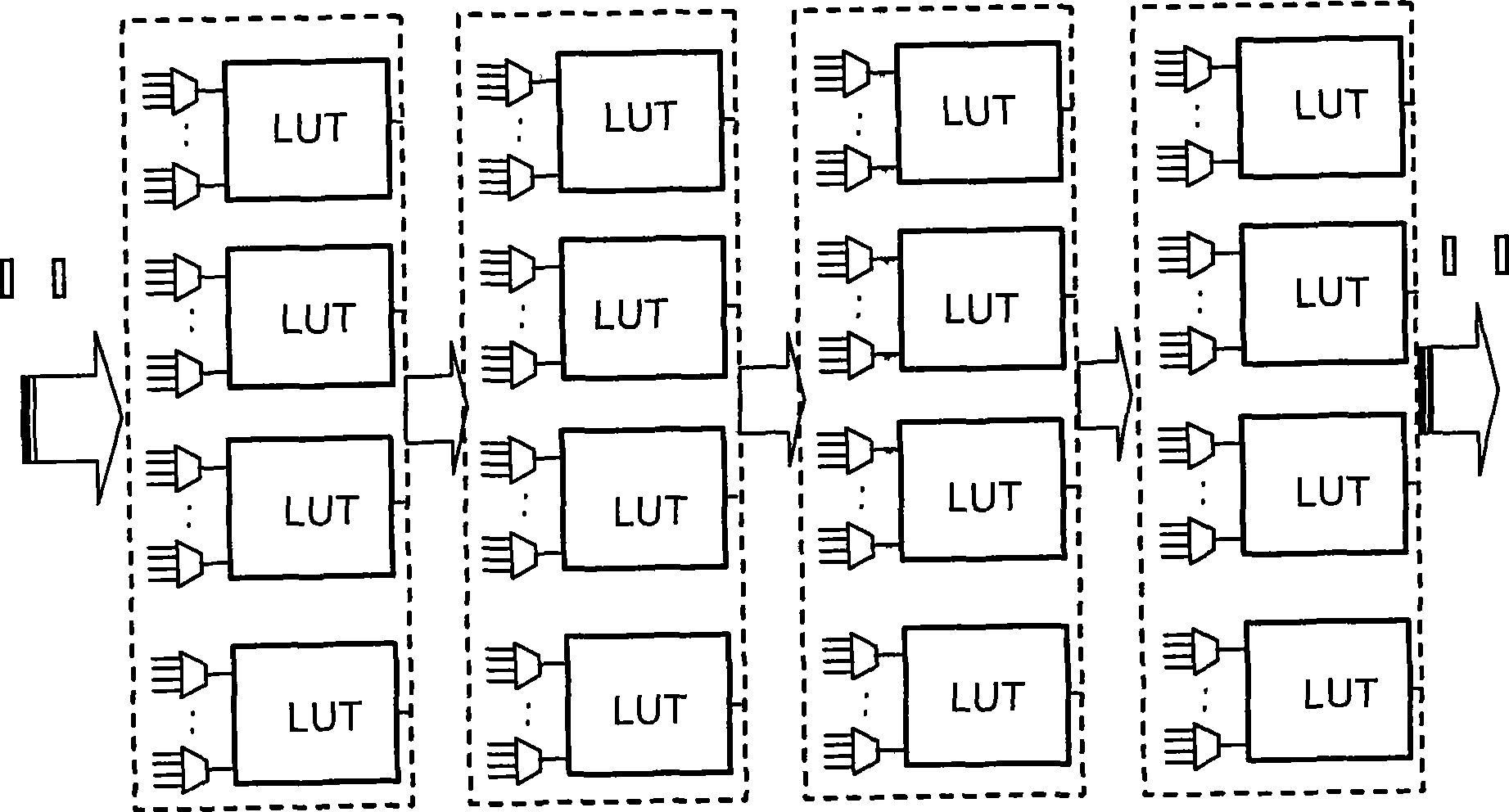

[0032] For mainstream virtual FPGA model structures (such as figure 1 shown), the present invention proposes a modeling method of a LUT-based virtual FPGA structure model that is closely combined with the FPGA underlying structure, and the virtual FPGA structure model established by this method (such as figure 2 shown) is an arbitrary n-input LUT as the basic unit of circuit evolution, and a virtual FPGA array structure is composed of such basic units.

[0033] The specific modeling method is:

[0034] (1) Determine the cells and their interconnections in the virtual FPGA structure

[0035] The modeling method of the present invention takes n input LUTs as basic units, and establishes an array of m (rows)×p (columns); in the m×p basic unit arrays, each of the n input ends of each basic unit is set with one M...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More