Table-look-up type data weighting balance circuit and dynamic component matching method

A technology of averaging circuits and weights, applied in digital-to-analog converters, delta modulation, etc., to solve problems such as large capacitance values and infeasibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

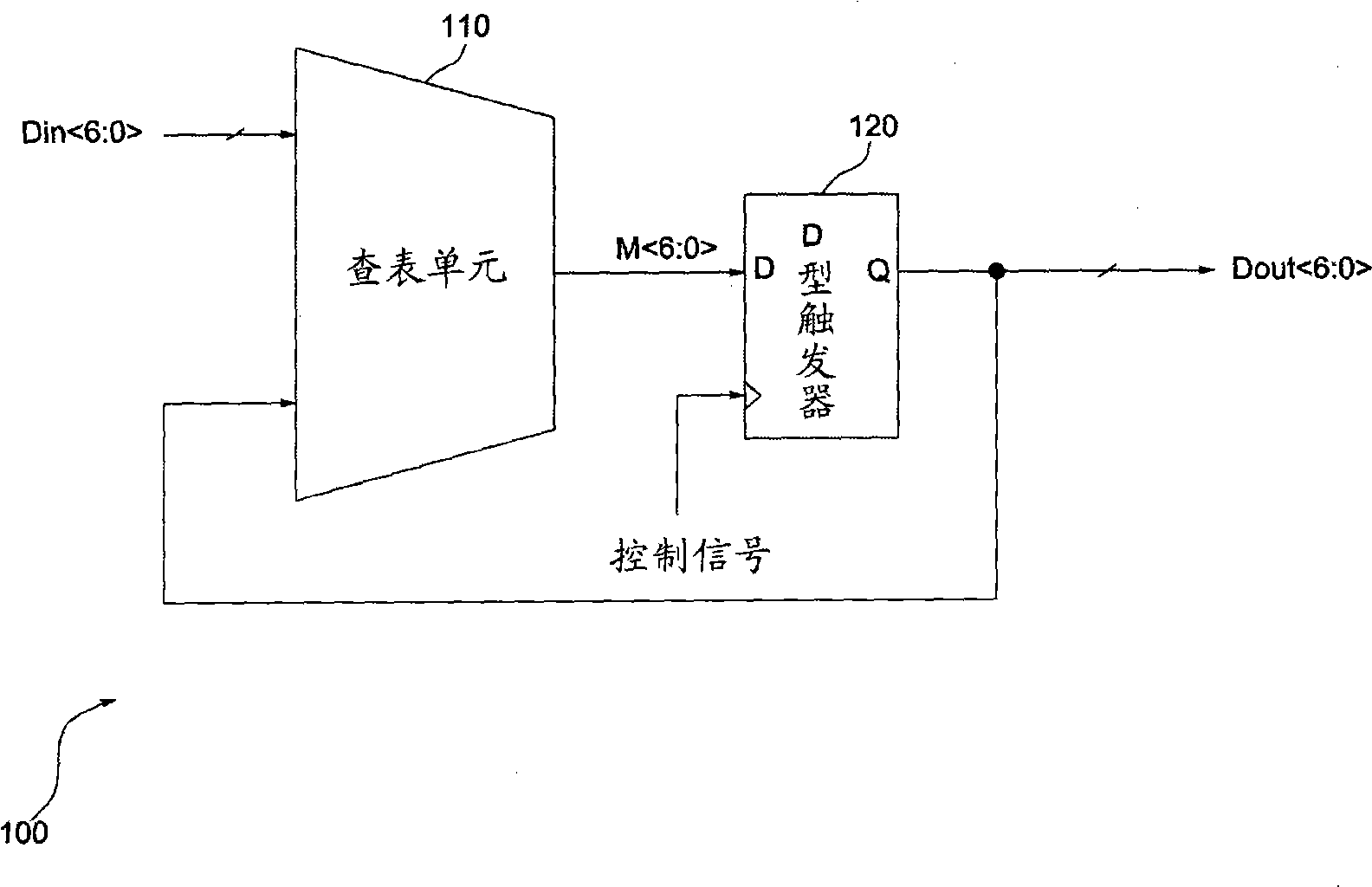

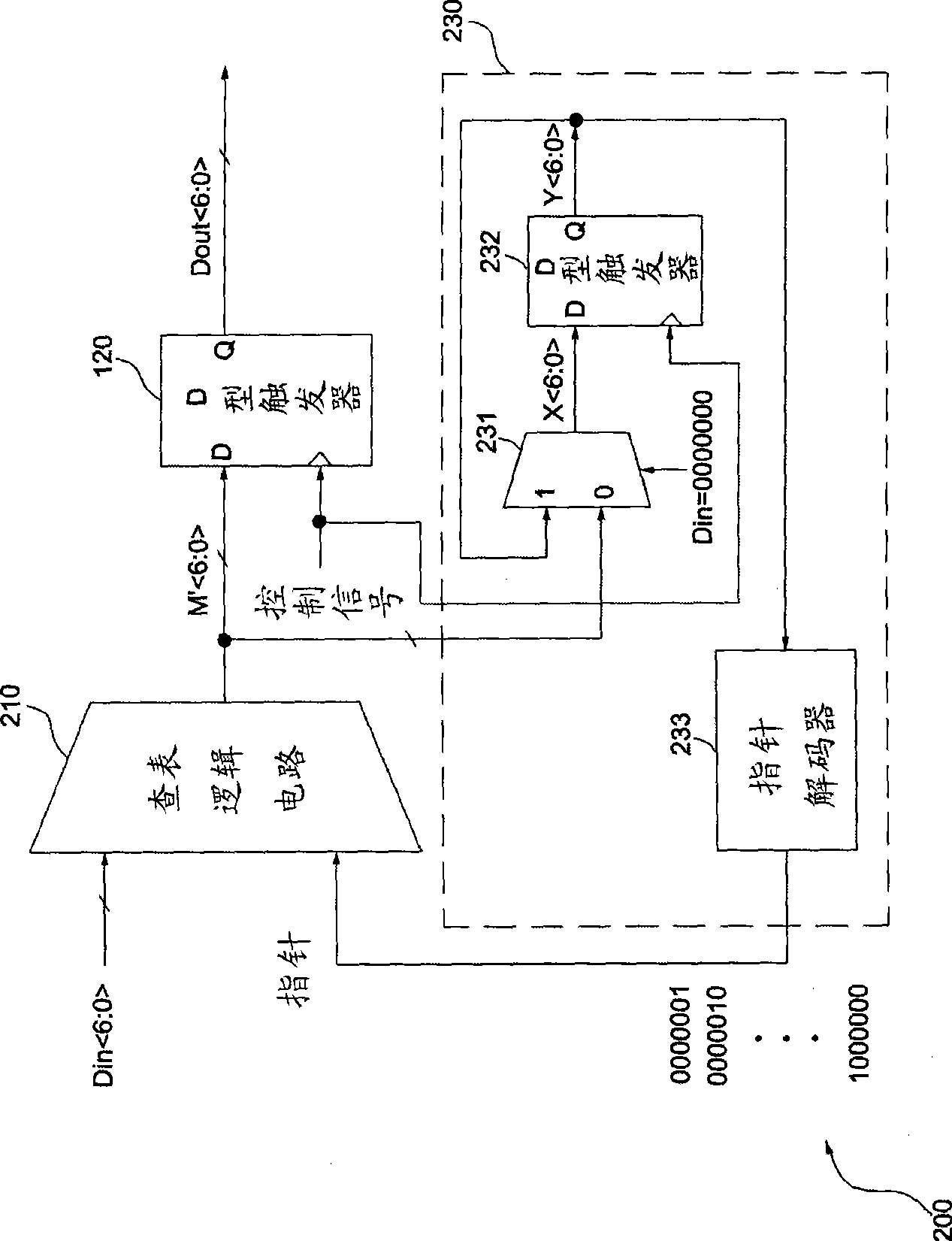

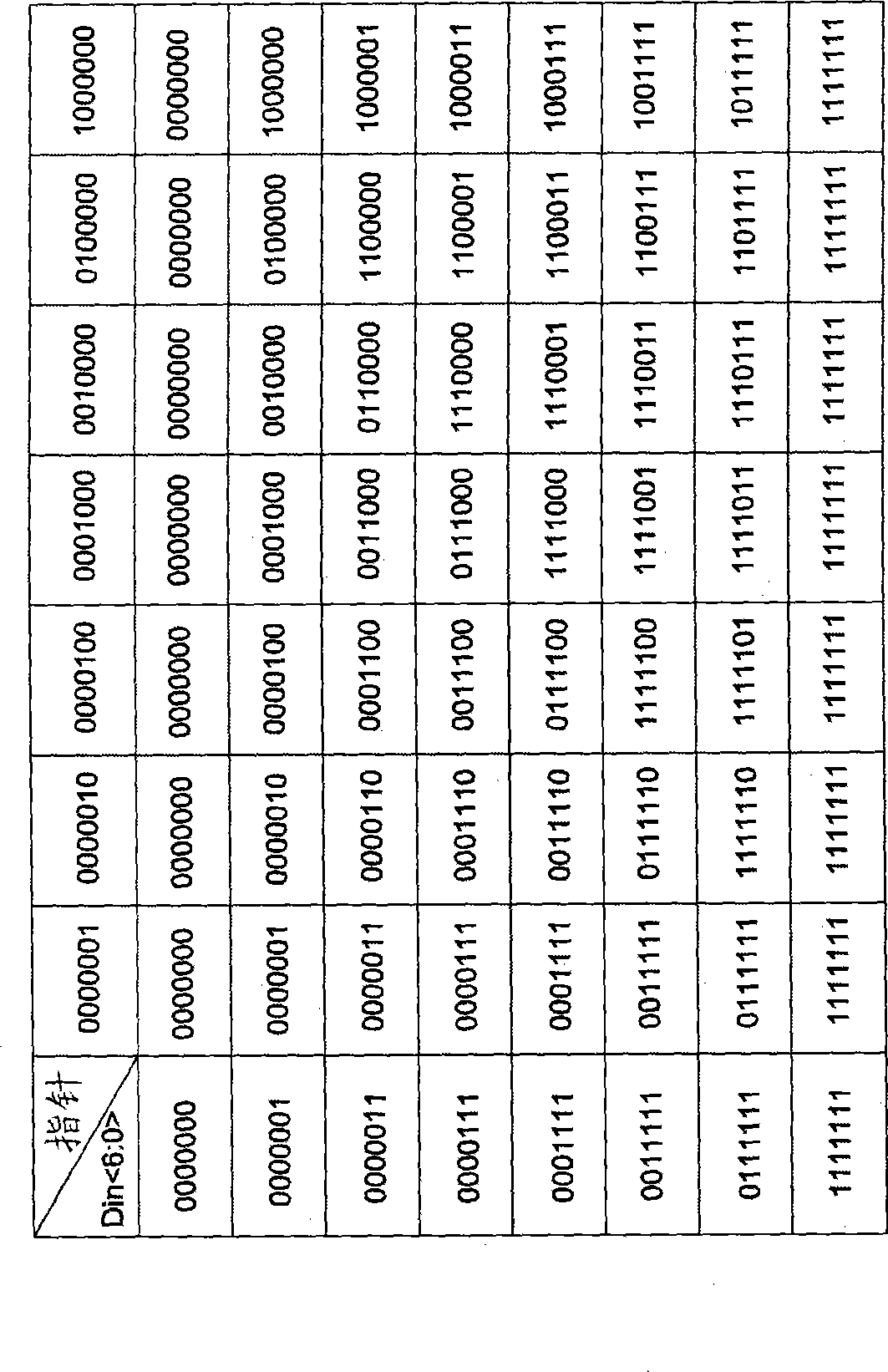

[0016] The present invention pre-stores all possible outputs of a data weight averaging circuit of a specific order and a specific bit width in a built-in truth table, and the table lookup unit 110 or the table lookup logic circuit 210 only needs to input two sets of Data to query the truth table and select the corresponding output. The present invention does not need to convert between thermometer codes and binary codes, nor does it require the operation of an adder, so not only can the speed be greatly improved, but at the same time, the operation delay will not be affected by the order of the data weight averaging circuit and the input data. affected by different bit widths.

[0017] For convenience, the following is from Figure 1 to Figure 3 , the back-end circuit of the table look-up type data weight averaging circuit of the present invention is a 3-bit (N=3) digital-to-analog converter with 7 digital-to-analog conversion units. Please note that the present invention is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More