Evaluation method for decoupling capacitor on ASIC sheet based on chain circuit

A technology of ASIC circuit and chain circuit, which is applied in the field of ASIC on-chip decoupling capacitor estimation, and can solve problems such as affecting the circuit and unstable power supply voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

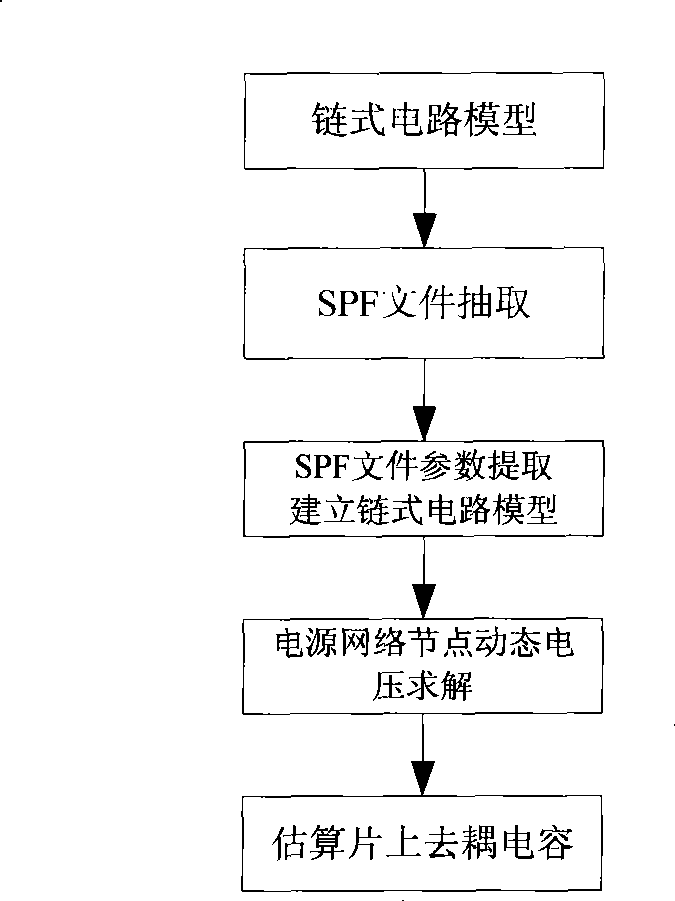

[0050] Such as figure 1 Shown is the basic flow of the method of the present invention, and its implementation steps are described in detail below.

[0051] A method for estimating decoupling capacitance on an ASIC chip based on a chain circuit, comprising the steps of:

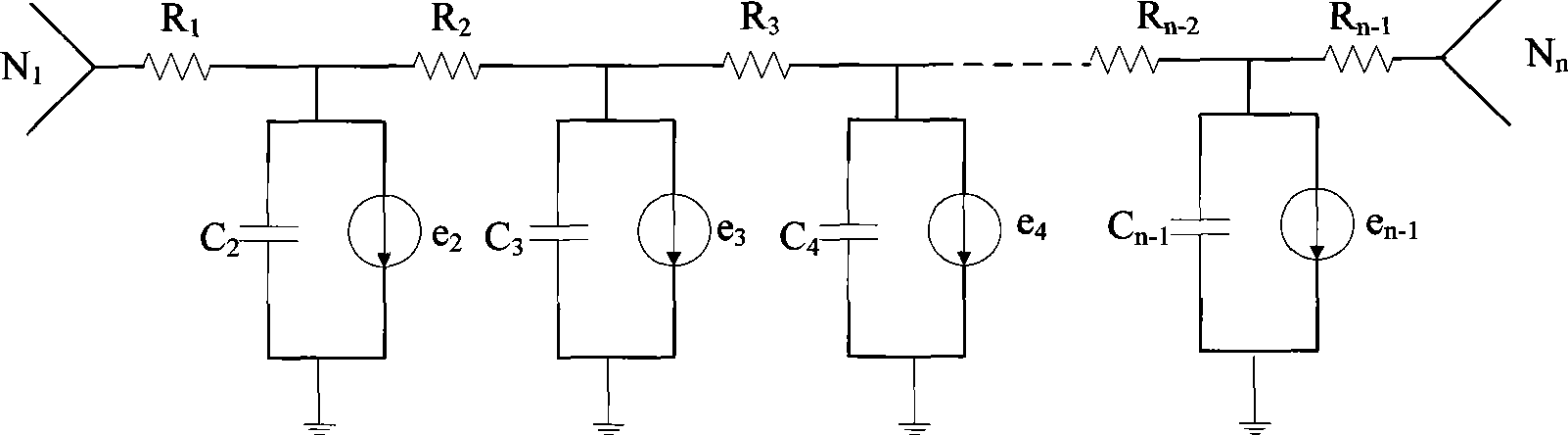

[0052] (1) if figure 2 The RC chain circuit model in the ASIC circuit shown

[0053] According to the characteristics of the ASIC circuit, the entire network is abstracted as a chain circuit, and its main parameter information includes: the connection relationship between component nodes, the resistance value R between nodes i , node capacitance C i And the equivalent current source of the component e i , where the constant current source simulates the charging and discharging process of the standard cell in the chip;

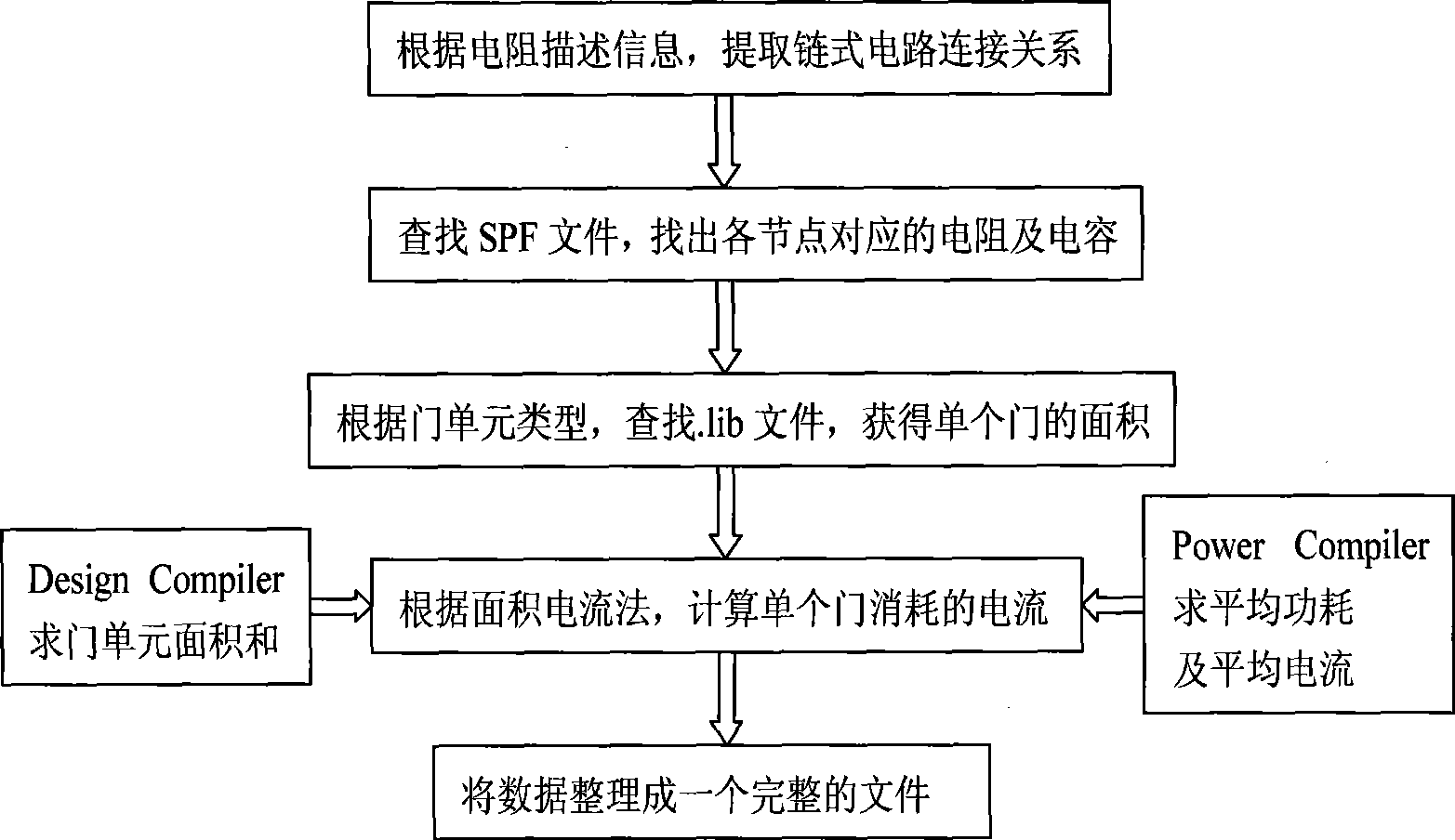

[0054] (2) SPF file extraction

[0055] Use the tool Star-RCXT to extract the parasitic parameter file of the circuit after wiring, that is, the SPF file. The command is: StarXtract-cle...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More