Patents

Literature

92 results about "Circuit modeling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

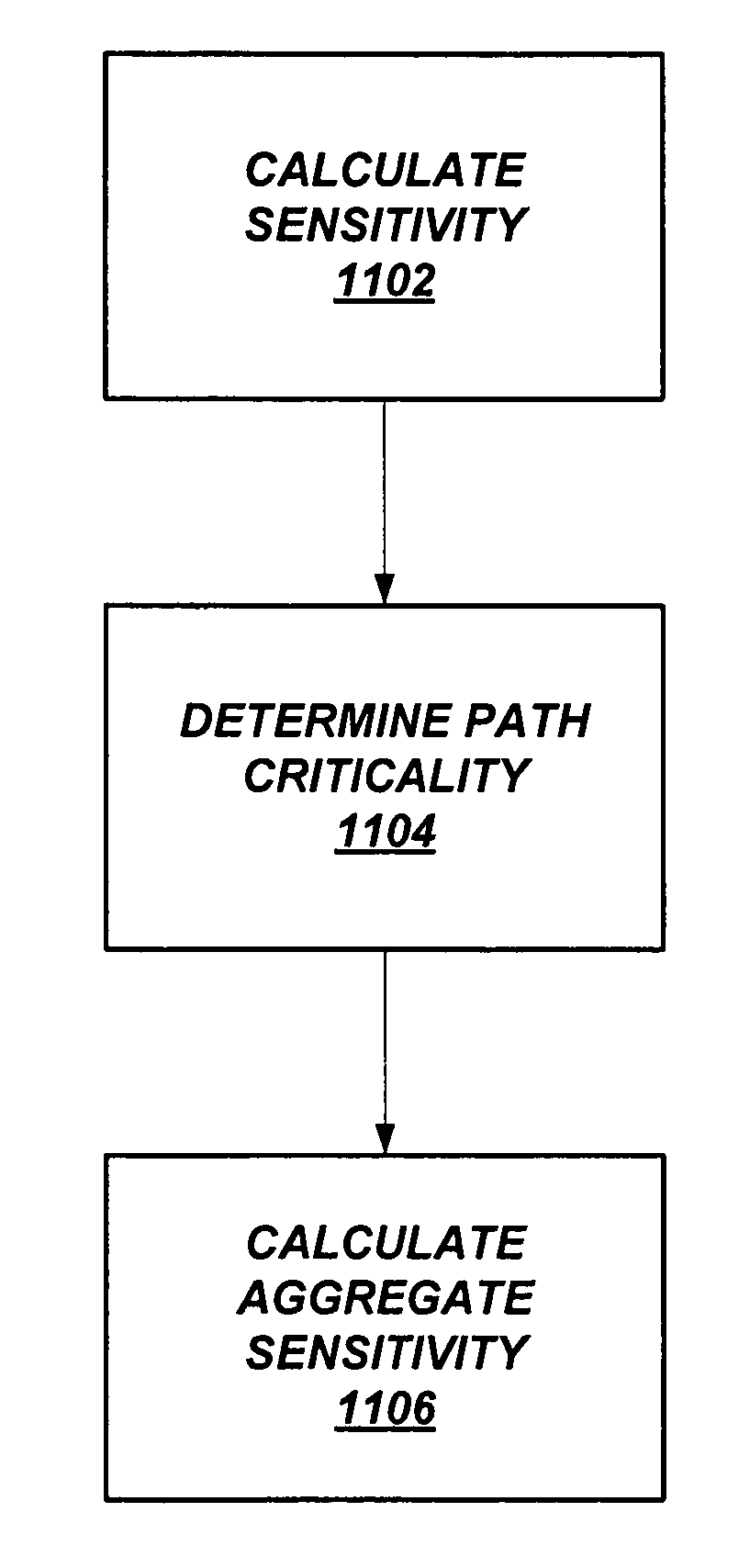

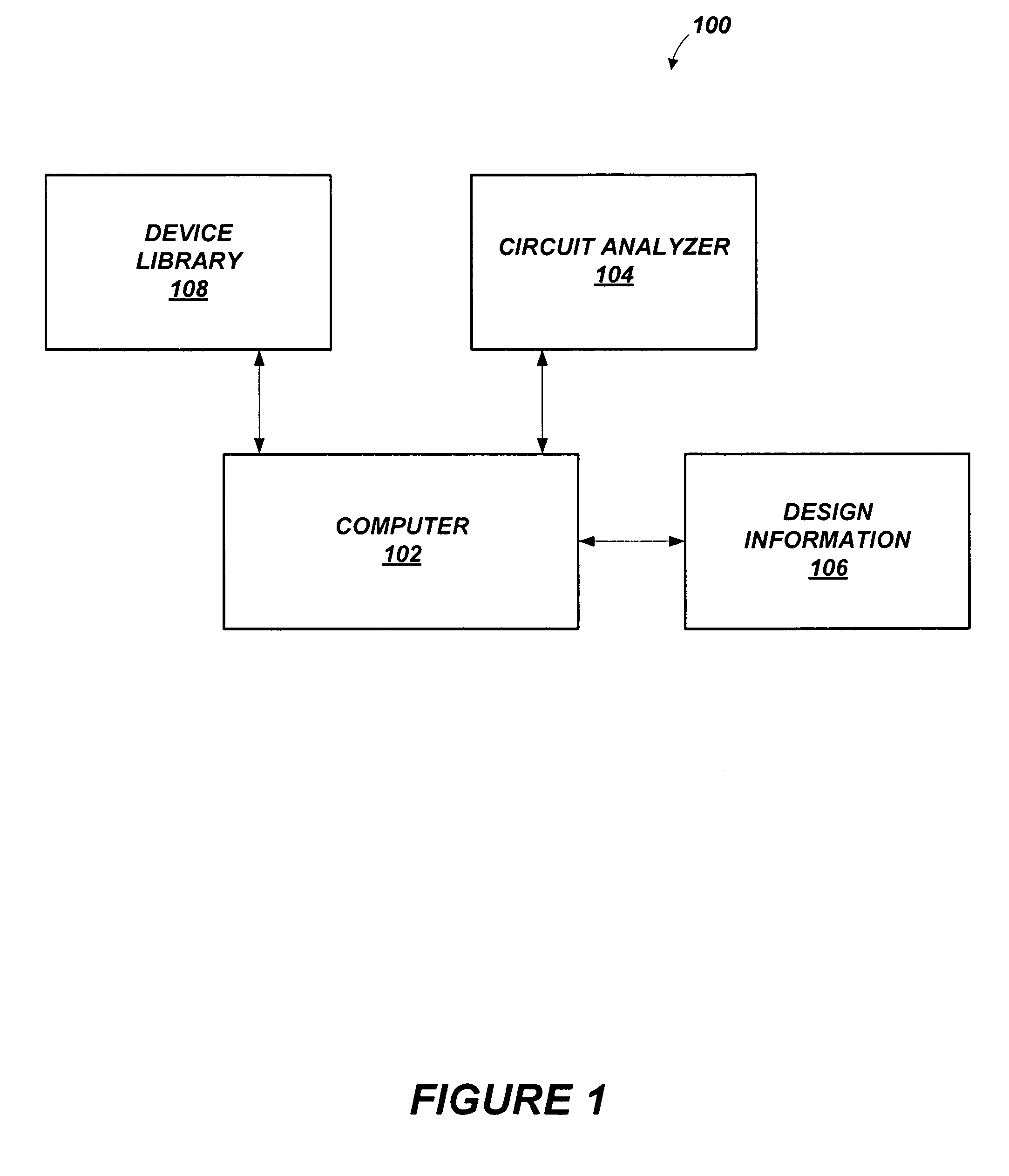

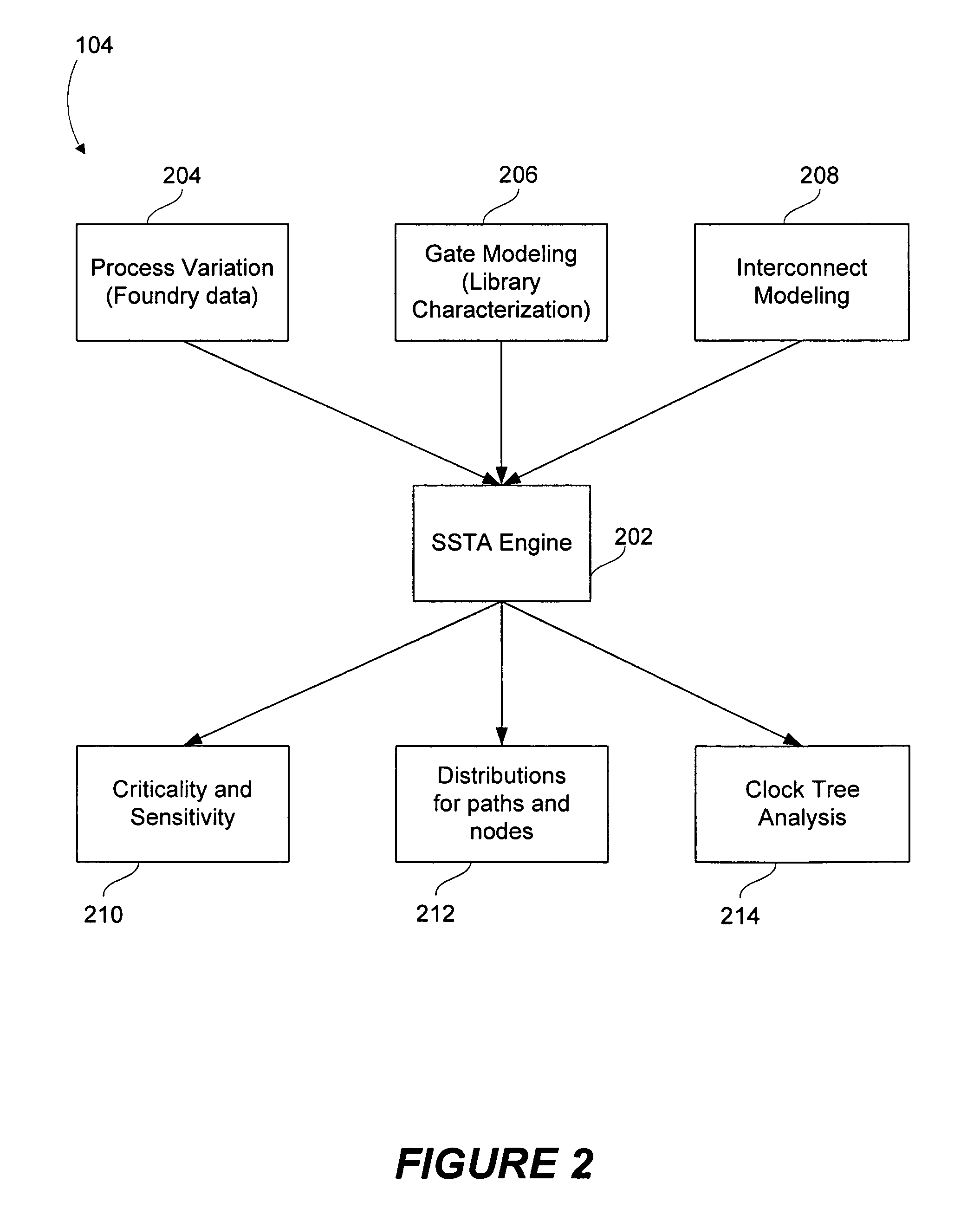

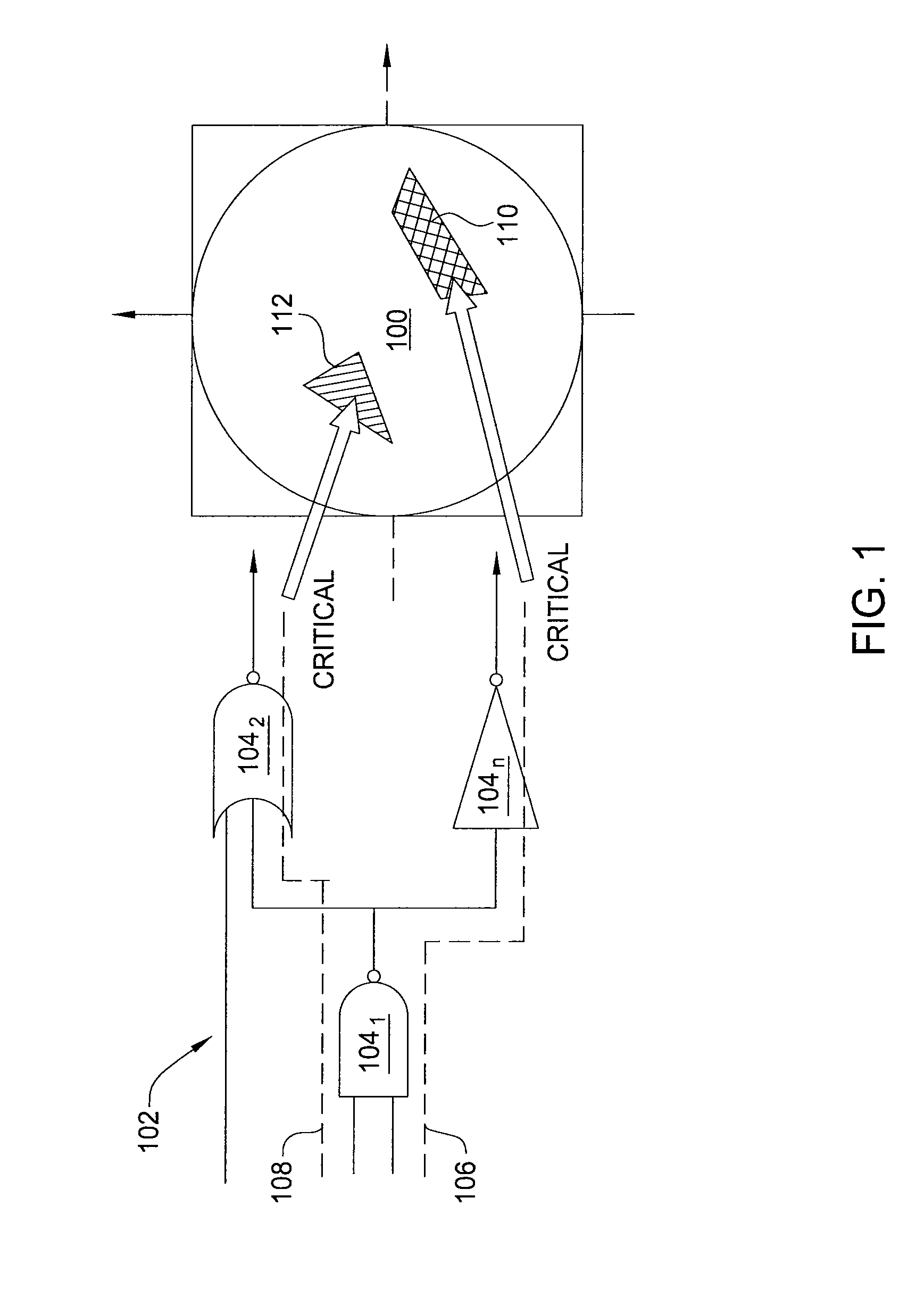

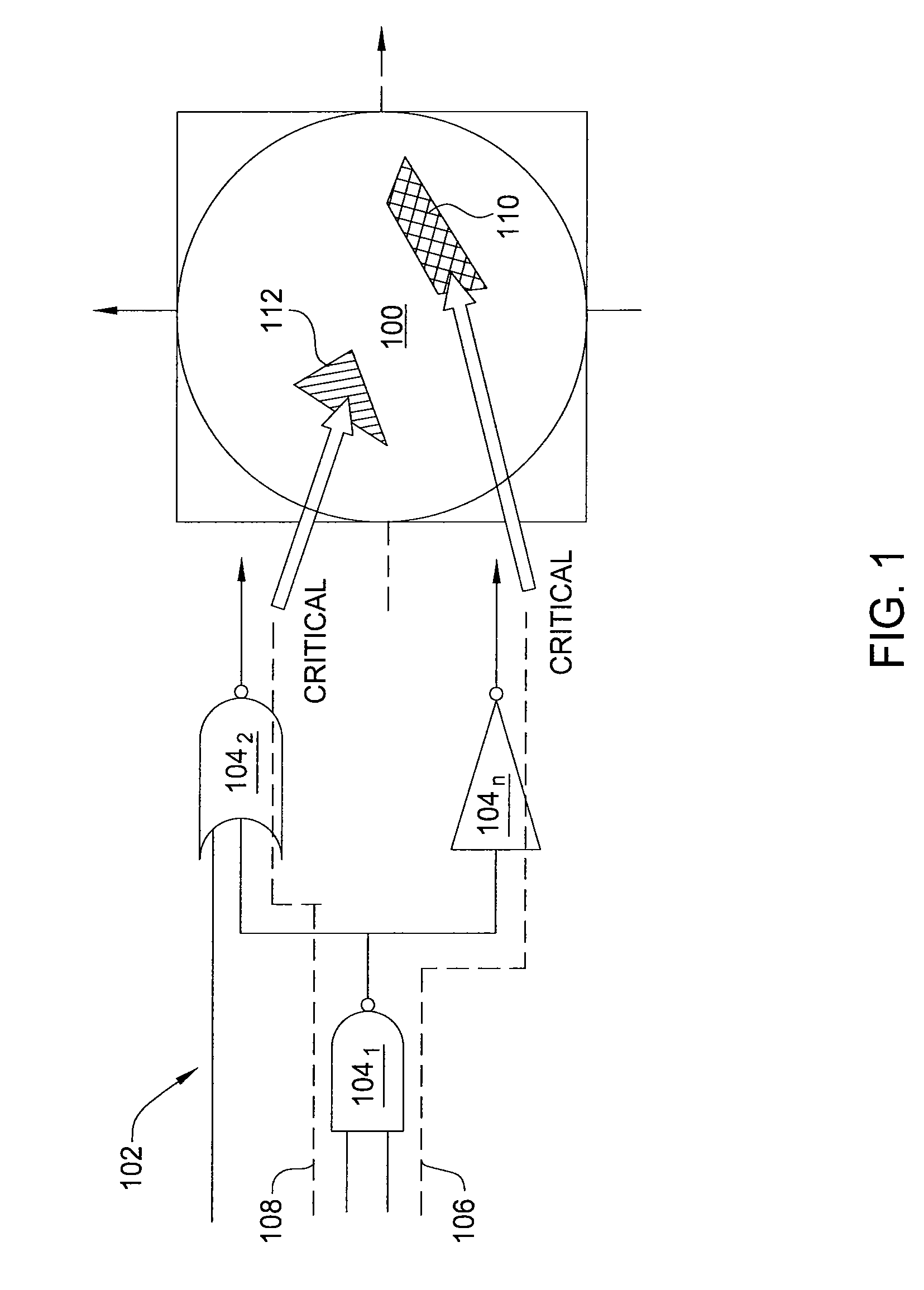

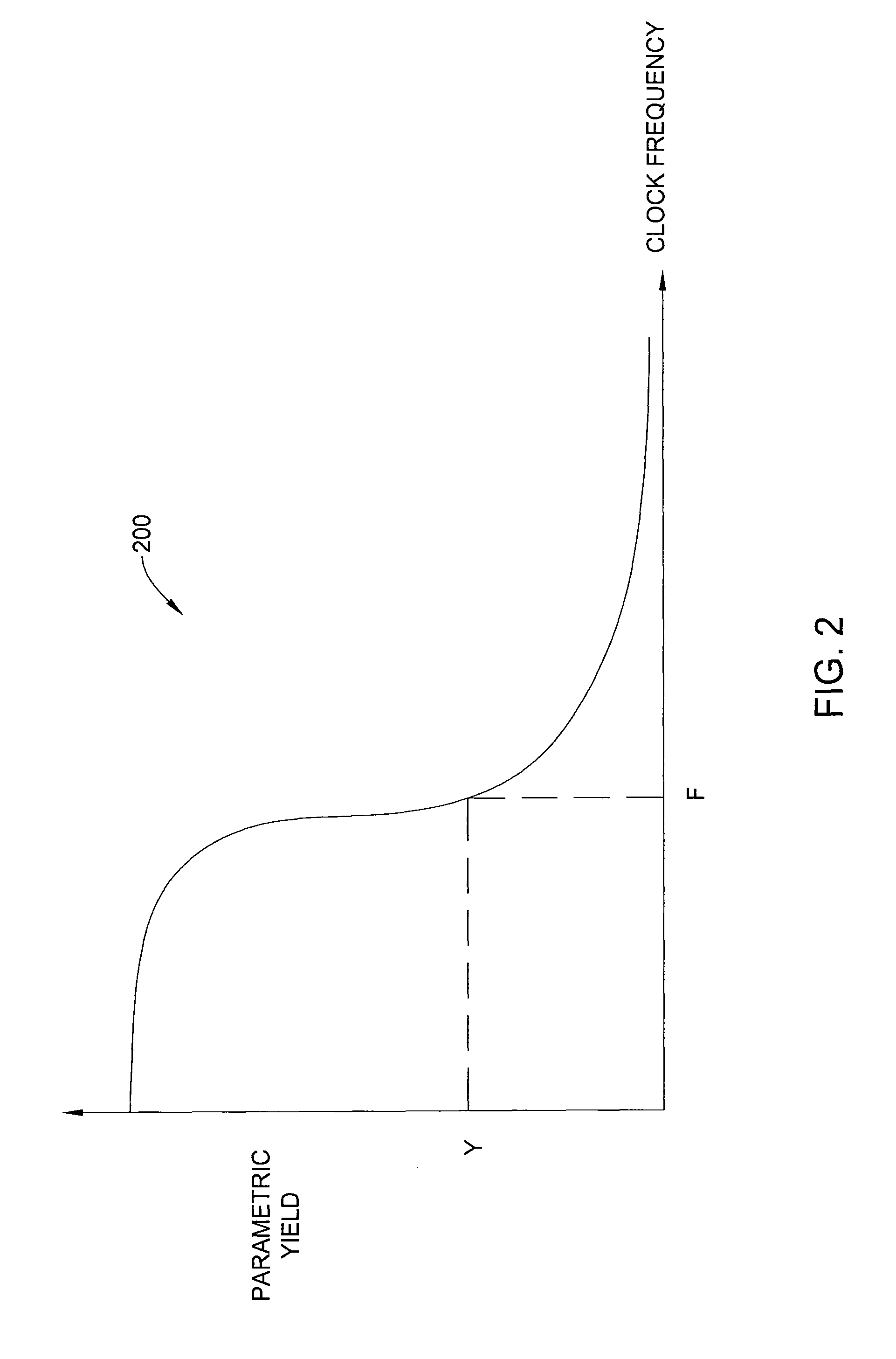

Aggregate sensitivity for statistical static timing analysis

ActiveUS7458049B1Analogue computers for electric apparatusComputation using non-denominational number representationCircuit modelingTime distribution

A system and a method are disclosed for circuit analysis. A circuit modeling system calculates sensitivities of gates for statistical static timing analysis of a circuit. Timing distribution sensitivities of gates and correlations between the sensitivities are determined. A Monte Carlo simulation is run using the sensitivities to determine timing distribution of paths and determine probabilities of paths being the critical path. Aggregate sensitivities for cells are also determined.

Owner:SYNOPSYS INC

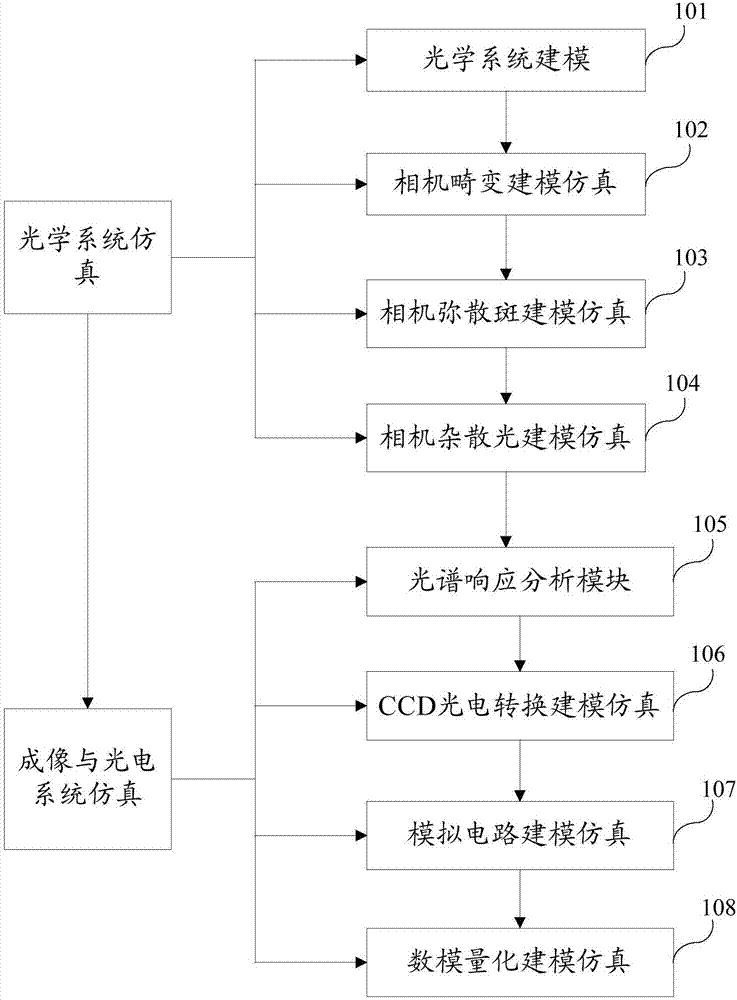

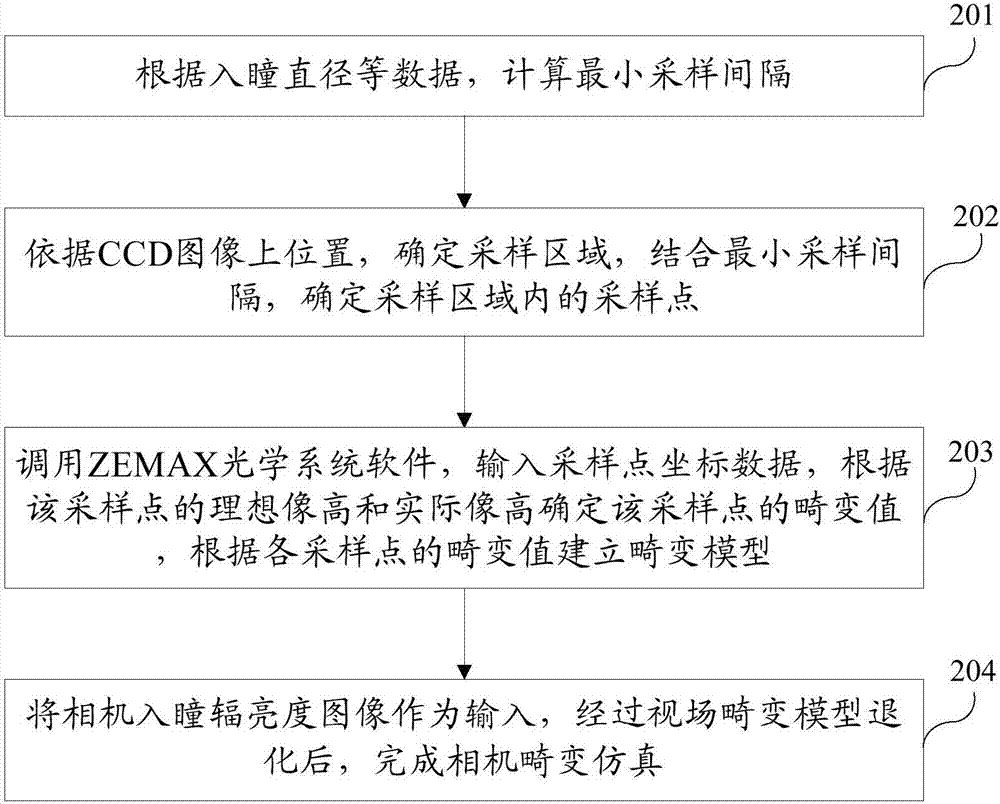

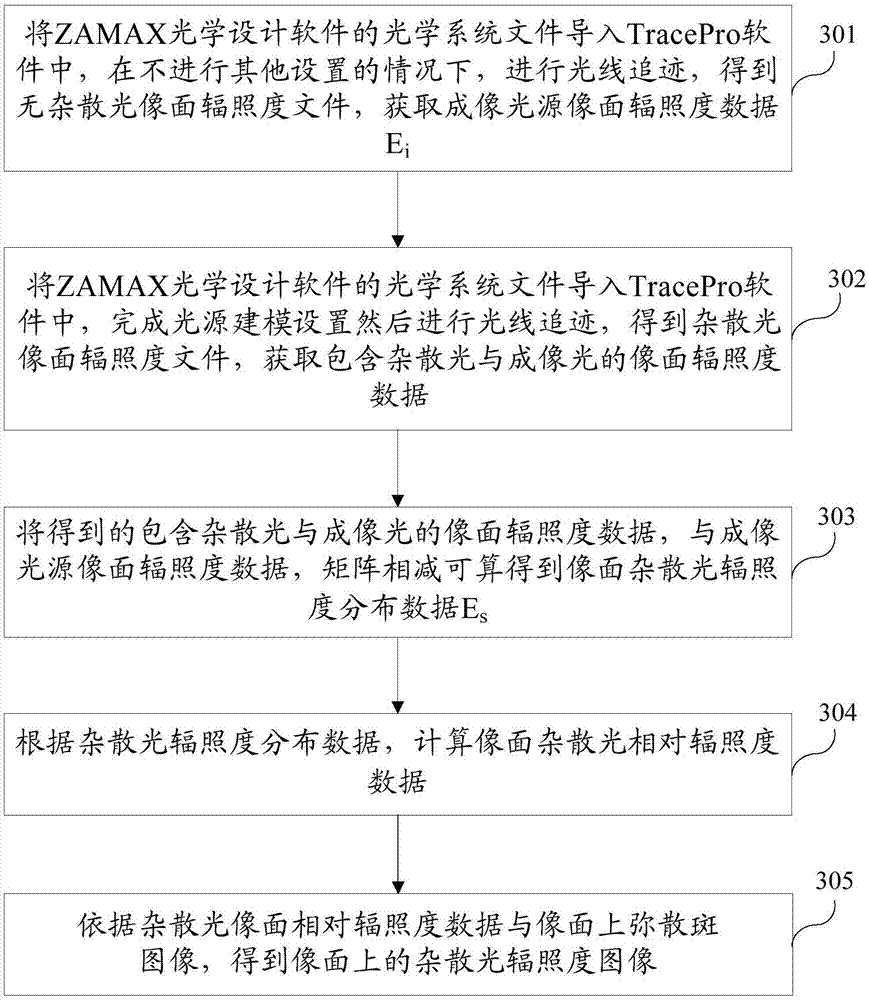

Ray tracing-based optical camera simulation imaging method and system

ActiveCN107092752AHigh closenessImprove simulation accuracyTelevision system detailsColor television detailsStray lightResponse analysis

The invention discloses a ray tracing-based optical camera simulation imaging method and system. The method comprises optical system simulation, and imaging and photoelectric system simulation, wherein the optical system simulation comprises optical system modeling, camera distortion modeling simulation, camera defocused spot modeling simulation and camera stray light modeling simulation; and the imaging and photoelectric system simulation comprises a spectrum response analysis module, CCD photoelectric conversion modeling simulation, analog circuit modeling simulation and digital-analog quantification modeling simulation. According to the method and the system, influence factors of an optical system and a CCD imaging system of a remote sensing camera to an imaging result are comprehensively considered; a detailed and complete remote sensing camera parameter database is established; a simulated image and a real image have higher close degree; and relatively high simulation precision is achieved.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

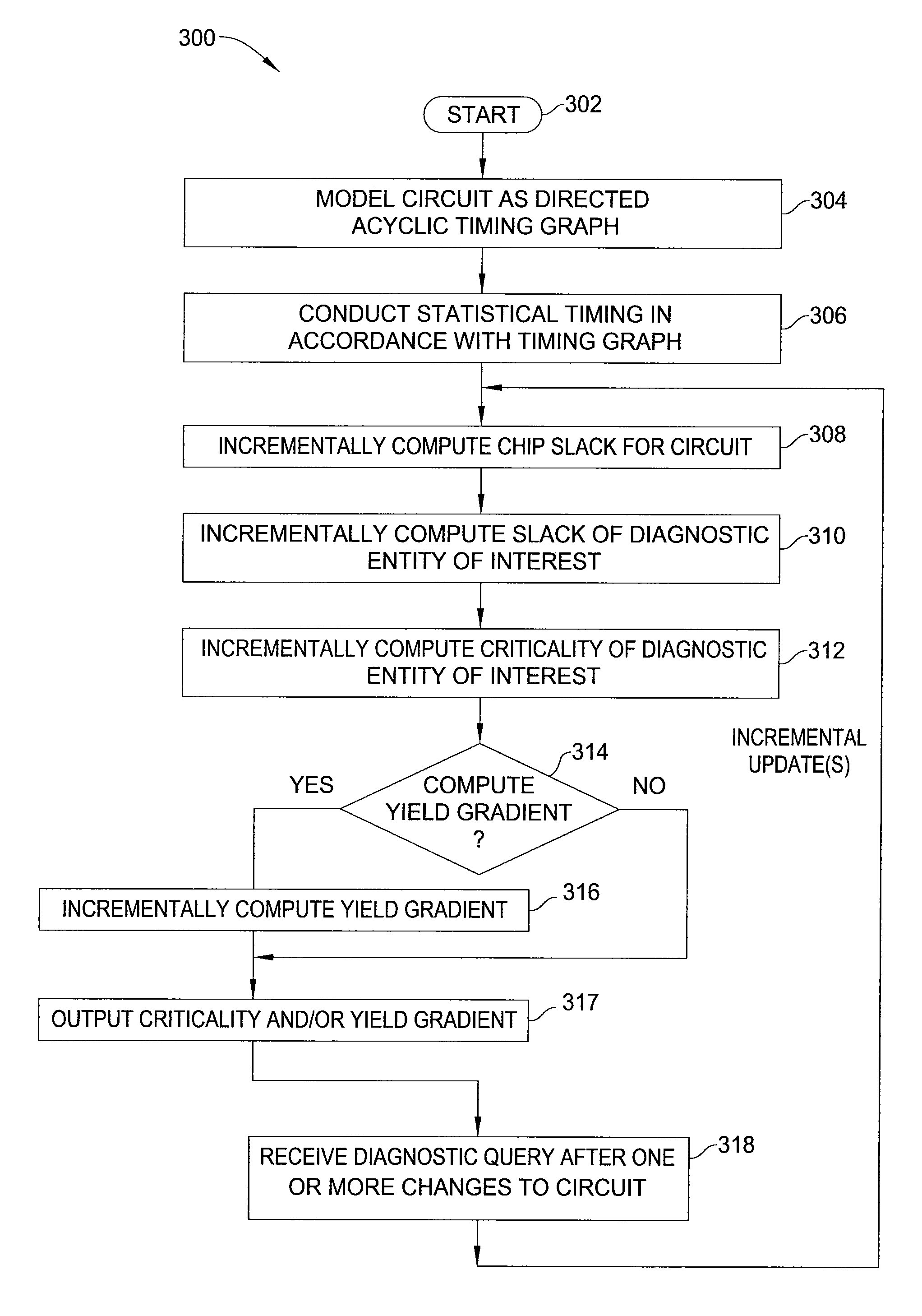

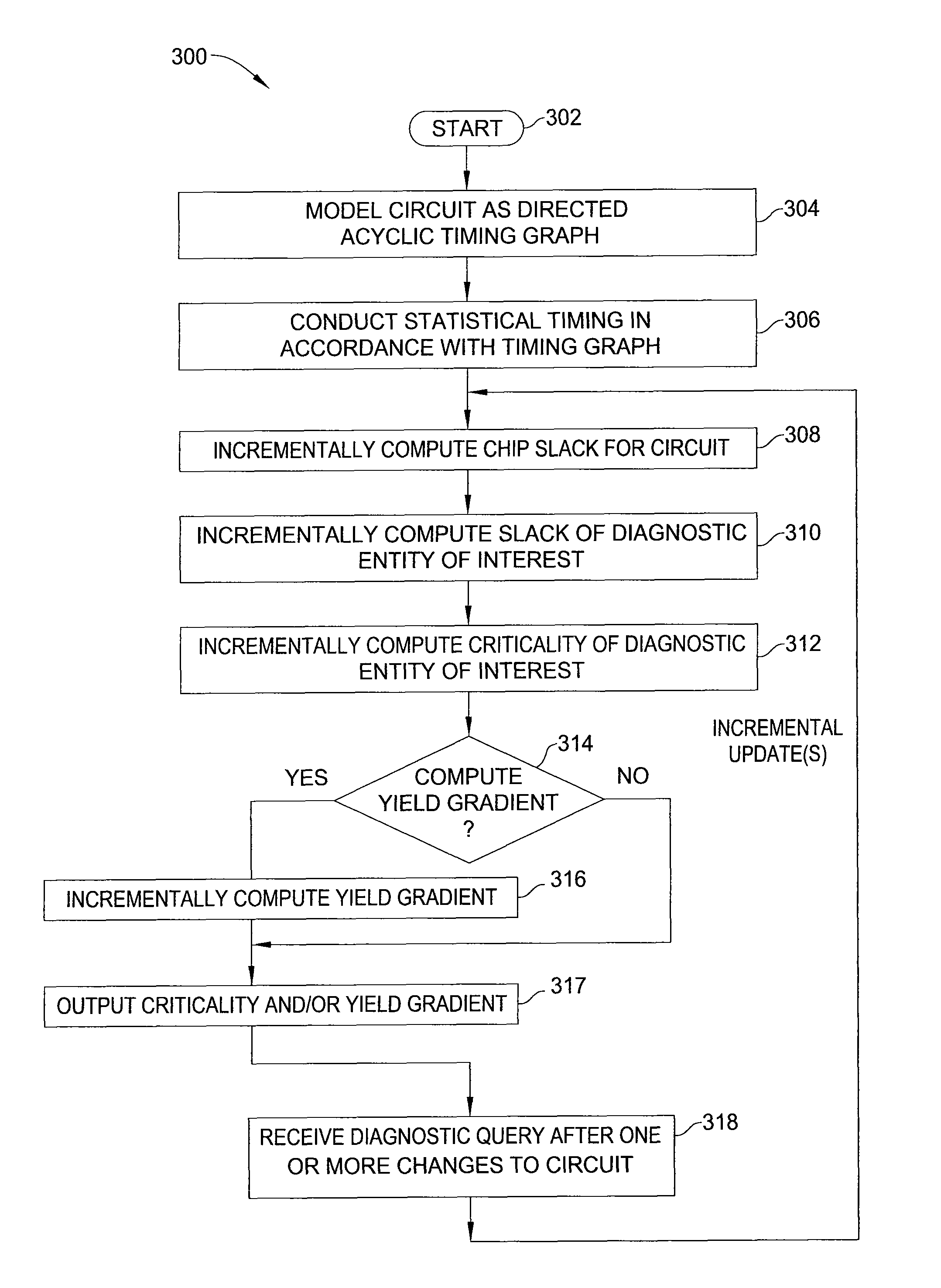

Method and apparatus for incrementally computing criticality and yield gradient

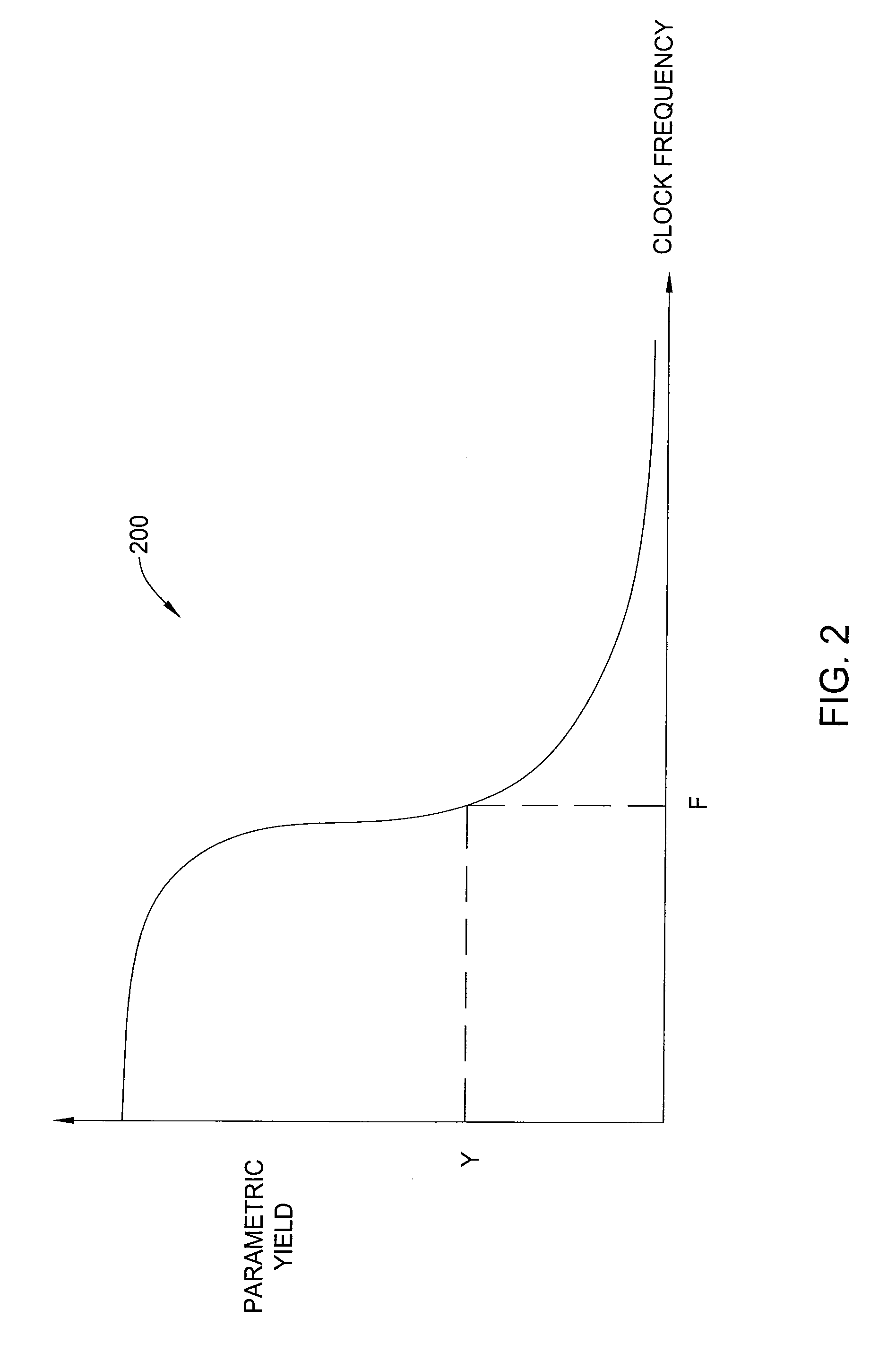

In one embodiment, the invention is a method and apparatus for incrementally computing criticality and yield gradient. One embodiment of a method for computing a diagnostic metric for a circuit includes modeling the circuit as a timing graph, determining a chip slack for the circuit, determining a slack of at least one diagnostic entity, and computing a diagnostic metric relating to the diagnostic entity(ies) from the chip slack and the slack of the diagnostic entity(ies).

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

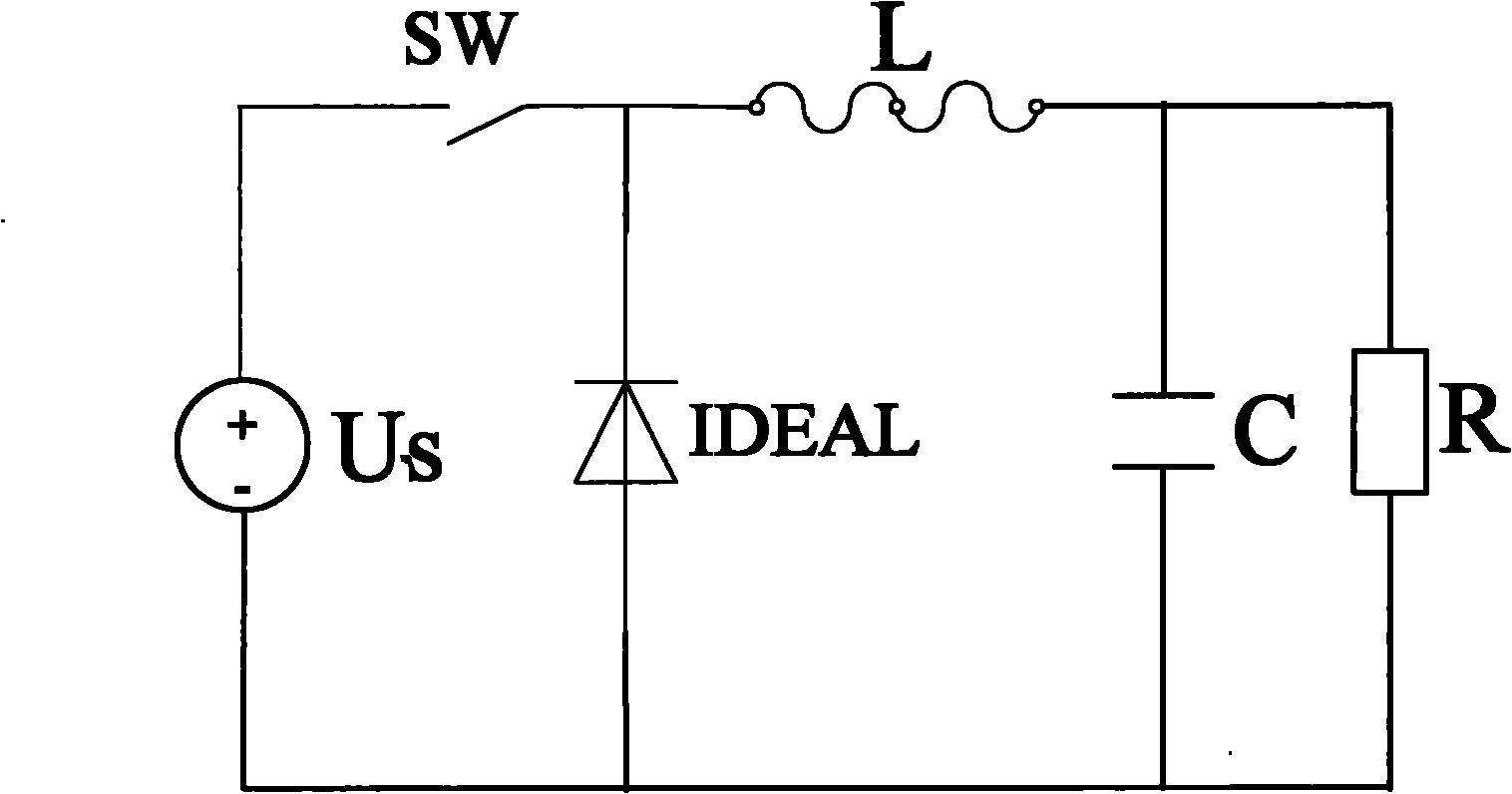

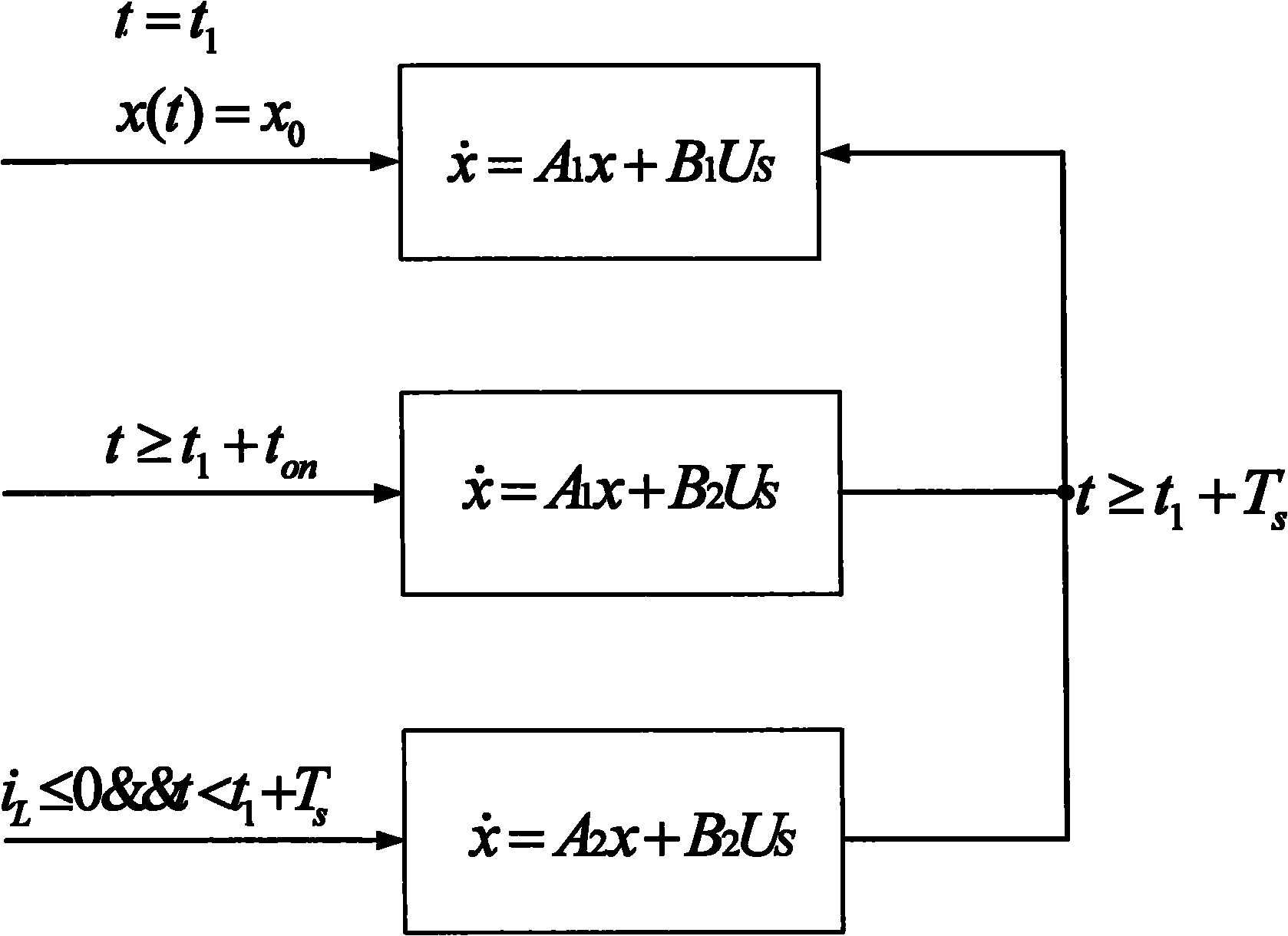

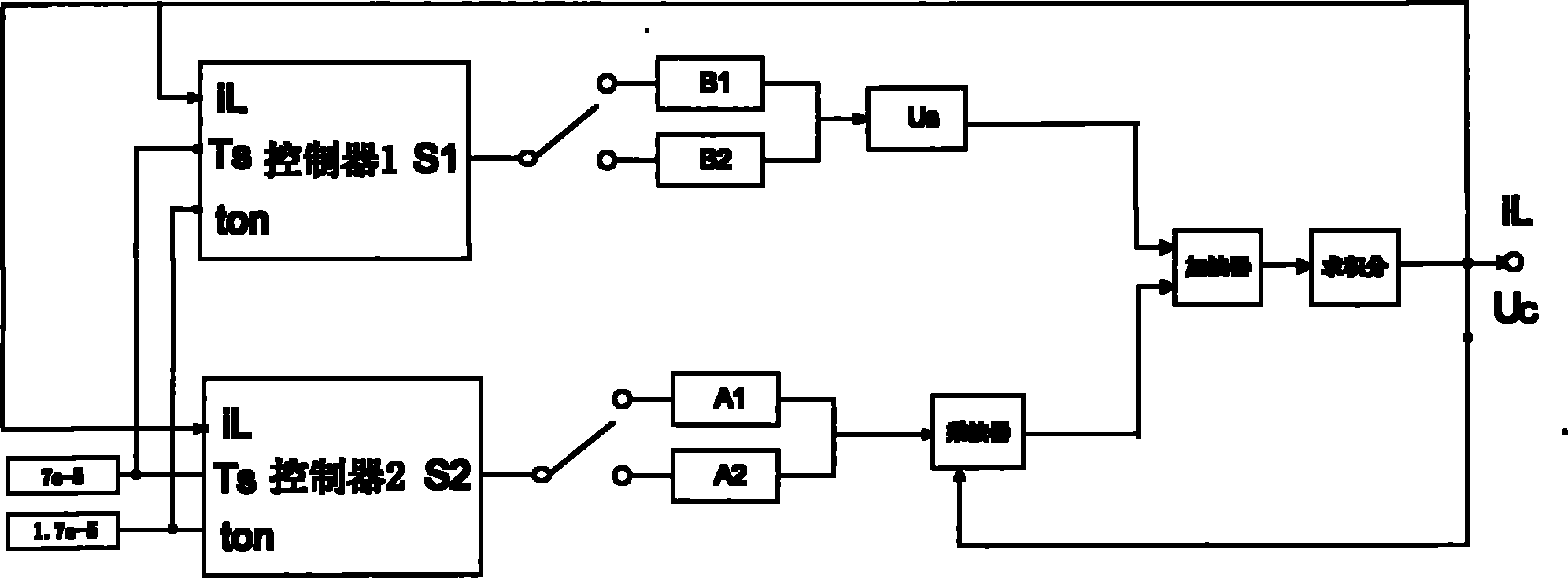

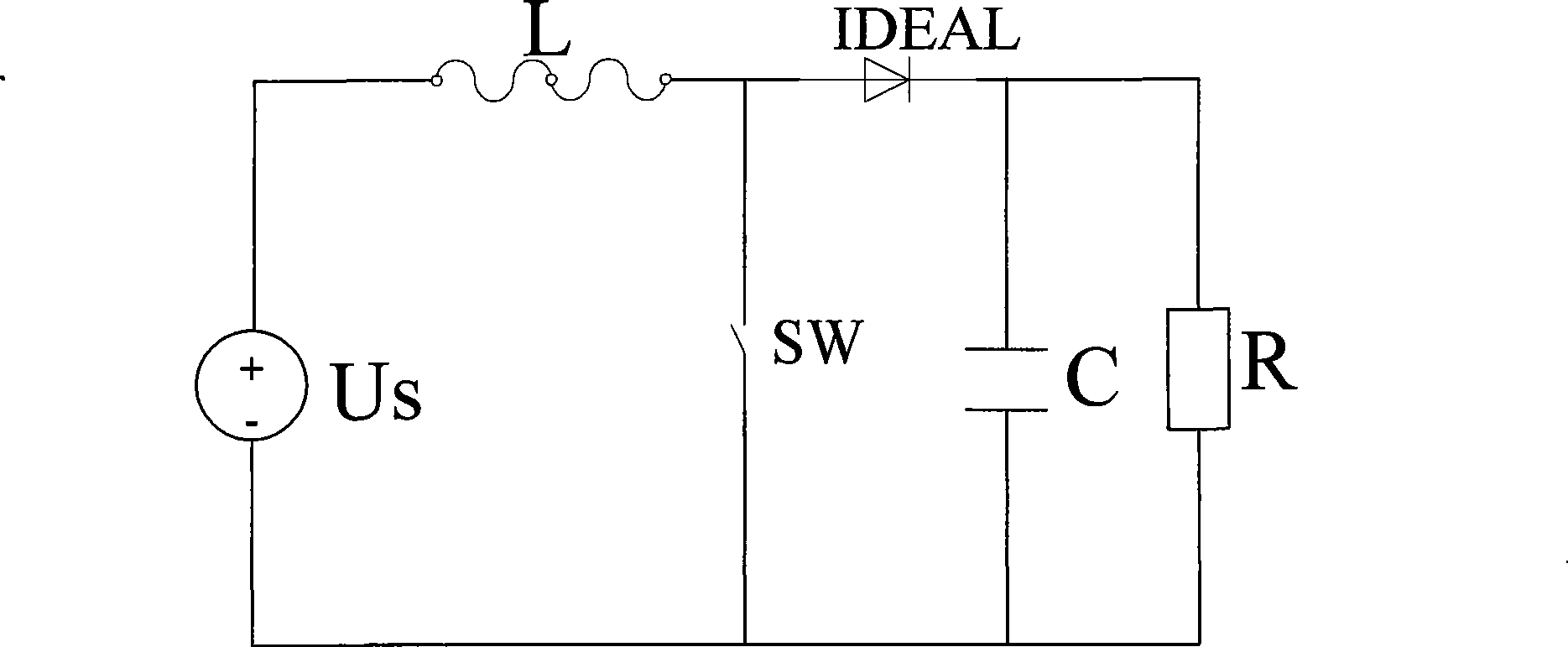

Hybrid switching system theory-based Buck circuit modeling method

InactiveCN101980219ASimple structureReduce volumeSpecial data processing applicationsCircuit modelingState space

The invention discloses a hybrid switching system theory-based Buck circuit modeling method and application thereof. The method comprises the following working steps of: 1, analyzing a Buck circuit, portioning a state space, and determining the number of working states; 2, determining switching conditions among the working states; 3, establishing a sate equation and an output equation of the Buck circuit; 4, determining a state matrix, an input matrix and an output matrix of a system according to circuit parameters; and 5, establishing a model of the Buck circuit based on the hybrid switching system theory. By utilizing the hybrid switching system theory, the modeling of the Buck circuit is accurate, and system stability and control performance are accurately analyzed, particularly complicated characteristics of a converter system caused by switching; and the Buck circuit has the advantages of simple structure, small volume, high conversion efficiency and the like.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

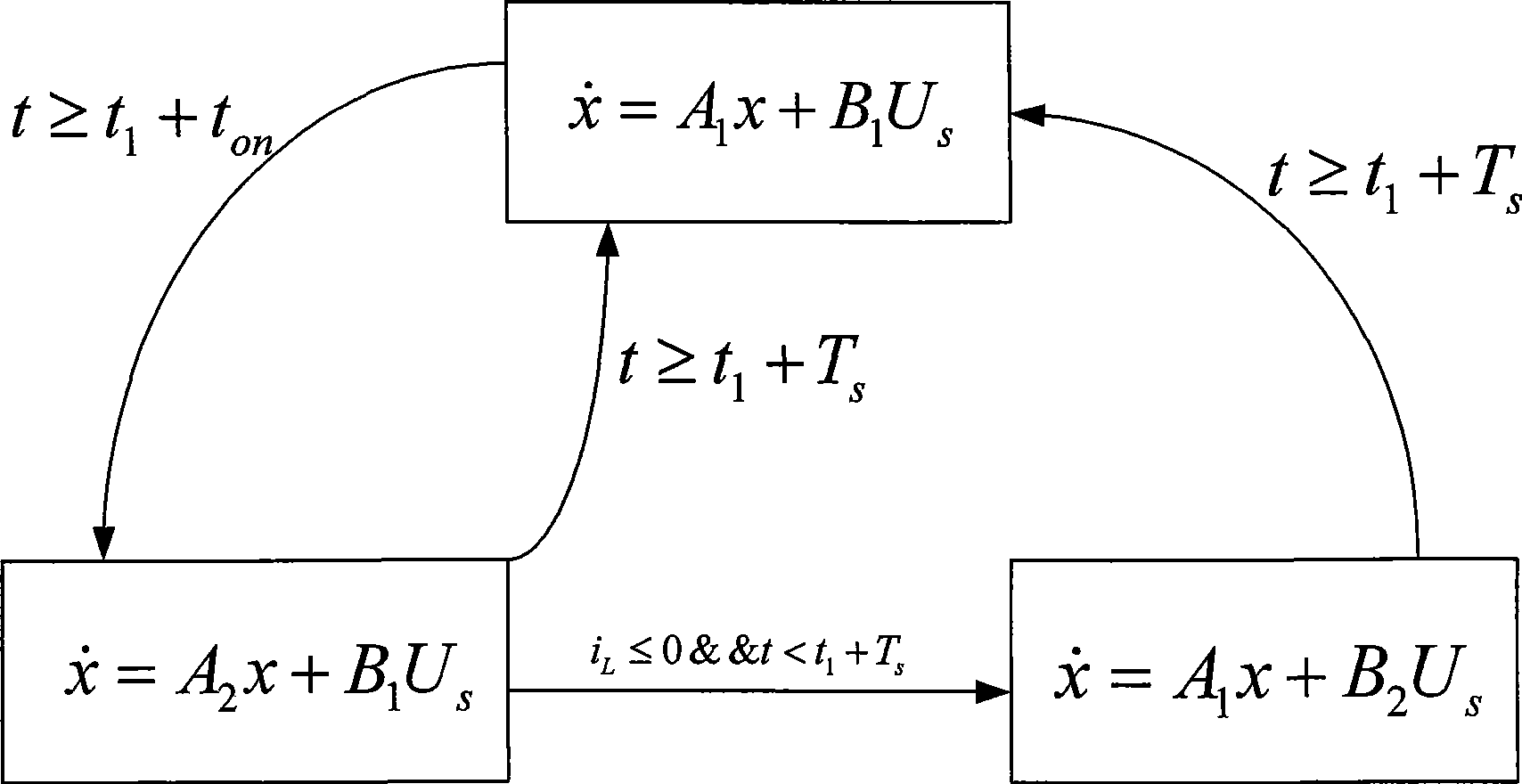

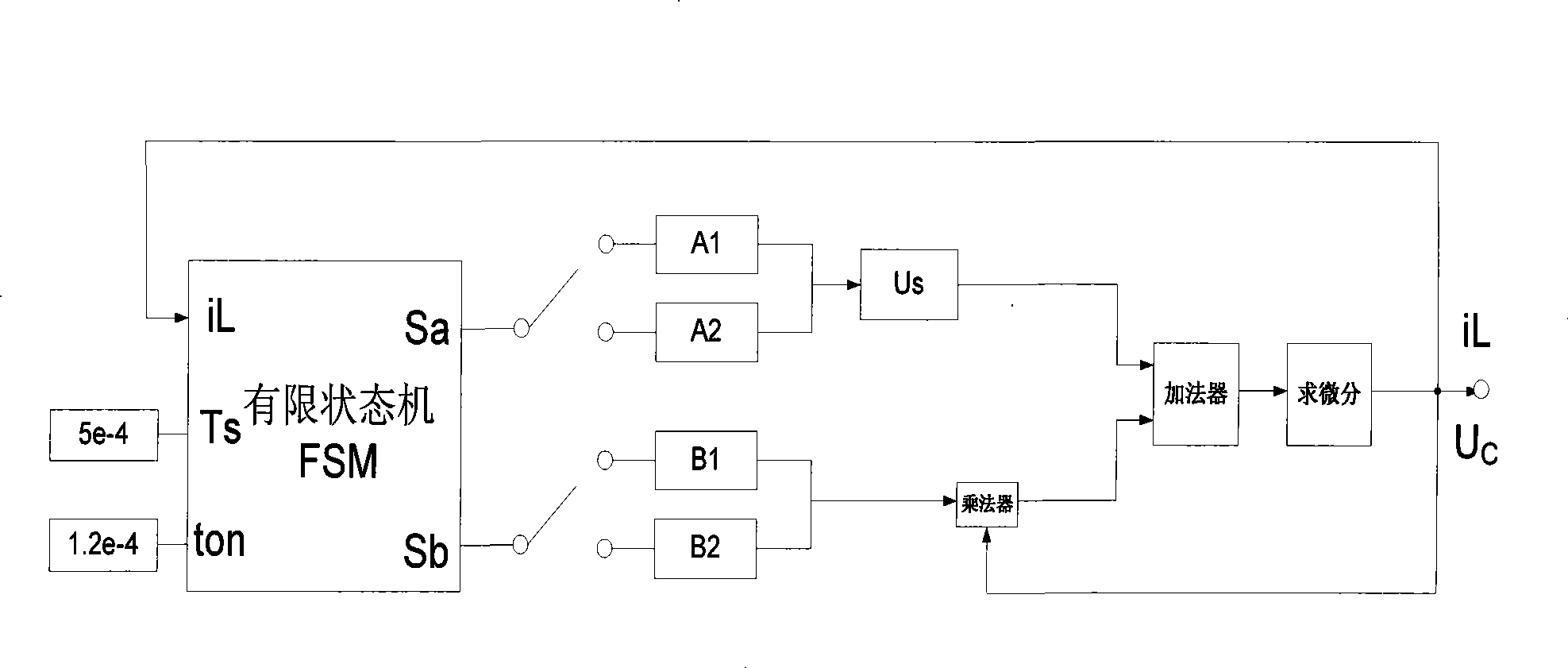

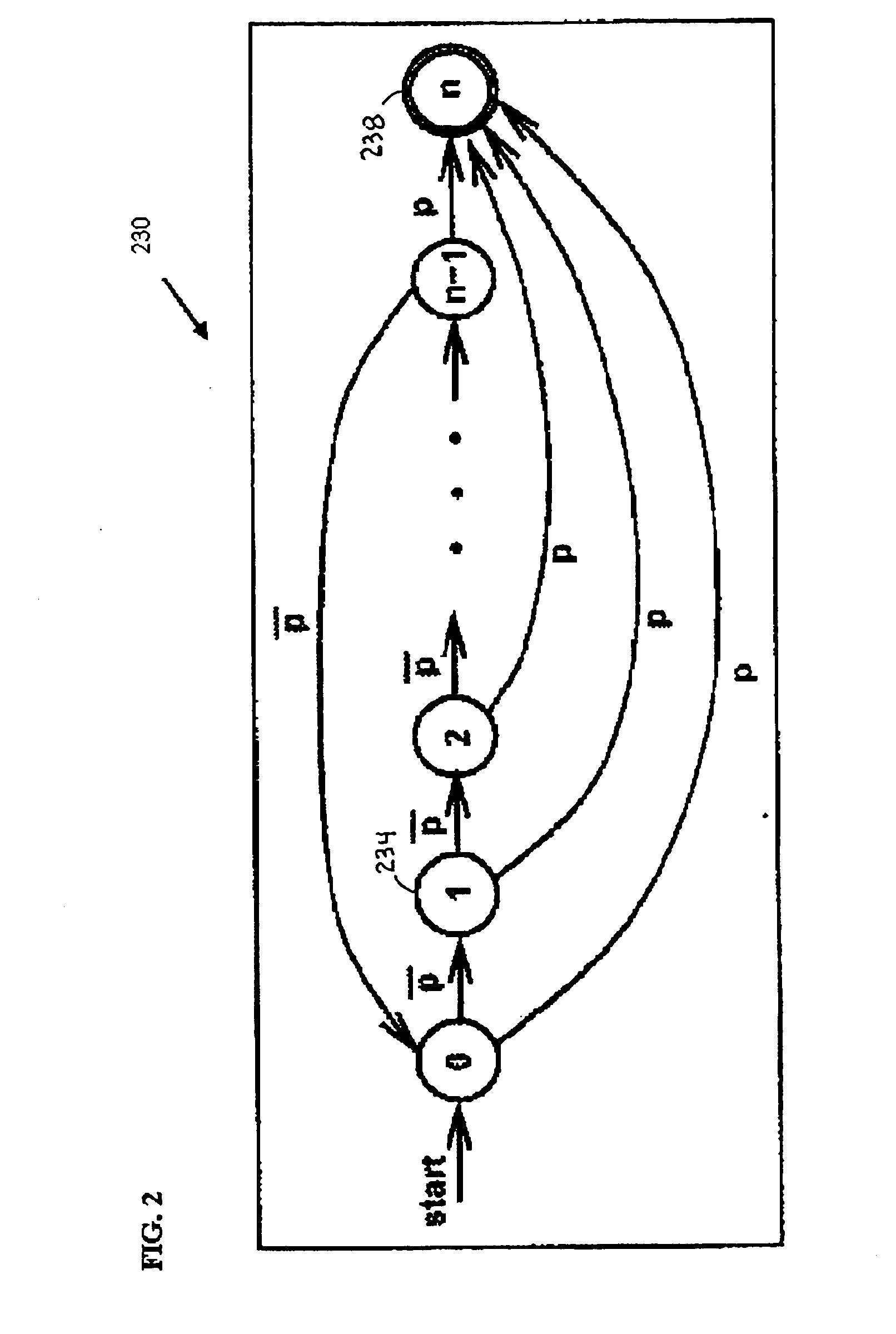

Boost circuit modeling approach and use thereof based on finite state machine

InactiveCN101393578AEffective modelingReduce volumeSpecial data processing applicationsCircuit modelingVirtual finite-state machine

The invention provides a finite state machine-based Boost circuit modeling method and application thereof. The modeling method is characterized by comprising the following steps: (1) determining the number of operational states; (2) determining conversion conditions among the operational states; (3) establishing a mathematical equation; (4) determining a matrix according to parameters; and (5) building a model. The modeling method has the advantages that the Boost circuit model built by using the finite state machine is very precise and is easy to analyze the control characteristics of a system, especially a plurality of complicated characteristics caused by the switching of a switch in a converter system. The Boost circuit has the advantages of small volume, simple structure, high conversion efficiency and so on.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

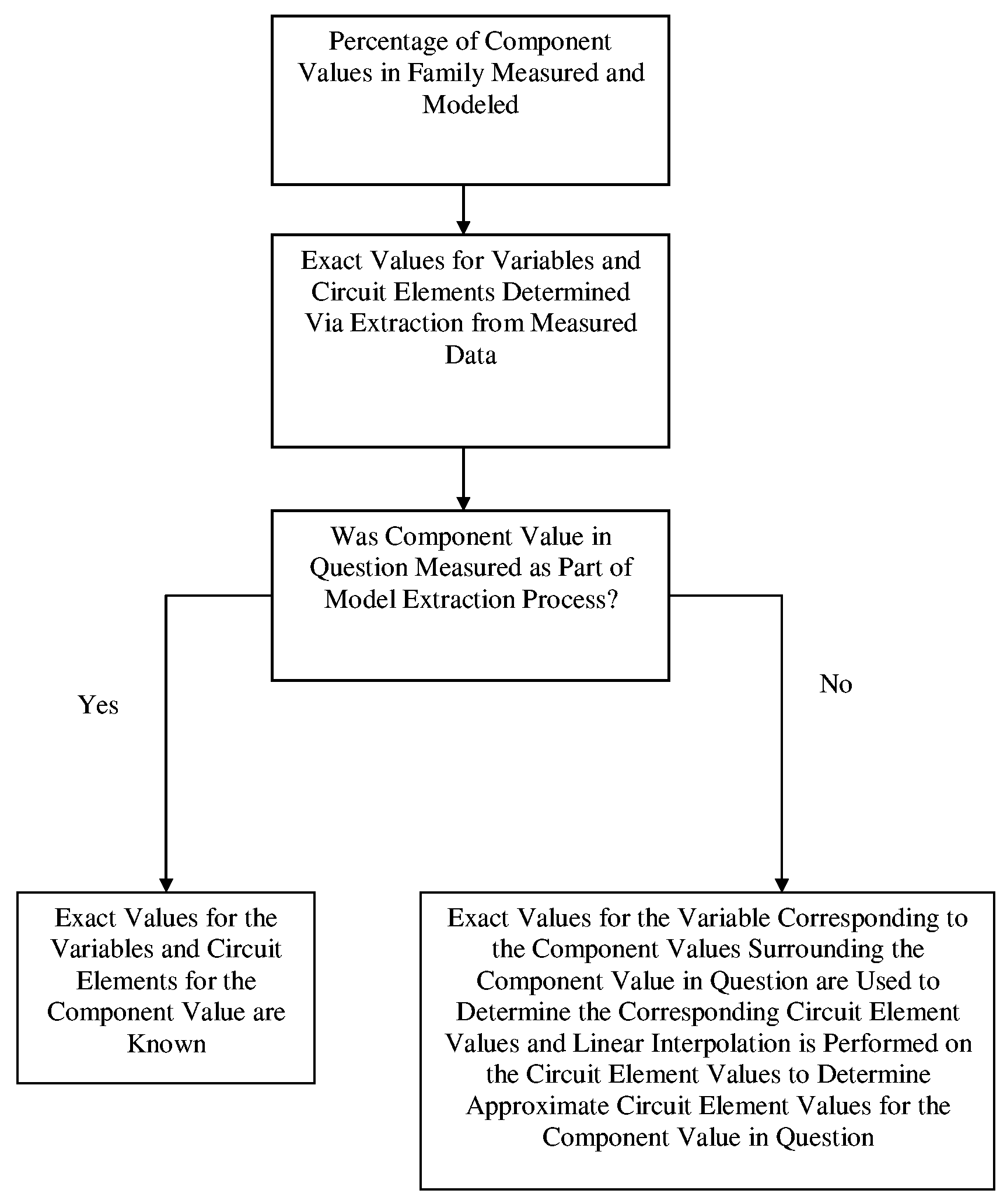

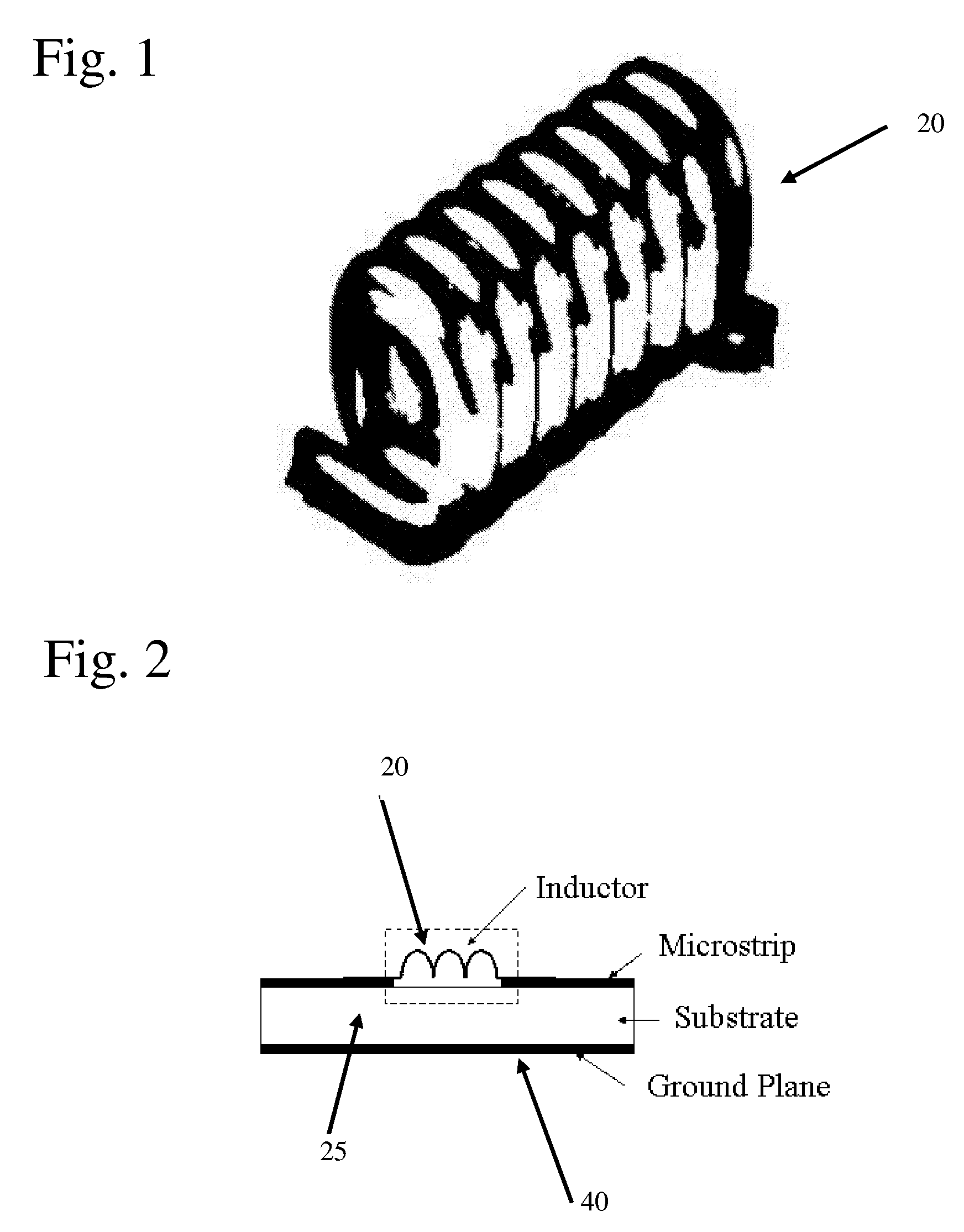

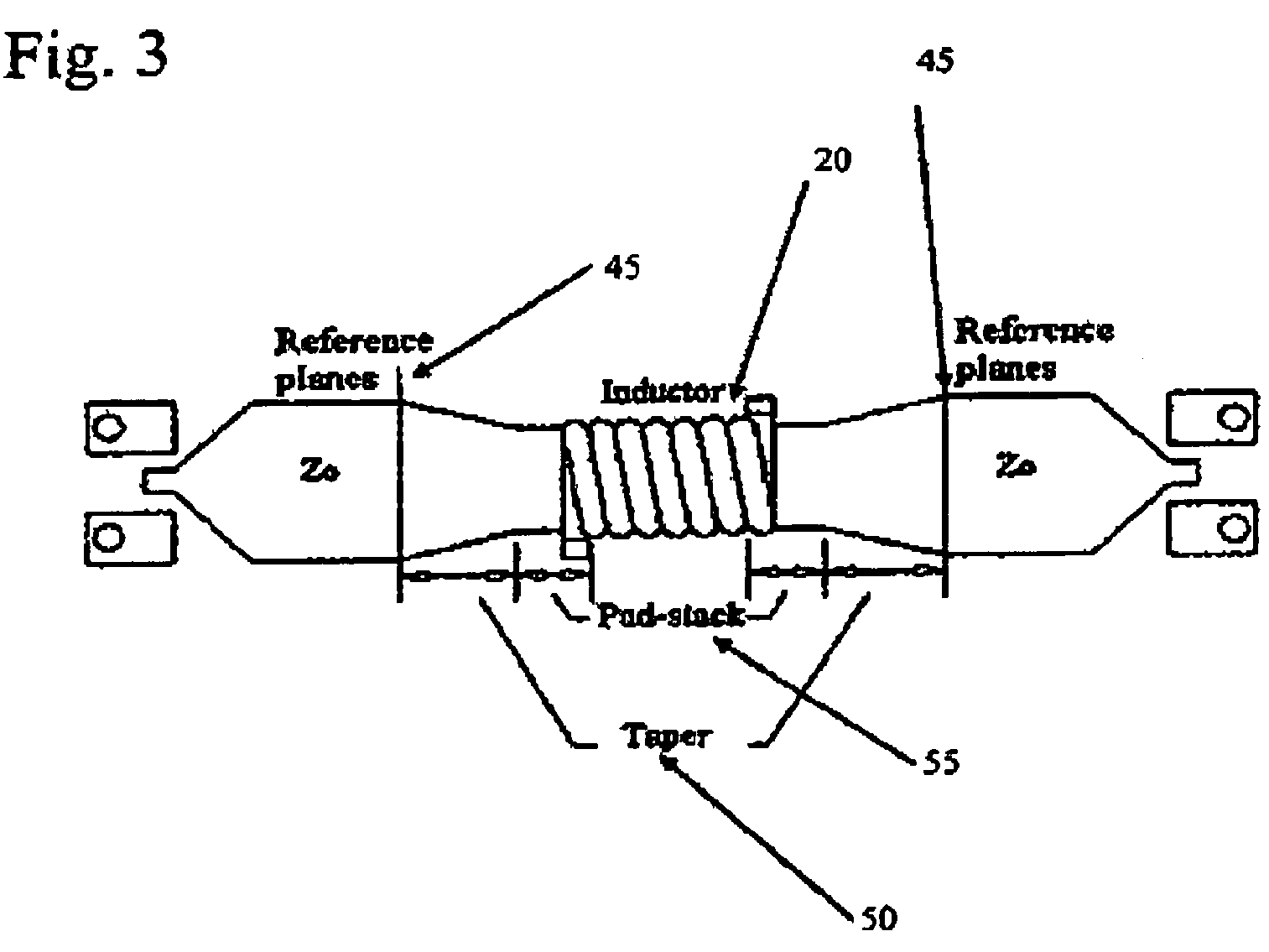

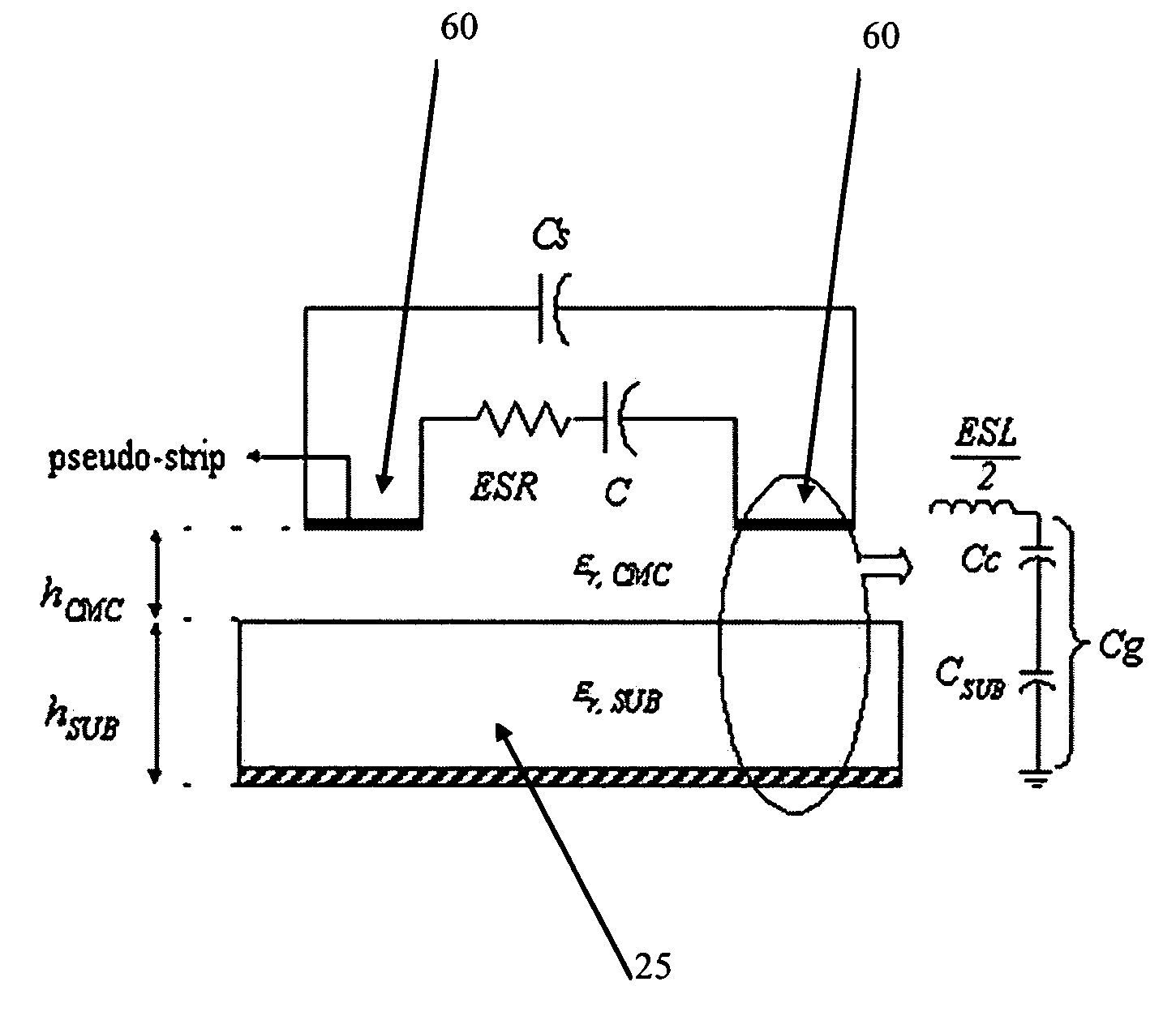

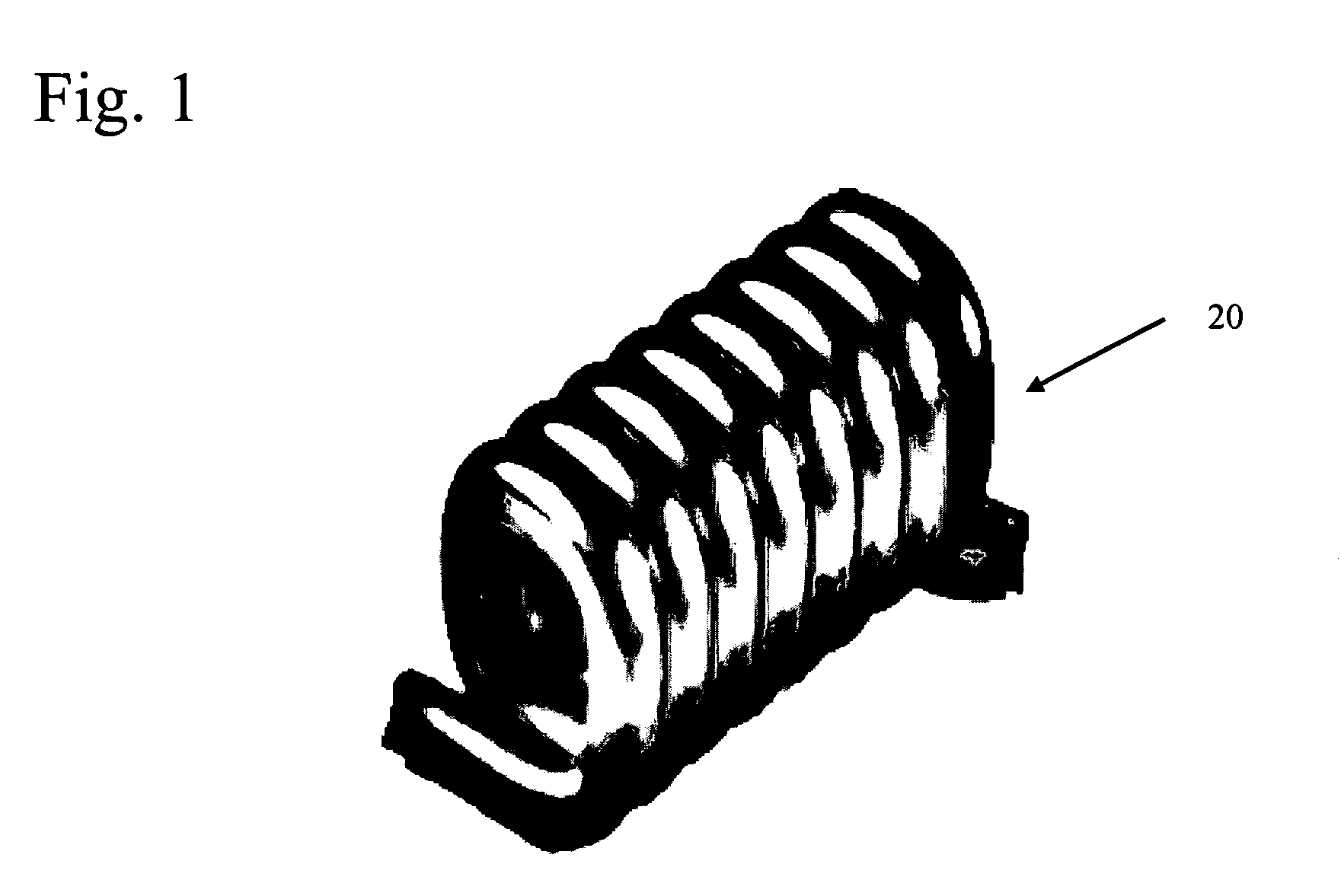

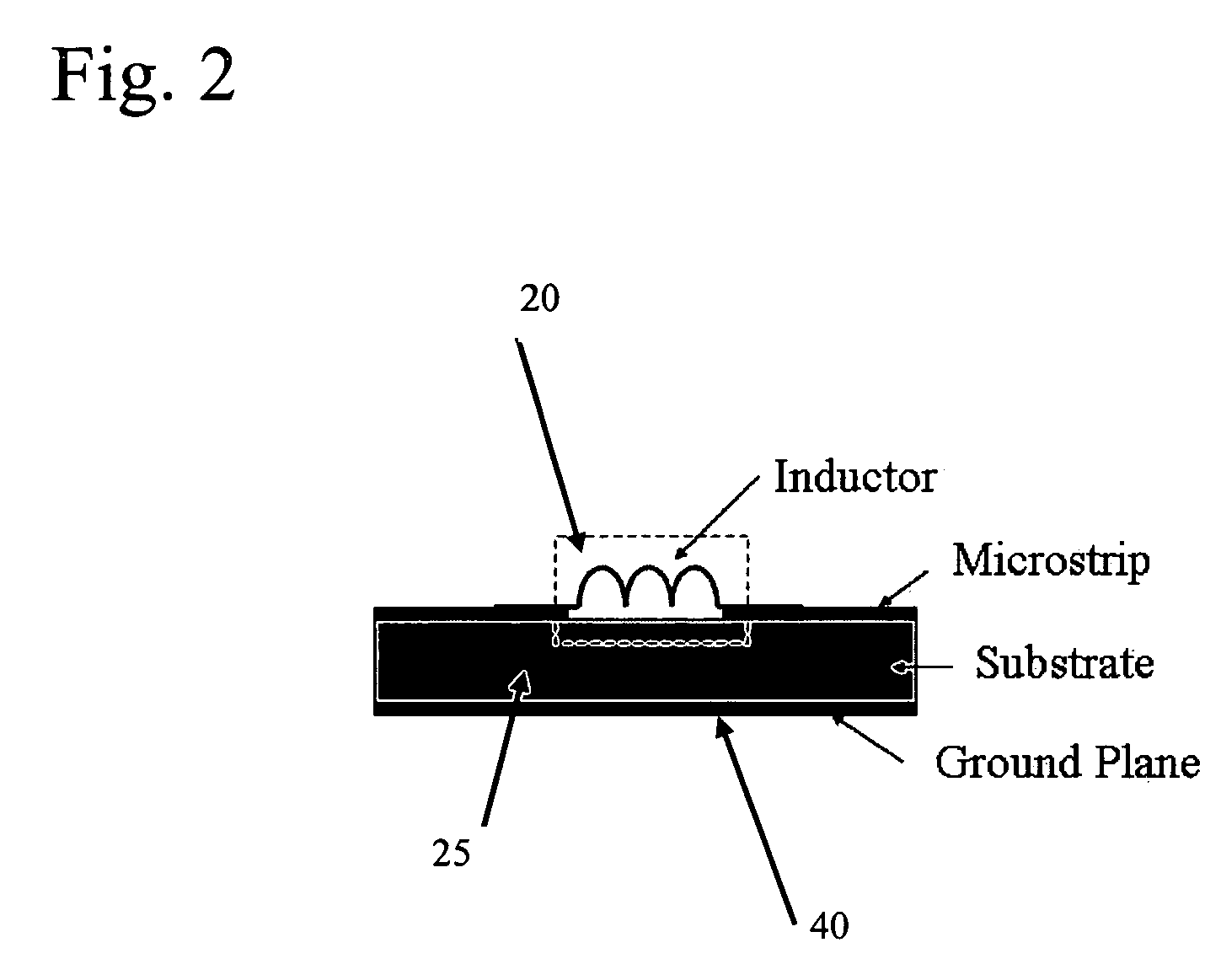

Global equivalent circuit modeling system for substrate mounted circuit components incorporating substrate dependent characteristics

InactiveUS7269810B1Accurately frequency performanceAccurate frequencyDetecting faulty computer hardwareCAD circuit designDielectricCircuit modeling

The present invention is a substrate dependent circuit modeling system for substrate-mounted components. The height and dielectric constant of a substrate have a significant impact on the frequency response of such components, and these effects cannot be treated independently from the circuit model. The equivalent circuit parameters in the model must be made to vary in accordance with changes in the substrate. The invention includes the steps of selecting a substrate mounted electrical circuit component for which an equivalent circuit model is desired, determining equivalent circuit model input parameters, wherein some of which are dependent upon characteristics of the substrate upon which the component is mounted, for the selected component, representing the selected electrical circuit component mounted upon the substrate as an equivalent electrical circuit, formulating mathematical expressions based upon the input parameters, and creating a unique equivalent circuit model for the component mounted upon the given substrate, the unique equivalent circuit model representing the mounting of the component upon the given substrate wherein the equivalent circuit model provides behavior and performance predictions of the component based upon the given substrate characteristics.

Owner:UNIV OF SOUTH FLORIDA

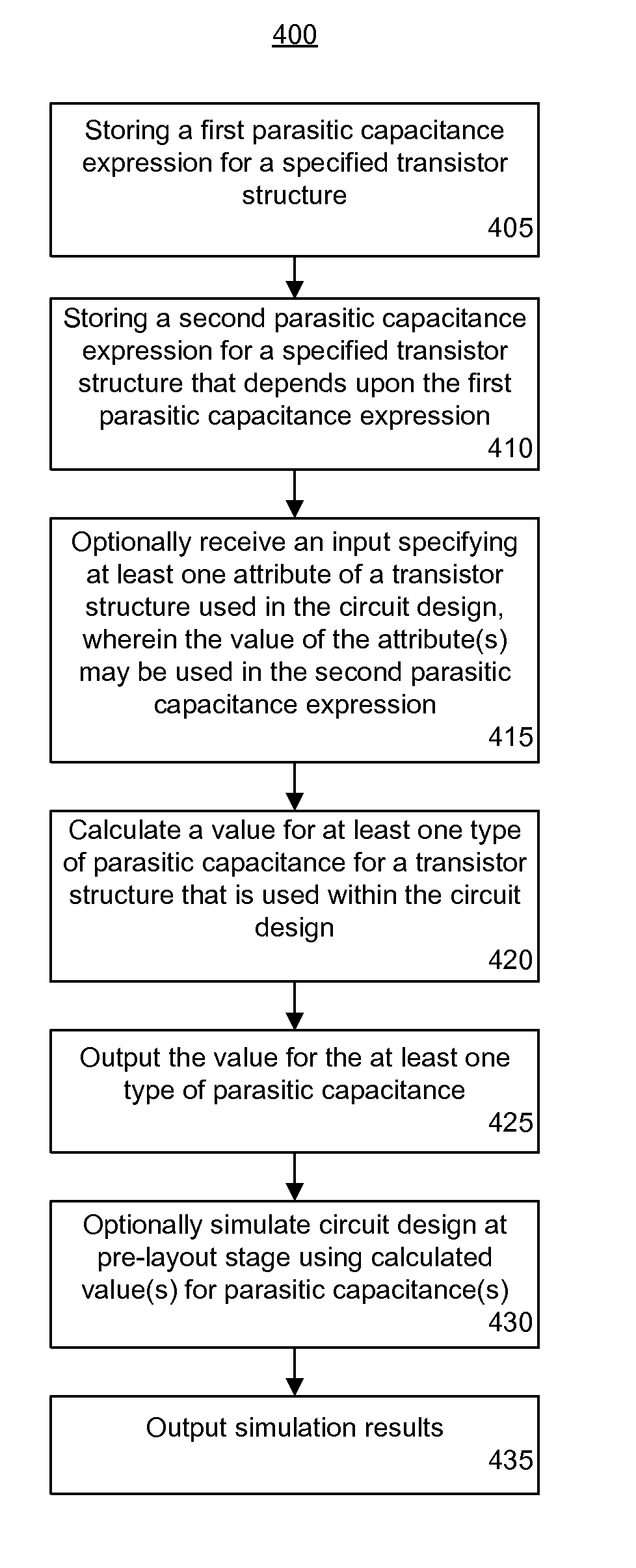

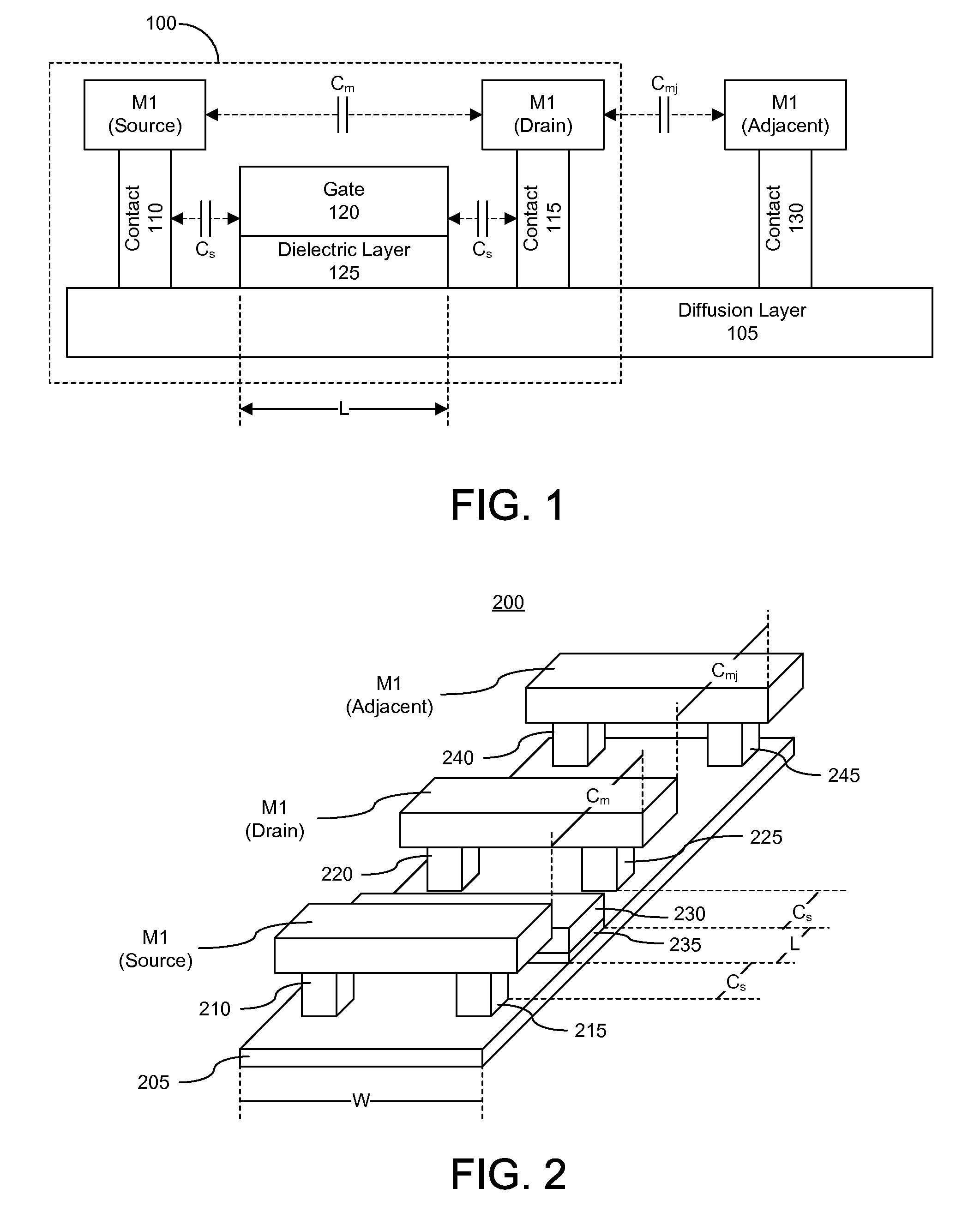

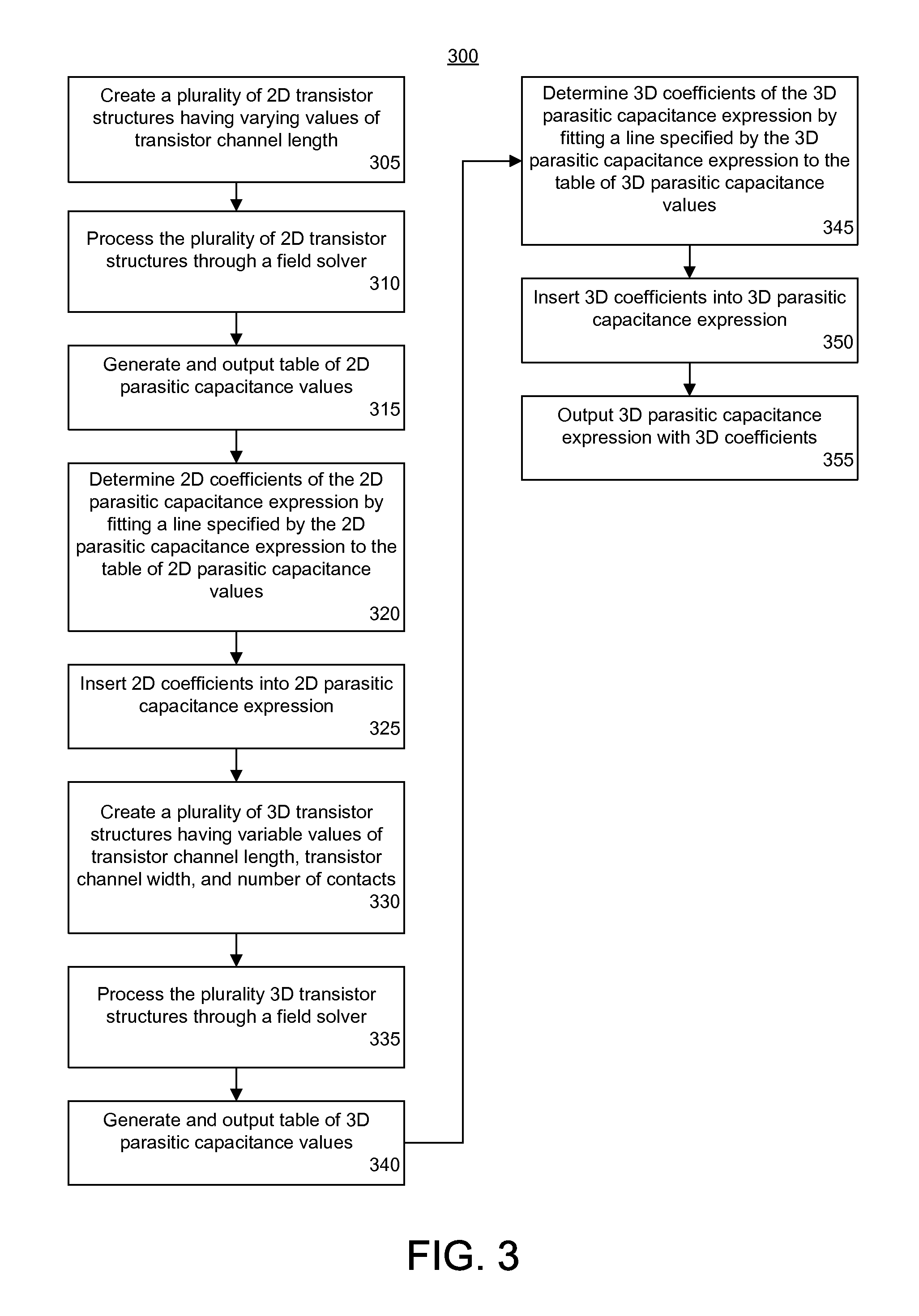

Predicting parasitic capacitance in schematic circuit simulations using sub-circuit modeling

ActiveUS8150638B1Computation using non-denominational number representationElectrical measurementsCircuit modelingParasitic capacitance

A computer-implemented method of determining parasitic capacitance for transistors within an integrated circuit can include determining a first set of coefficients for a first expression that calculates parasitic capacitance for a transistor structure according to a first plurality of parasitic capacitances derived from a plurality of two-dimensional transistor structures (320). The first set of coefficients can be inserted into the first expression (325). The method further can include determining a second set of coefficients for a second expression that calculates parasitic capacitance for a transistor structure according to a second plurality of parasitic capacitances derived from a plurality of three-dimensional transistor structures (345). The second expression can include the first expression (350). The method can include inserting the second set of coefficients into the second expression and outputting the second expression (355).

Owner:XILINX INC

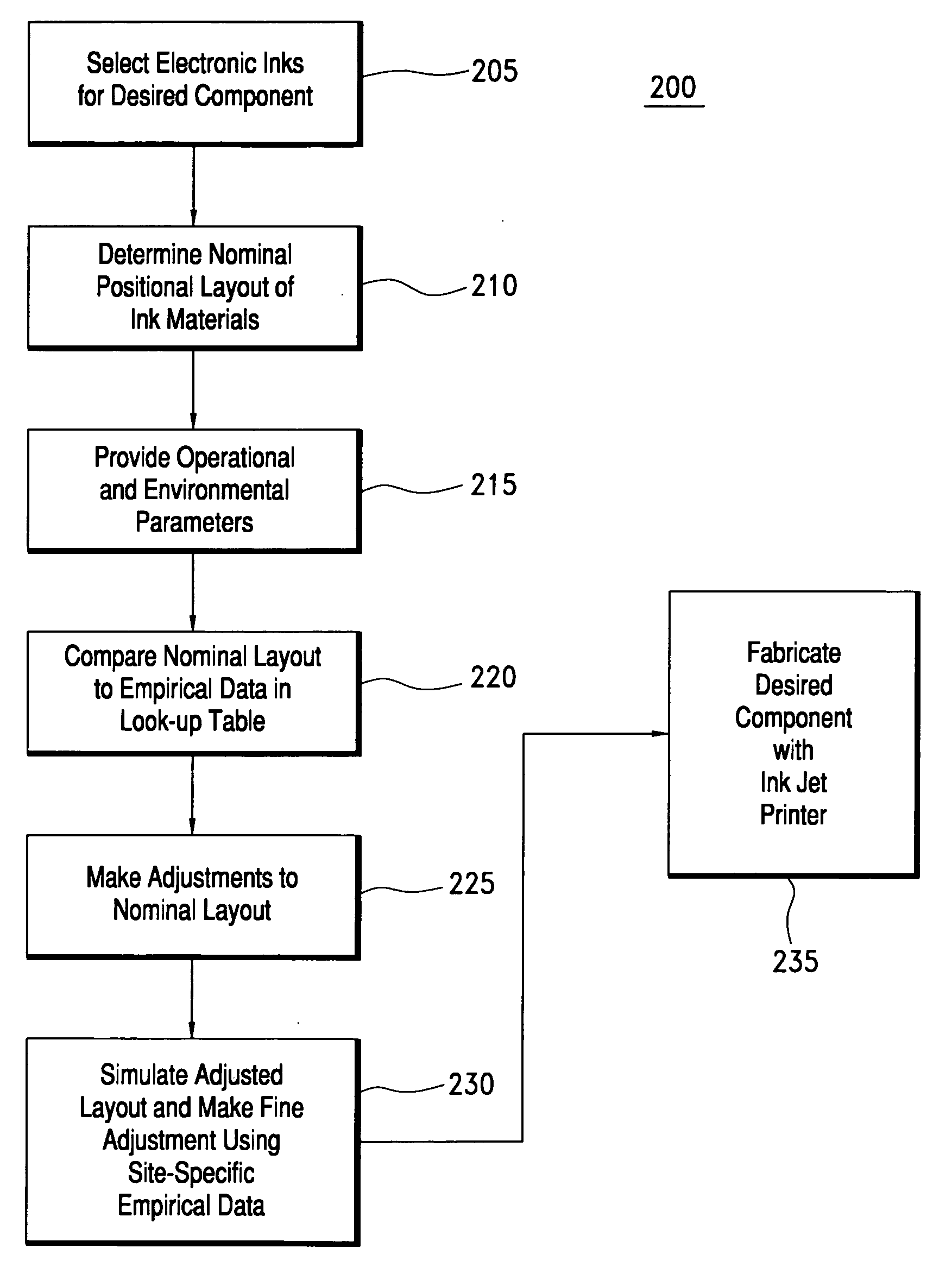

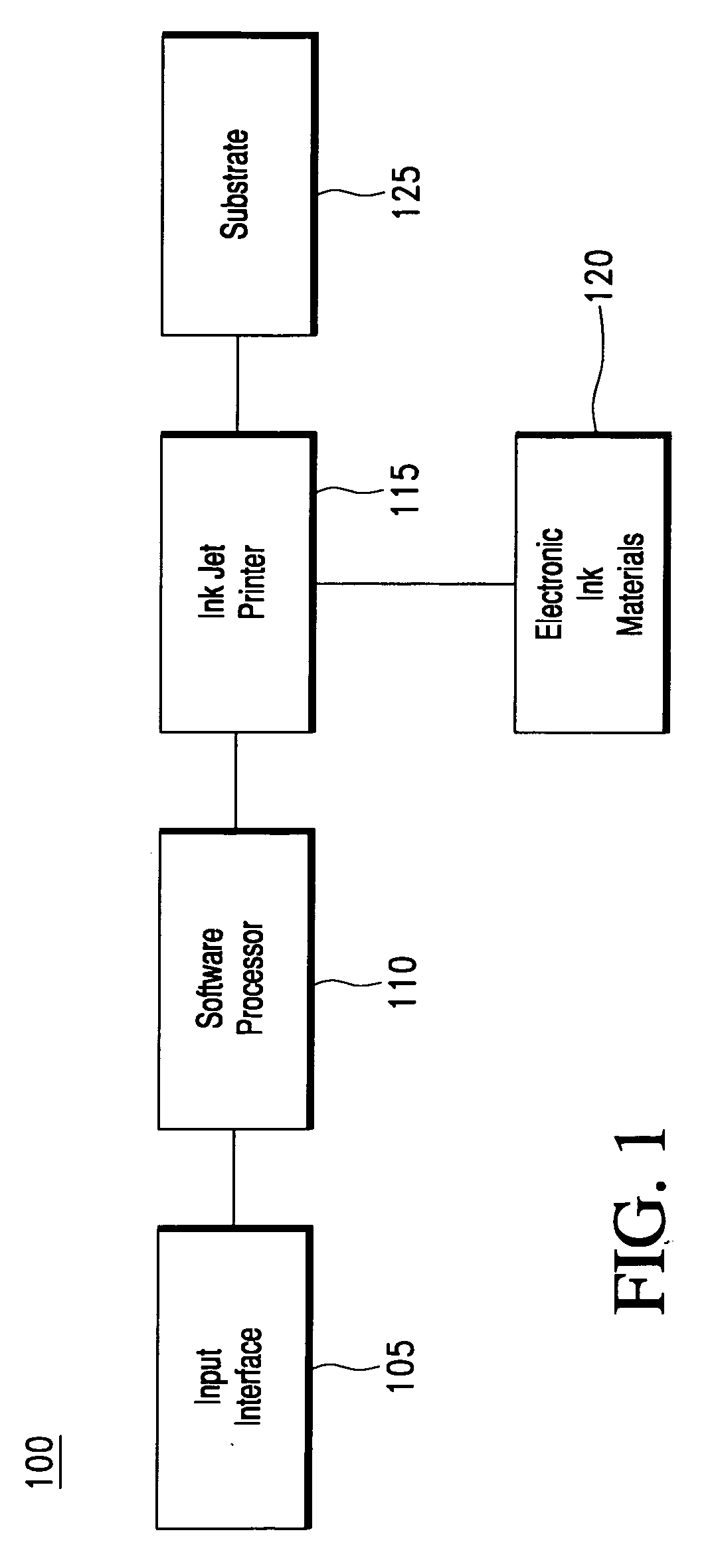

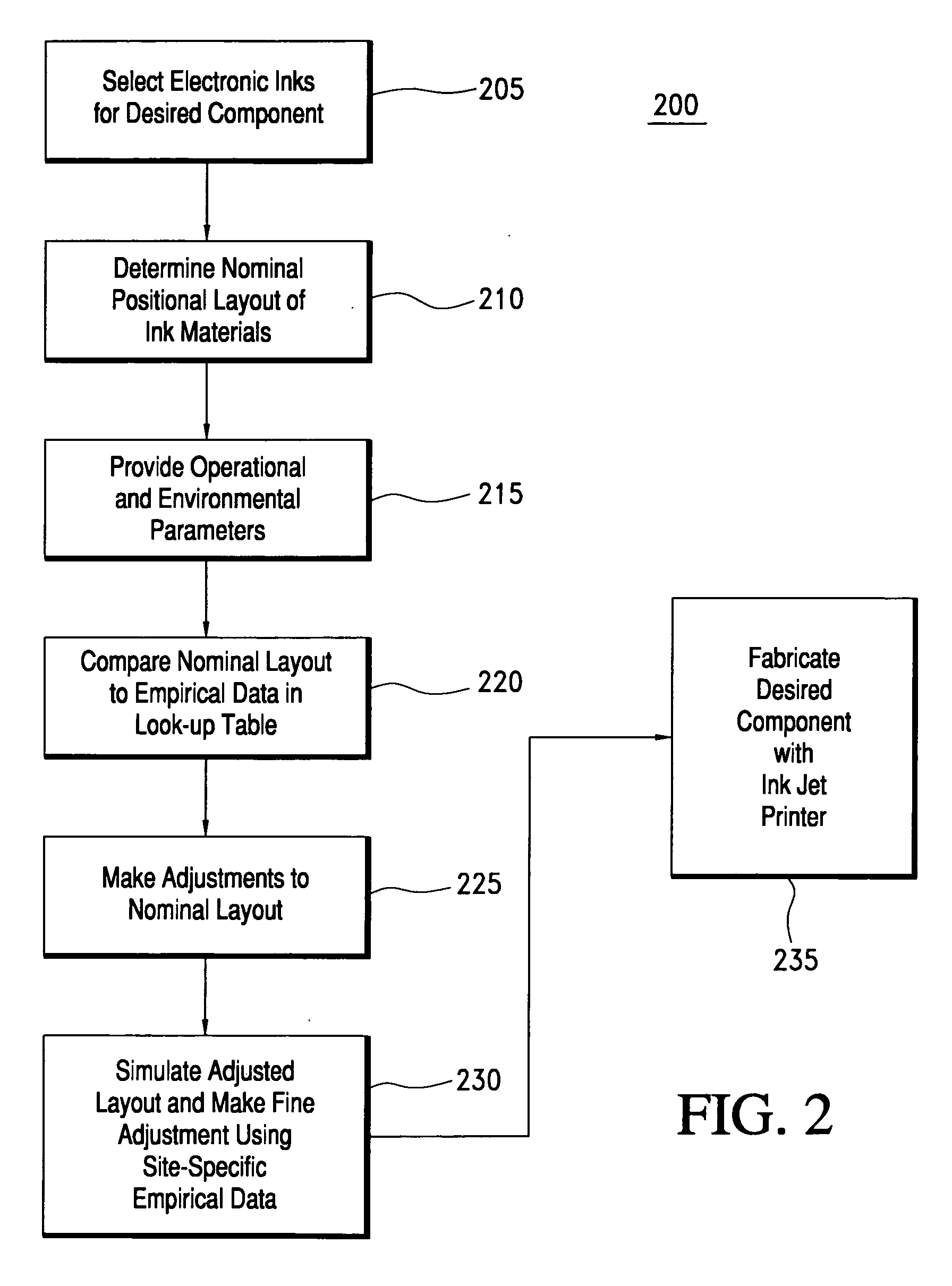

Circuit modeling and selective deposition

InactiveUS20060158478A1Printed electric component incorporationComputer designed circuitsCircuit modelingSelective deposition

A process for fabricating an electrical component using an ink-jet printing process is provided. The process includes the steps of selecting at least one electronic ink having at least a first functionality when cured; determining a positional layout for a plurality of droplets of the electronic ink(s) such that, based at least on the first functionality, the positional layout provides a desired response for the electrical component; providing at least a first characteristic that relates to the electrical component; comparing the determined positional layout to at least one corresponding entry in a lookup table of empirical data relating to the first characteristic and to the determined positional layout; adjusting the determined positional layout accordingly; and printing each of the droplets of the electronic ink(s) onto a substrate according to the adjusted positional layout. The step of determining a positional layout may include determining a volume of ink to be deposited.

Owner:CABOT CORP

Method and system for logic-level circuit modeling

InactiveUS7188327B2Simplified yet accurateAccurate timingCAD circuit designSoftware simulation/interpretation/emulationCircuit modelingTheoretical computer science

Owner:CADENCE DESIGN SYST INC

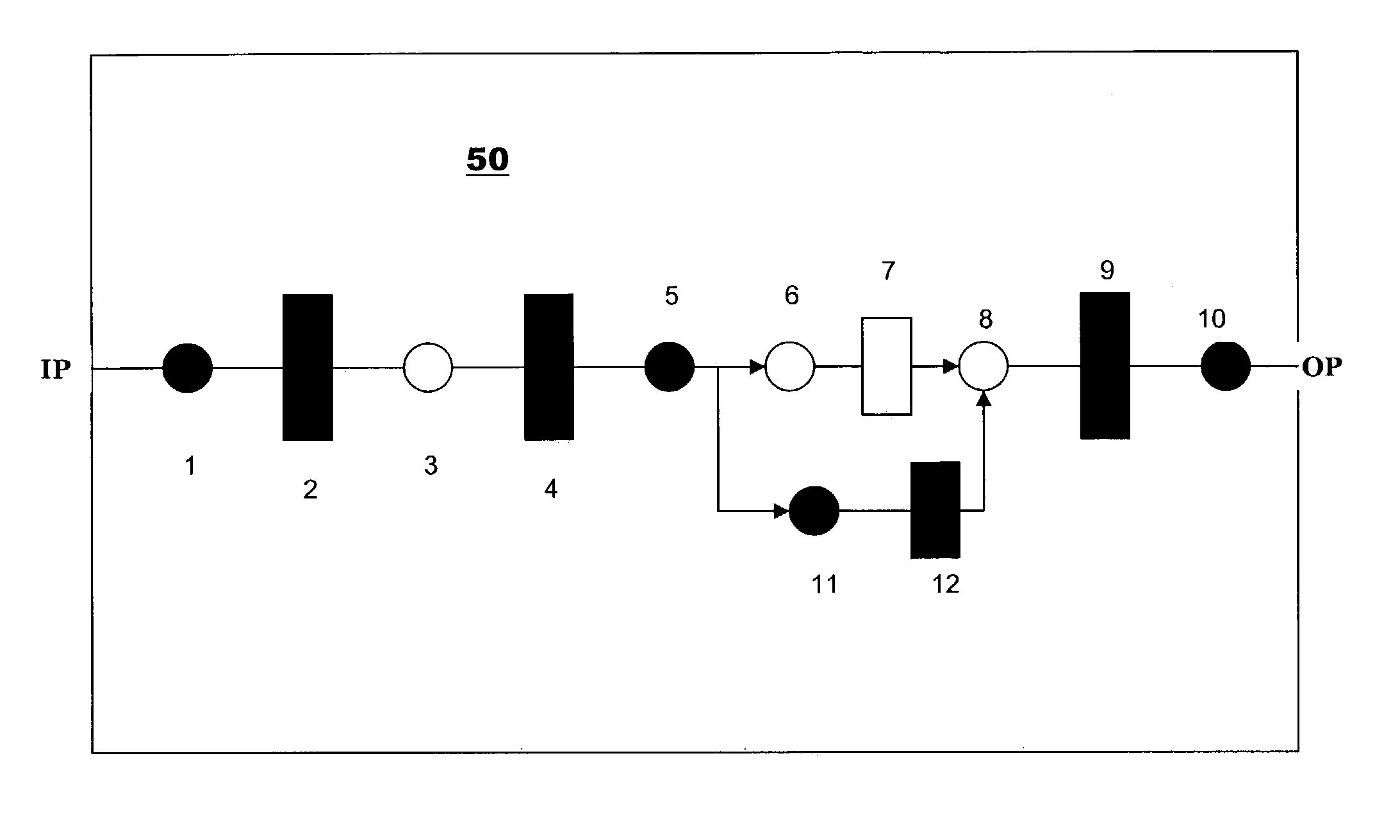

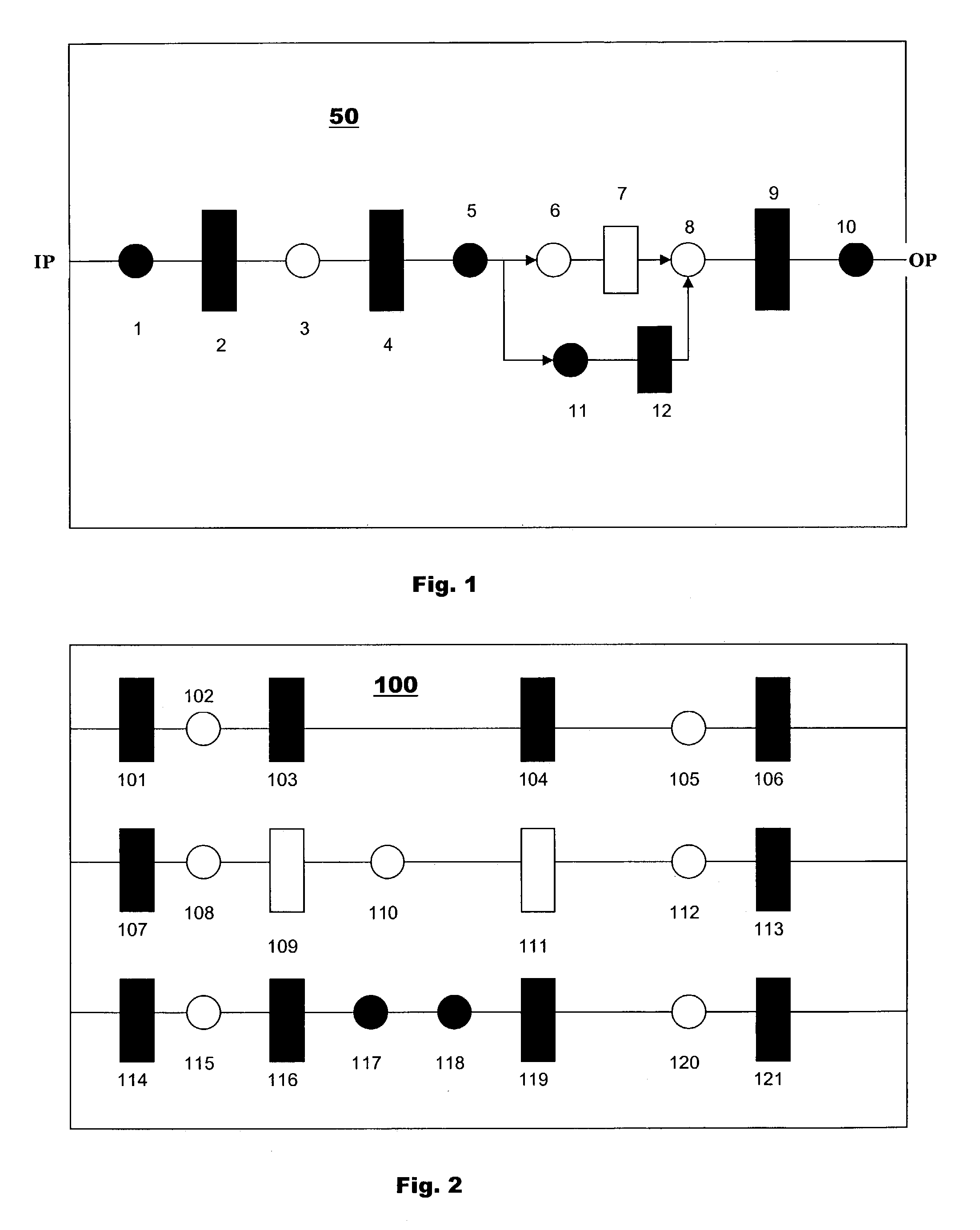

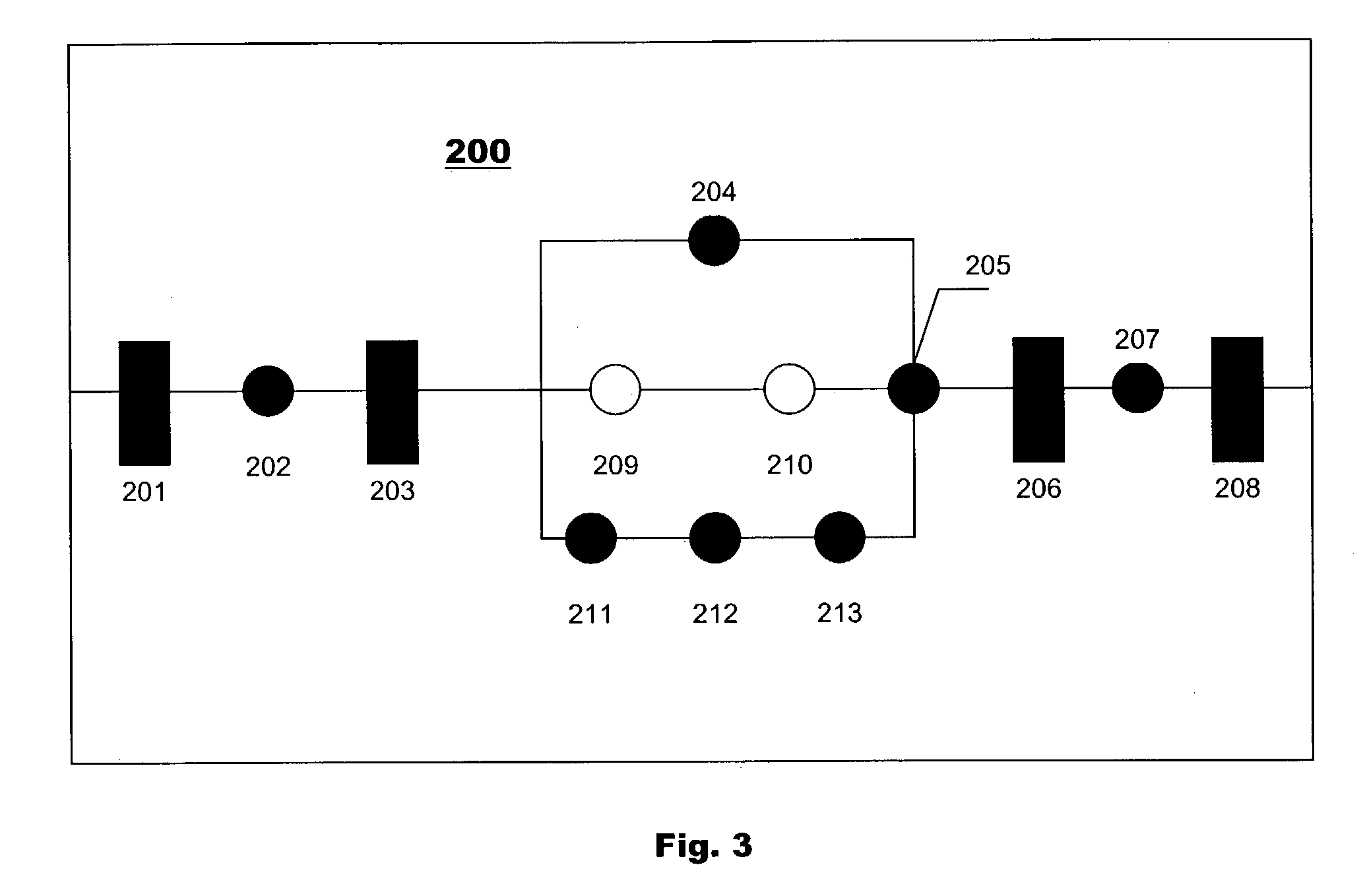

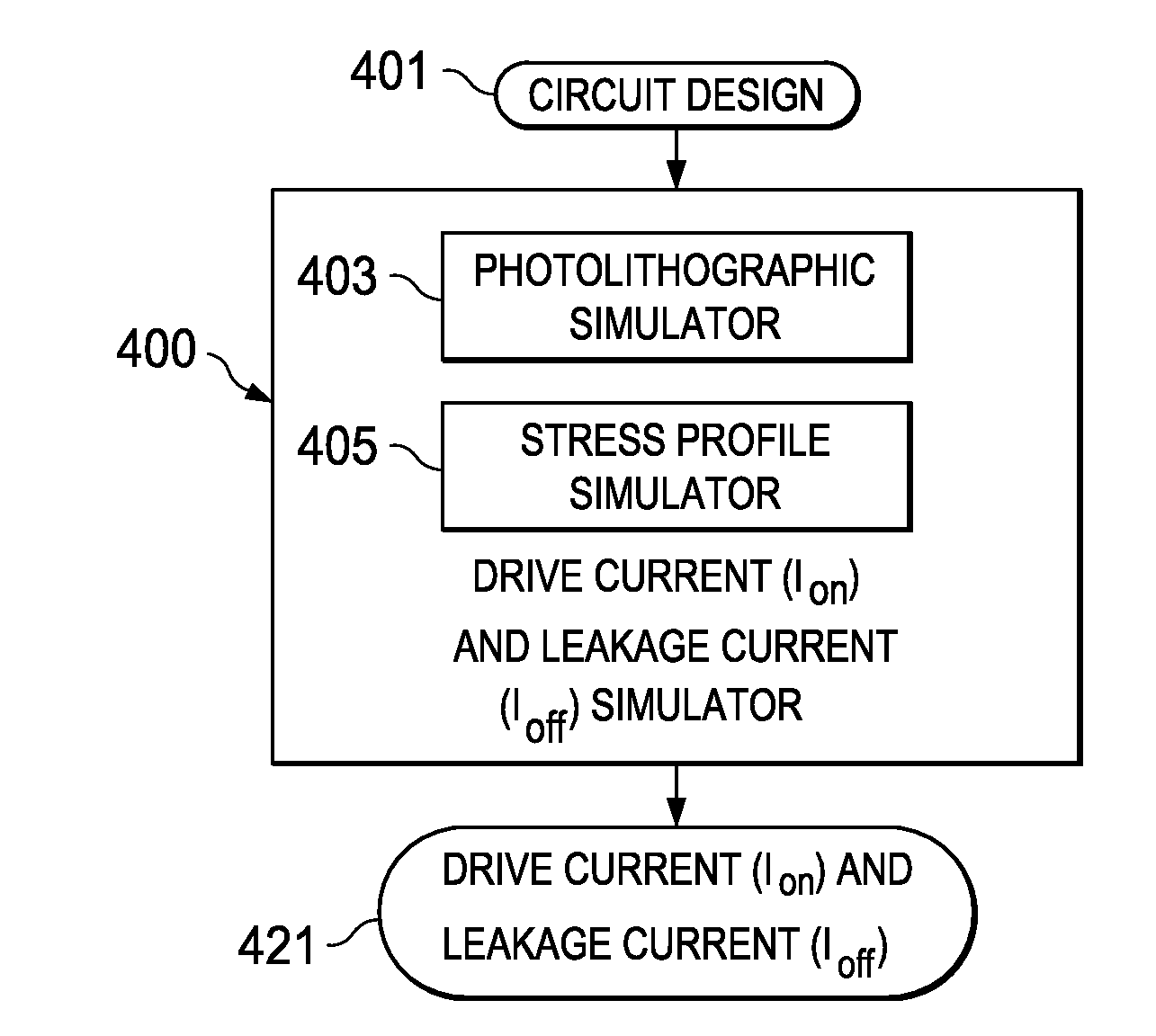

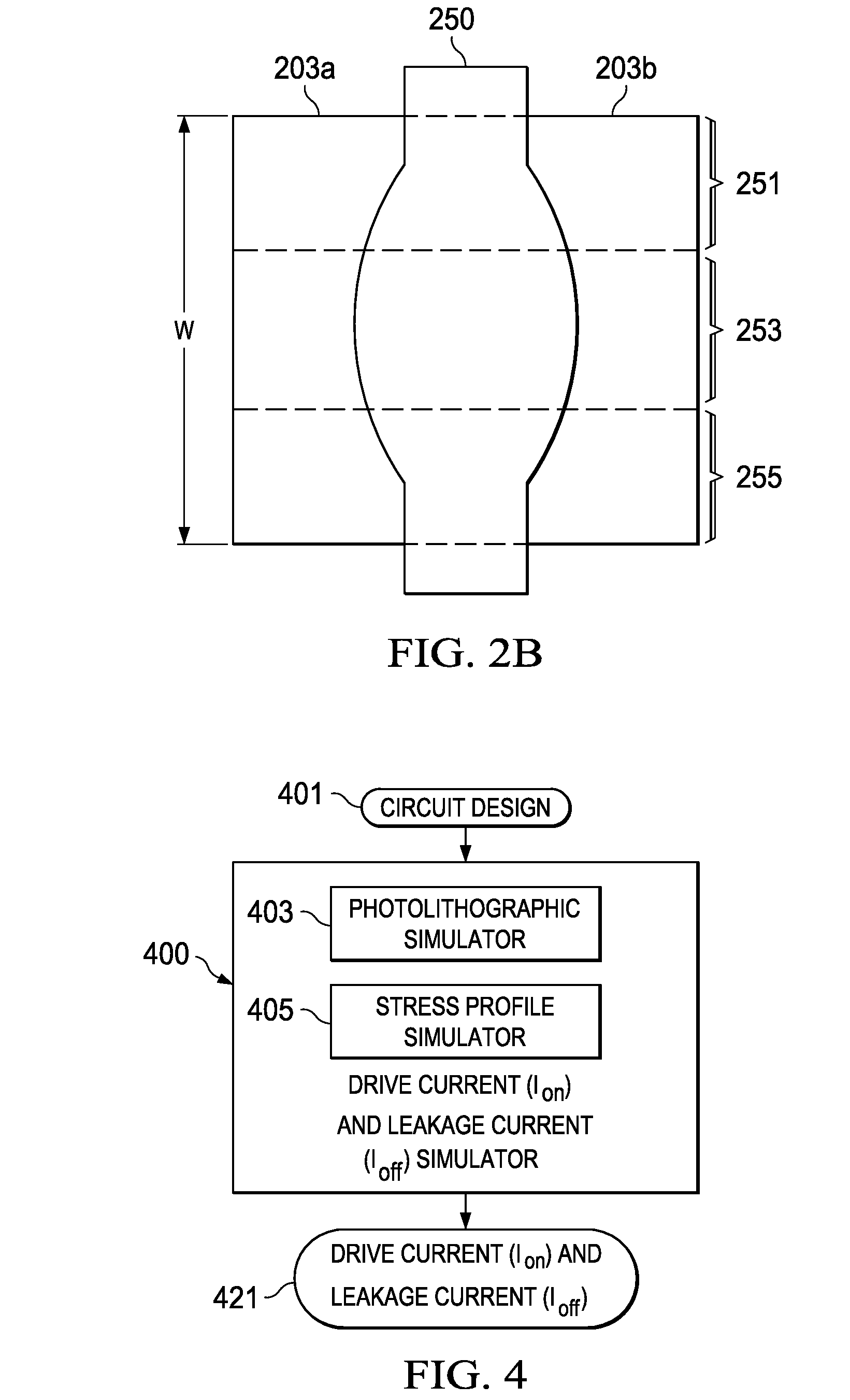

Effective gate length circuit modeling based on concurrent length and mobility analysis

ActiveUS20100257493A1Detecting faulty computer hardwareComputer aided designStress distributionCircuit modeling

Disclosed is a computer implemented method and computer program product to determine metal oxide semiconductor (MOS) gate functional limitations. A simulator obtains a plurality of slices of a MOS gate, the slices each comprising at least one parameter, the parameter comprising a slice gate width and a slice gate length. The simulator determines a current for each slice based on a slice gate length of the slice to form a length-based current for each slice. The simulator determines a length-based current for the MOS gate by summing the length-based current for each slice. The simulator calculates a stress profile for each slice. The simulator determines a slice carrier mobility for each slice based on the stress profile of each slice. The simulator determines a carrier mobility-based current for each slice, based on each slice carrier mobility. The simulator determines a carrier mobility for the MOS gate based on the carrier mobility-based current for each slice. The simulator determines an effective length for the MOS gate based on the length-based current.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

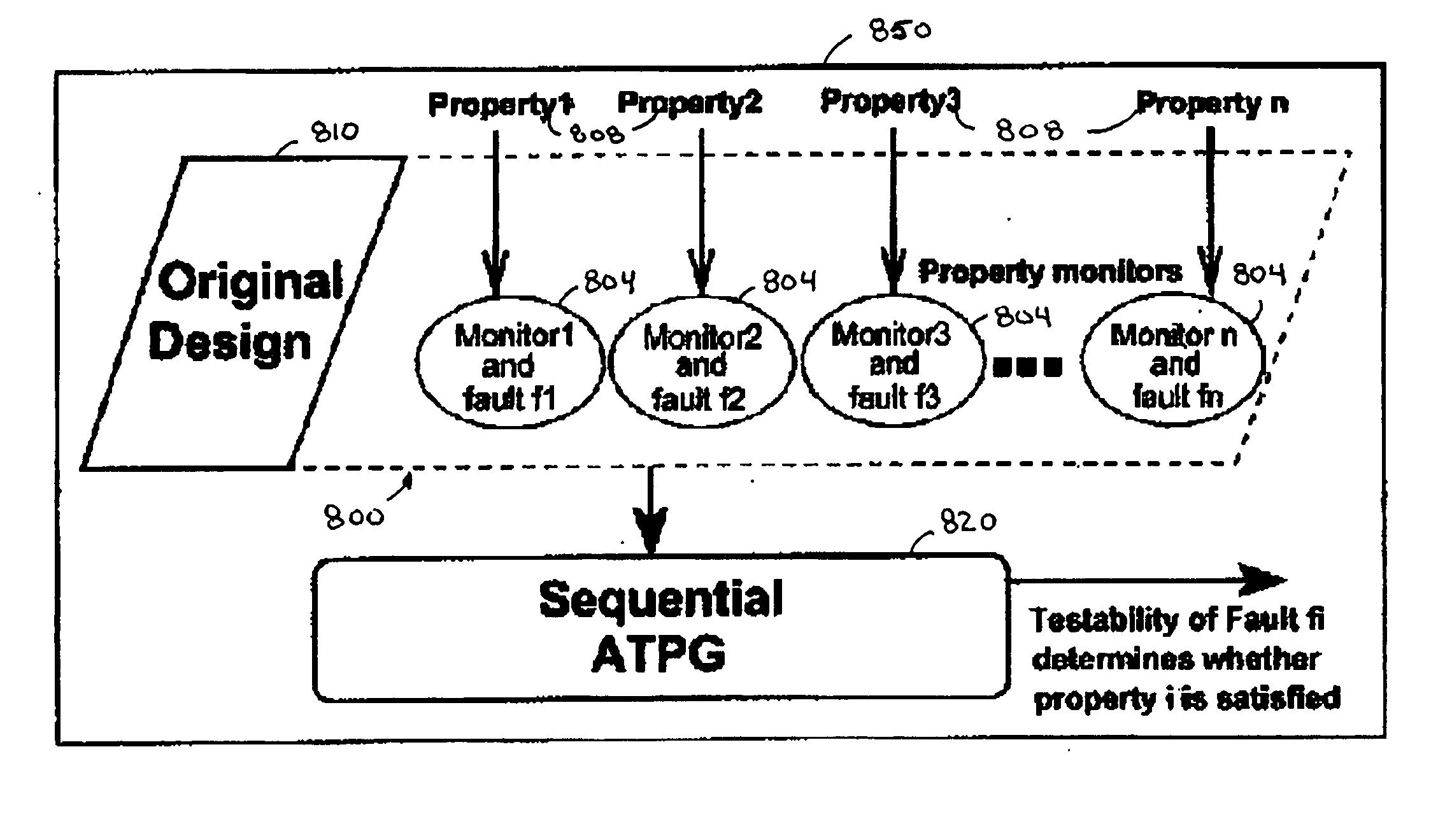

Circuit modeling apparatus, systems, and methods

InactiveUS20050193304A1Increase credibilityGreat confidenceElectronic circuit testingError detection/correctionCircuit modelingComputer science

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

Global equivalent circuit modeling system for substrate mounted circuit components incorporating substrate dependent characteristics

ActiveUS7003744B2Accurately frequency performanceAccurate frequencyComputer designed circuitsComputer aided designDielectricCircuit modeling

The present invention is a substrate dependent circuit modeling system for substrate-mounted components. The height and dielectric constant of a substrate have a significant impact on the frequency response of such components, and these effects cannot be treated independently from the circuit model. The equivalent circuit parameters in the model must be made to vary in accordance with changes in the substrate. The invention includes the steps of selecting a substrate mounted electrical circuit component for which an equivalent circuit model is desired, determining equivalent circuit model input parameters, wherein some of which are dependent upon characteristics of the substrate upon which the component is mounted, for the selected component, representing the selected electrical circuit component mounted upon the substrate as an equivalent electrical circuit, formulating mathematical expressions based upon the input parameters, and creating a unique equivalent circuit model for the component mounted upon the given substrate, the unique equivalent circuit model representing the mounting of the component upon the given substrate wherein the equivalent circuit model provides behavior and performance predictions of the component based upon the given substrate characteristics.

Owner:UNIV OF SOUTH FLORIDA

System And Method For Electrical Theory Simulator

A circuit modeling simulator is provided as an educational tool substantially duplicating and expanding a hardware-based breadboard educational tool. To do so, the system and method provides a circuit modeling simulator that allows a user to create and test a simulated electronic circuit, and includes a library of schematic components, displayed on the side of a screen that allows a user to drag and drop the components anywhere on the project screen, displayed at a center of the screen. The user can place multiple occurrences of each type of device, and each component includes a drop down window that allows the user to select the particular model and value of the component. The user is also provided with simulated testing devices or meters that display the appropriate values based on the circuit parameter behaviors.

Owner:NAT JOINT APPRENTICESHIP & TRAINING COMMITTEE

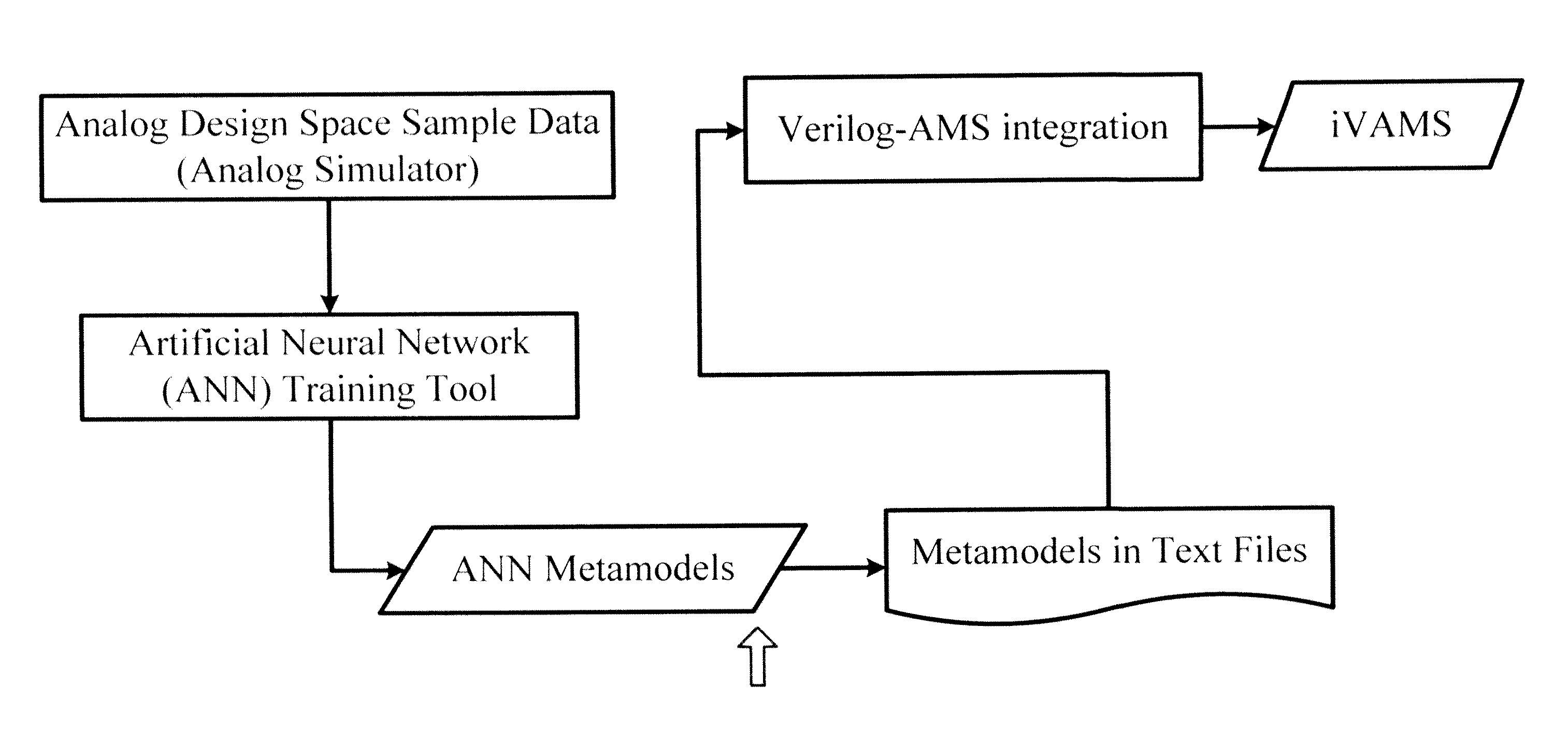

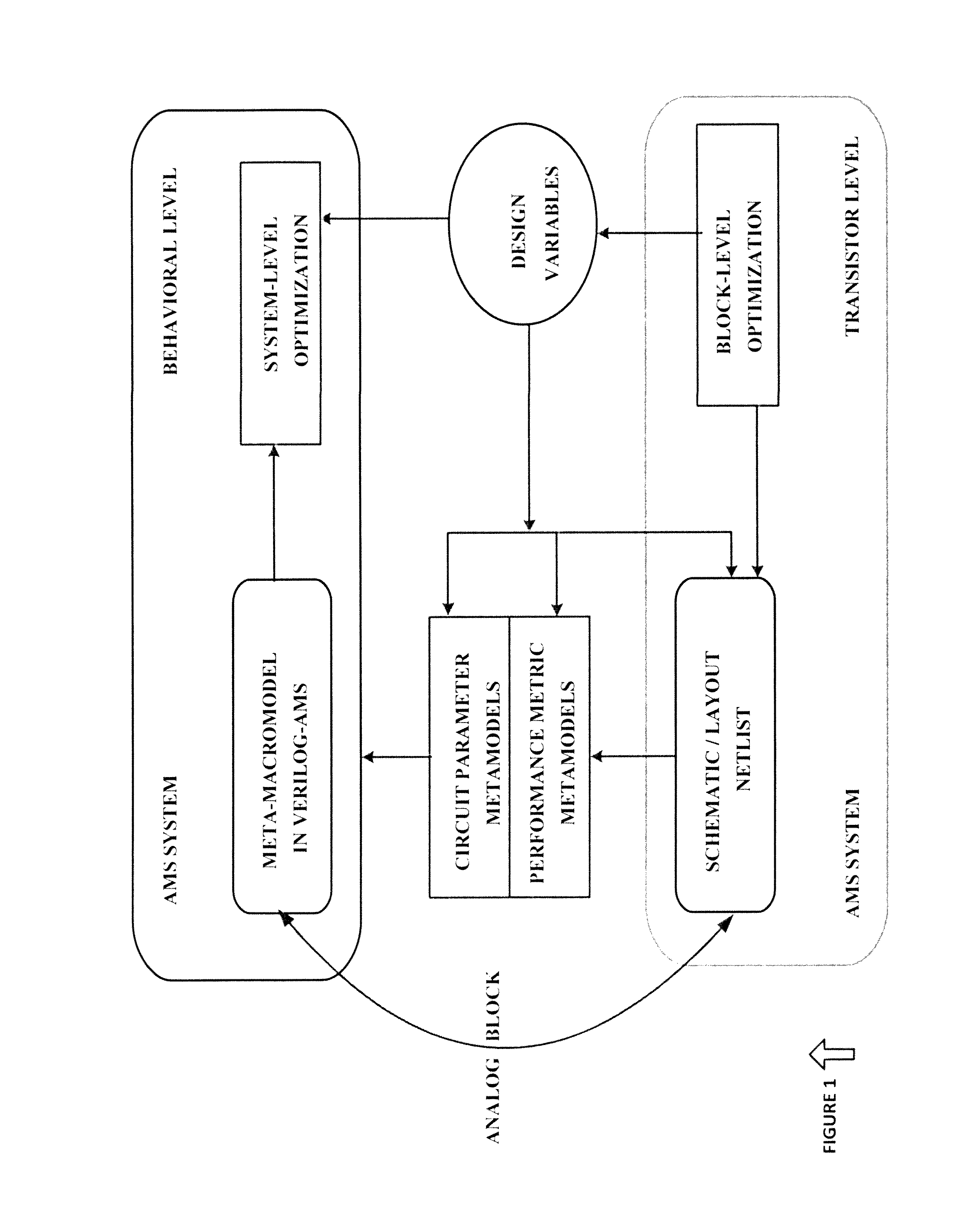

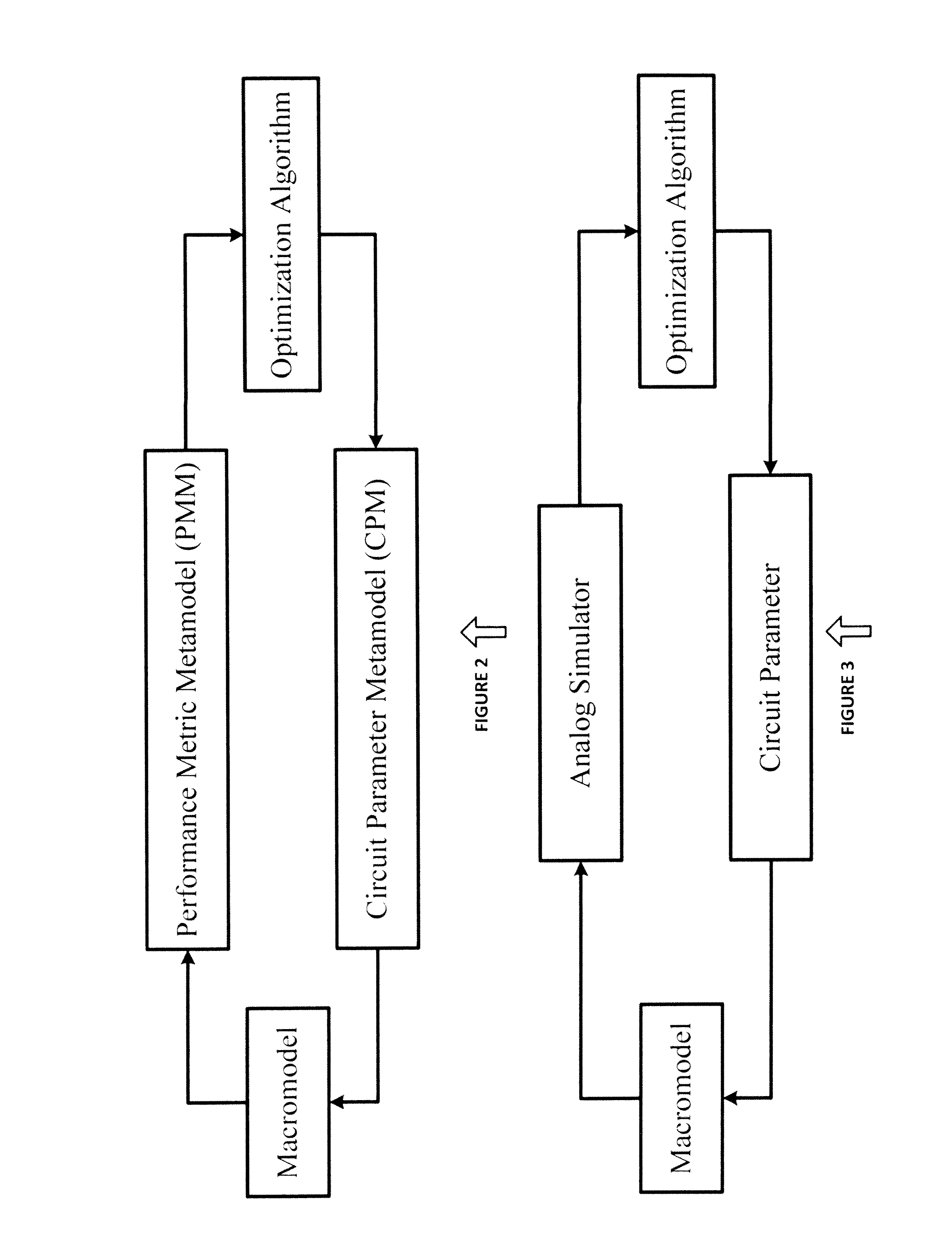

Intelligent metamodel integrated Verilog-AMS for fast and accurate analog block design exploration

InactiveUS9026964B2CAD circuit designSoftware simulation/interpretation/emulationComputer architectureCircuit modeling

Owner:UNIVERSITY OF NORTH TEXAS

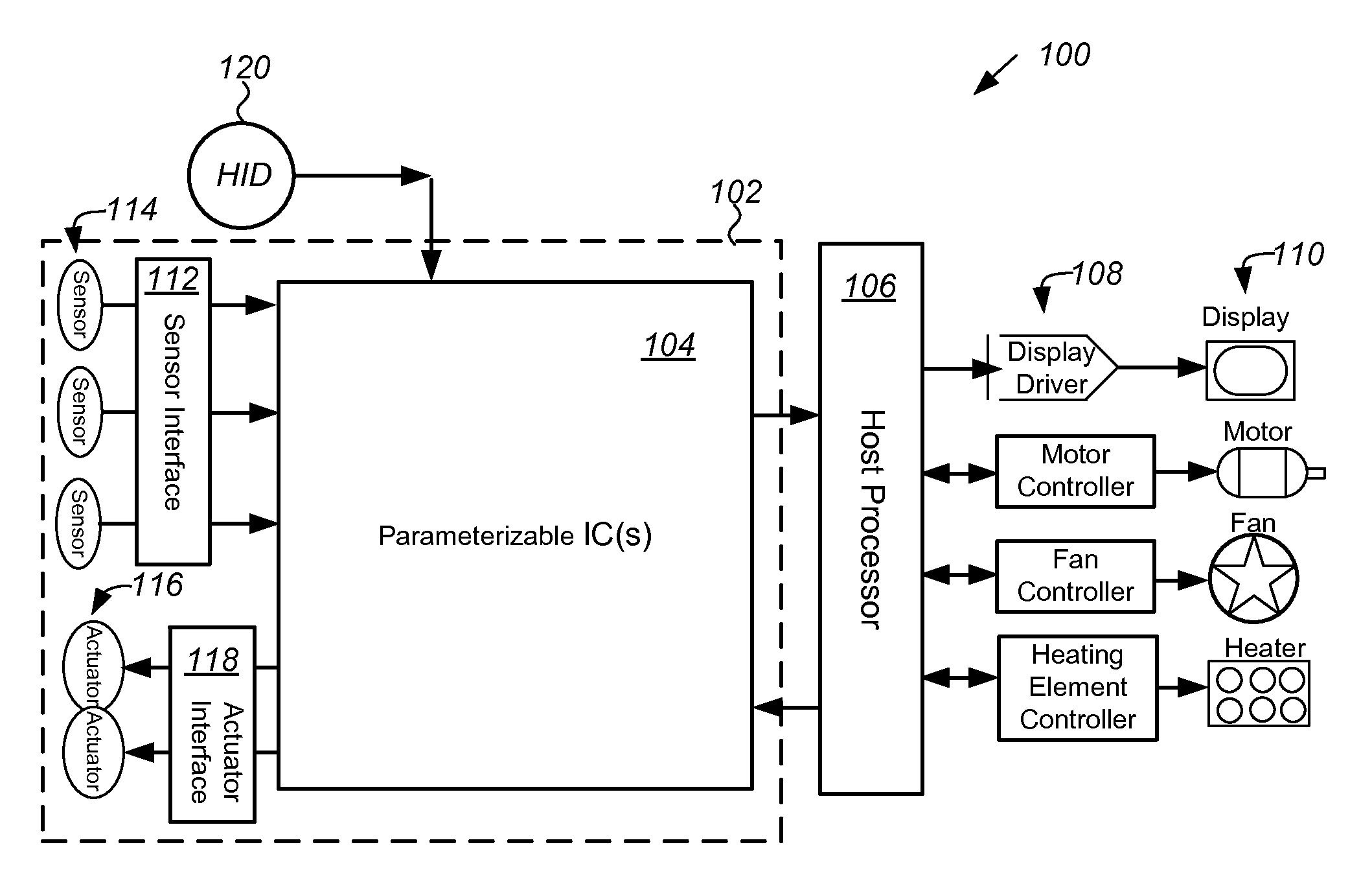

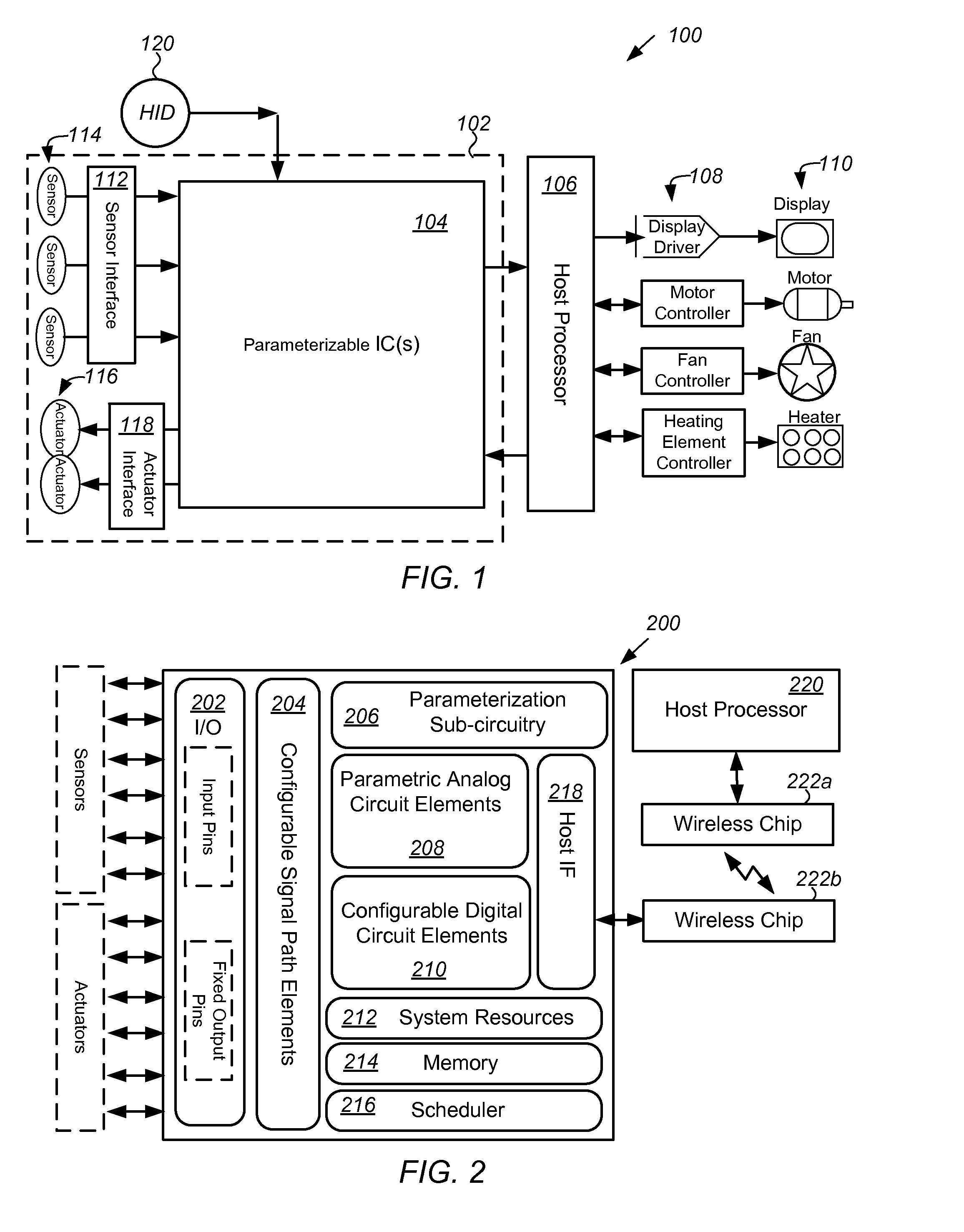

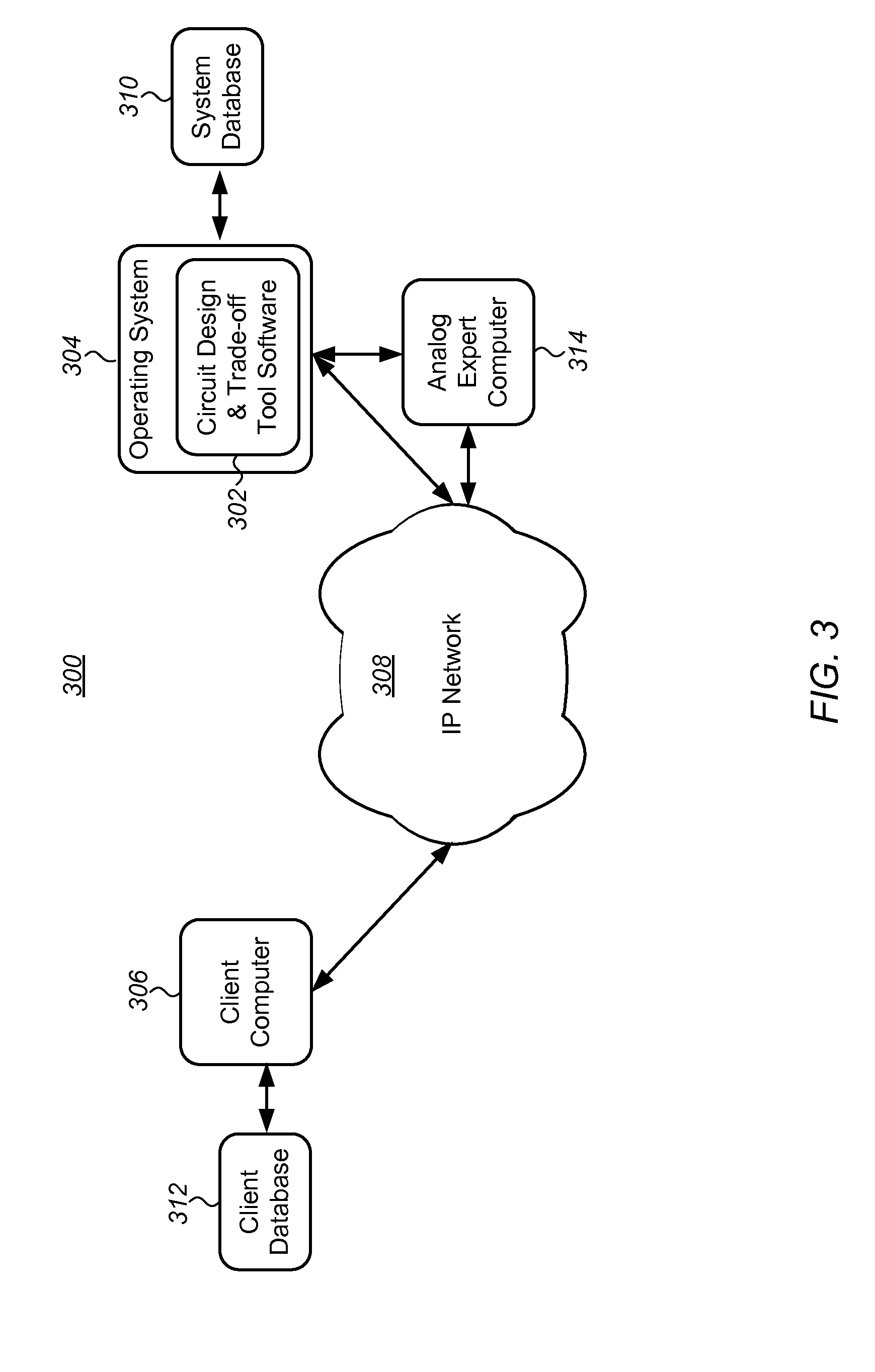

Tool and Method for Refining A Circuit Including Parametric Analog Elements

A method is provided for designing and implementing a circuit comprising an integrated circuit (IC) including a number of analog and digital circuit elements for which operating parameters can be set. In one embodiment the method includes entering in a circuit design tool embodied in a computer readable medium on a server specified requirements for a circuit, the specified requirements including physical properties to be sensed by the circuit. The circuit is automatically modeled by the circuit design tool based on the specified requirements and resources available on the IC, the modeling including translating the specified requirements into parameter settings of the number of the analog and digital circuit elements. The circuit is then built, the building including setting parameters of at least one of the analog and digital circuit elements of the IC using the circuit design tool based on the modeling of the circuit.

Owner:CYPRESS SEMICON CORP

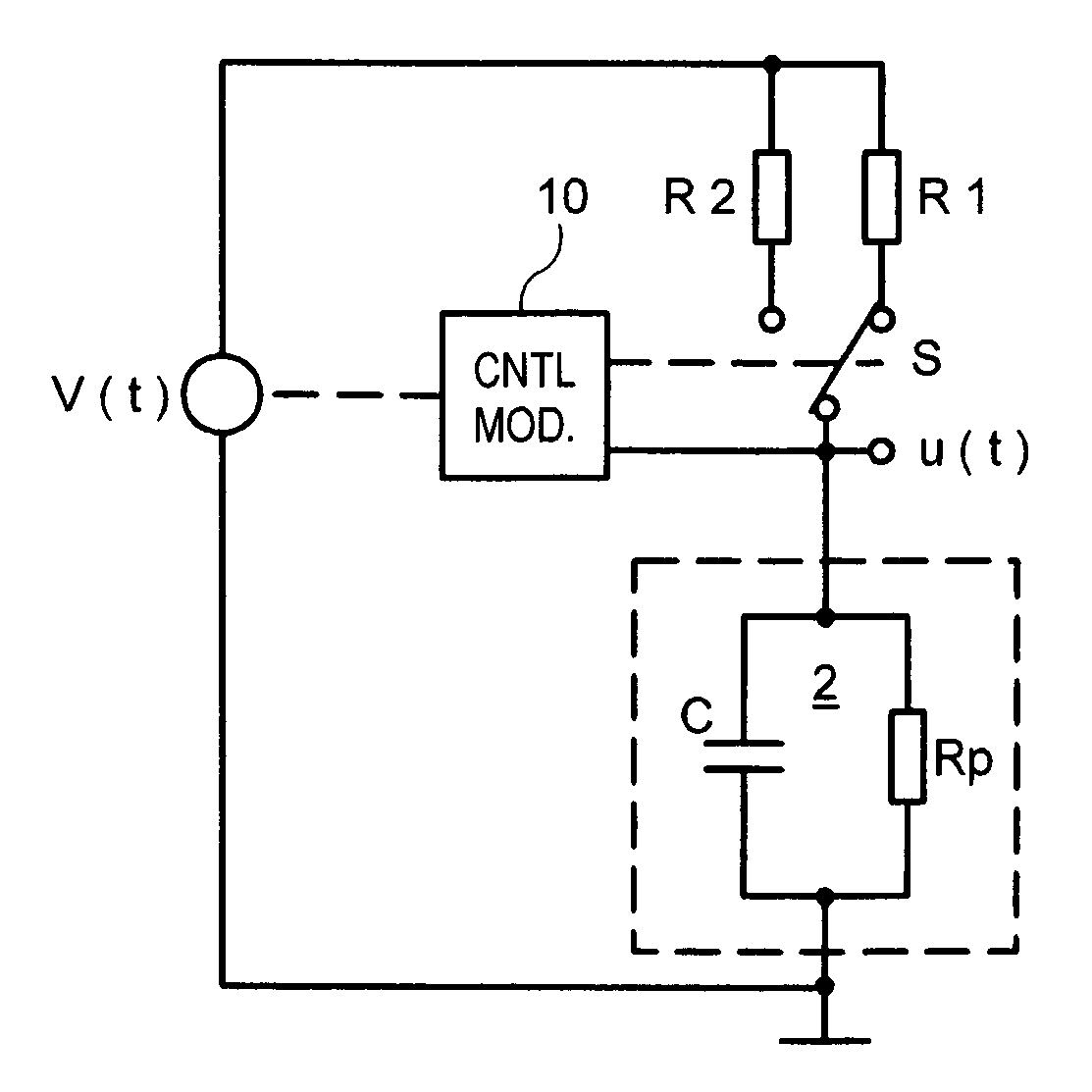

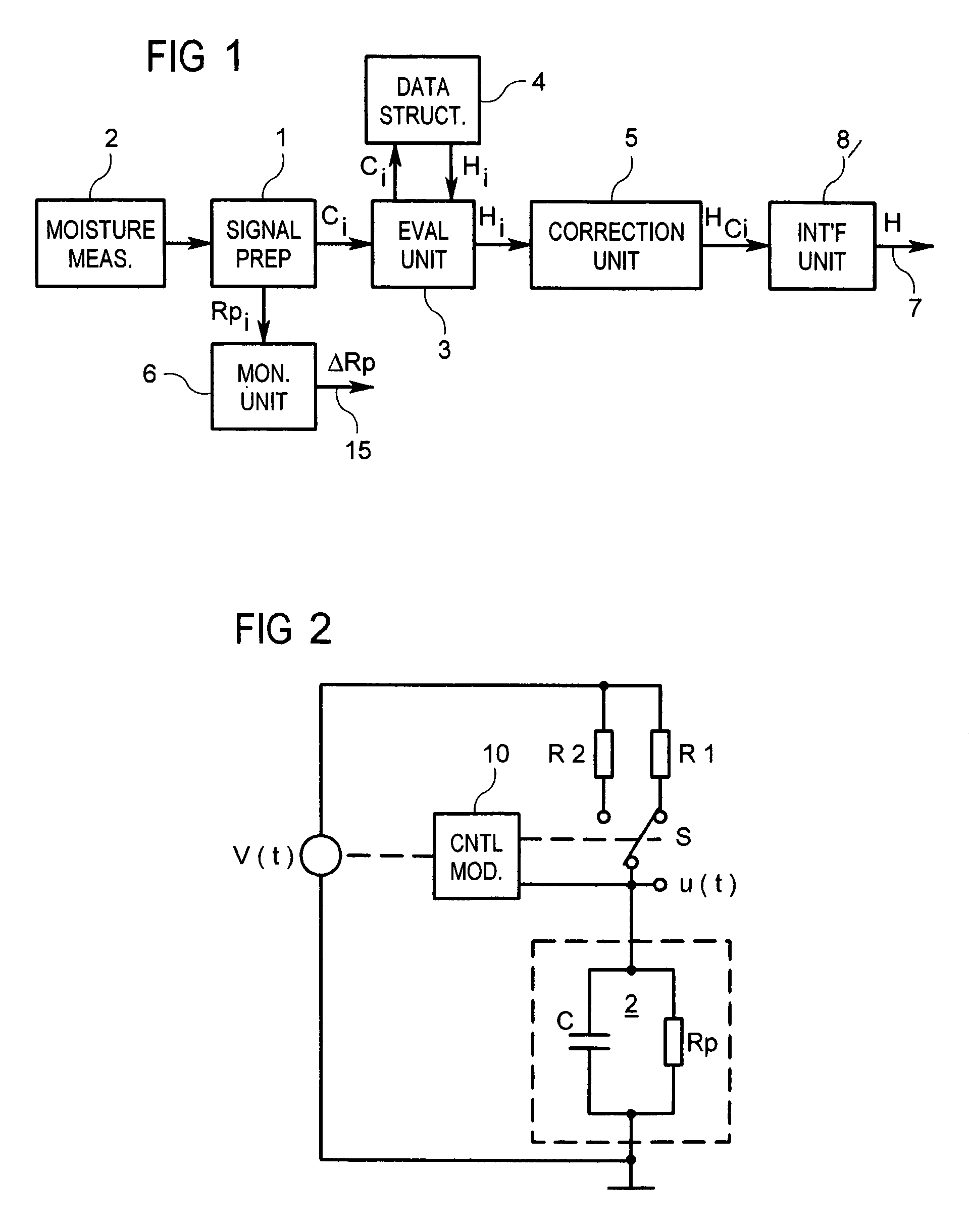

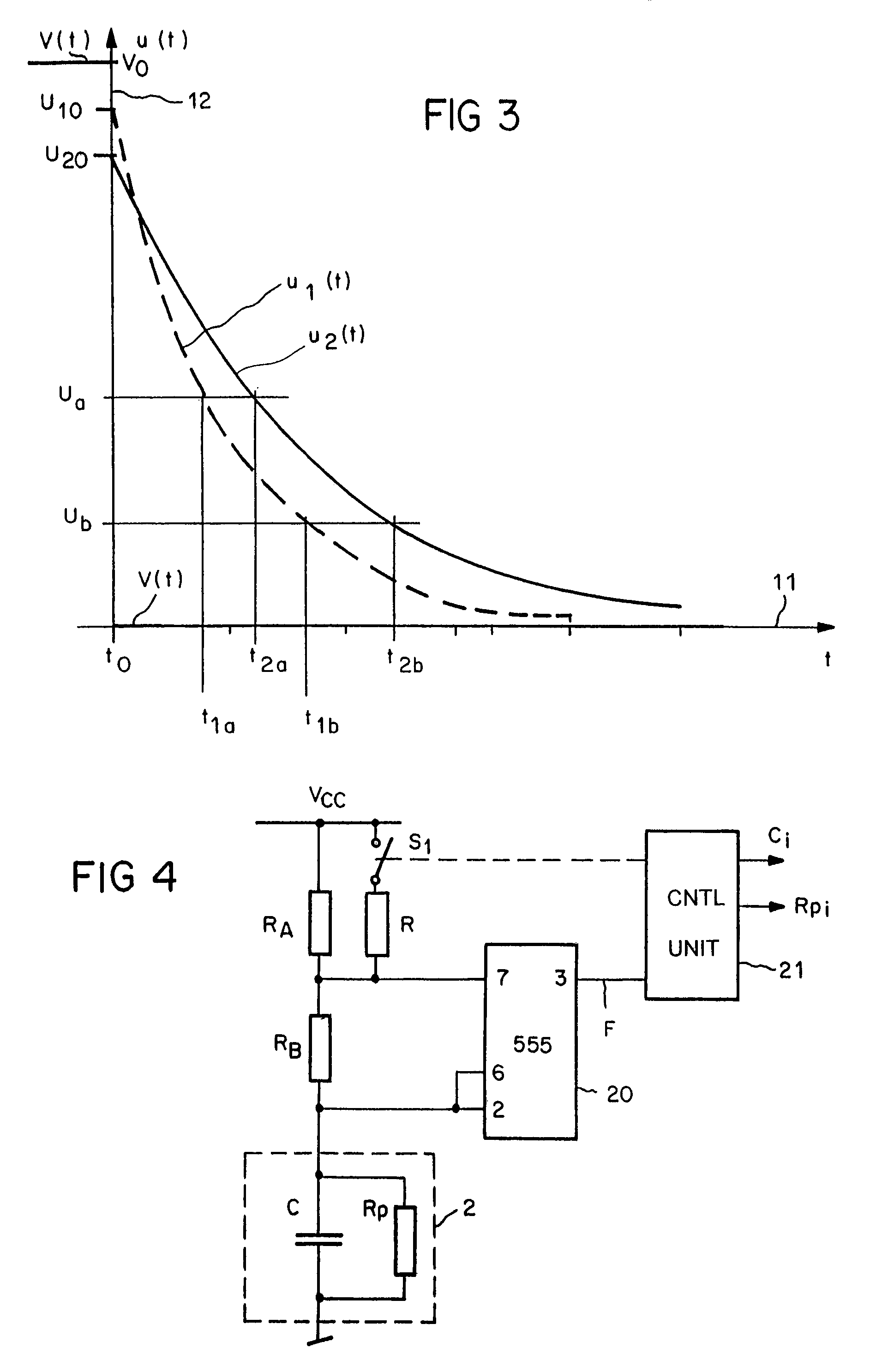

Moisture sensor with capacitive moisture measuring element and method of determining air humidity

ActiveUS7030630B2Improve the level ofKnown methodResistance/reactance/impedenceMaterial capacitanceCapacitanceEngineering

In a method of determining air humidity, a capacitive moisture measuring element (2) used in a moisture sensor for calculation operations is modelled by a parallel circuit of an ideal capacitor (C) and an ohmic resistance (Rp). Charging and / or discharging of the capacitive moisture measuring element (2) by way of a first measuring resistor (R1; RA) provides for ascertaining a first time constant or a first period duration of the charging and / or discharging operation, and charging and / or discharging of the moisture measuring element (2) by way of a second measuring resistor (R2; RA / / R) provides for ascertaining a second one. The capacitance (C) of the moisture measuring element (2) is then calculated from the two time constants or the two period durations, a value for the moisture level finally being ascertained from the capacitance. This method achieves a higher level of measuring accuracy on the part of the moisture sensor.

Owner:SIEMENS SWITZERLAND

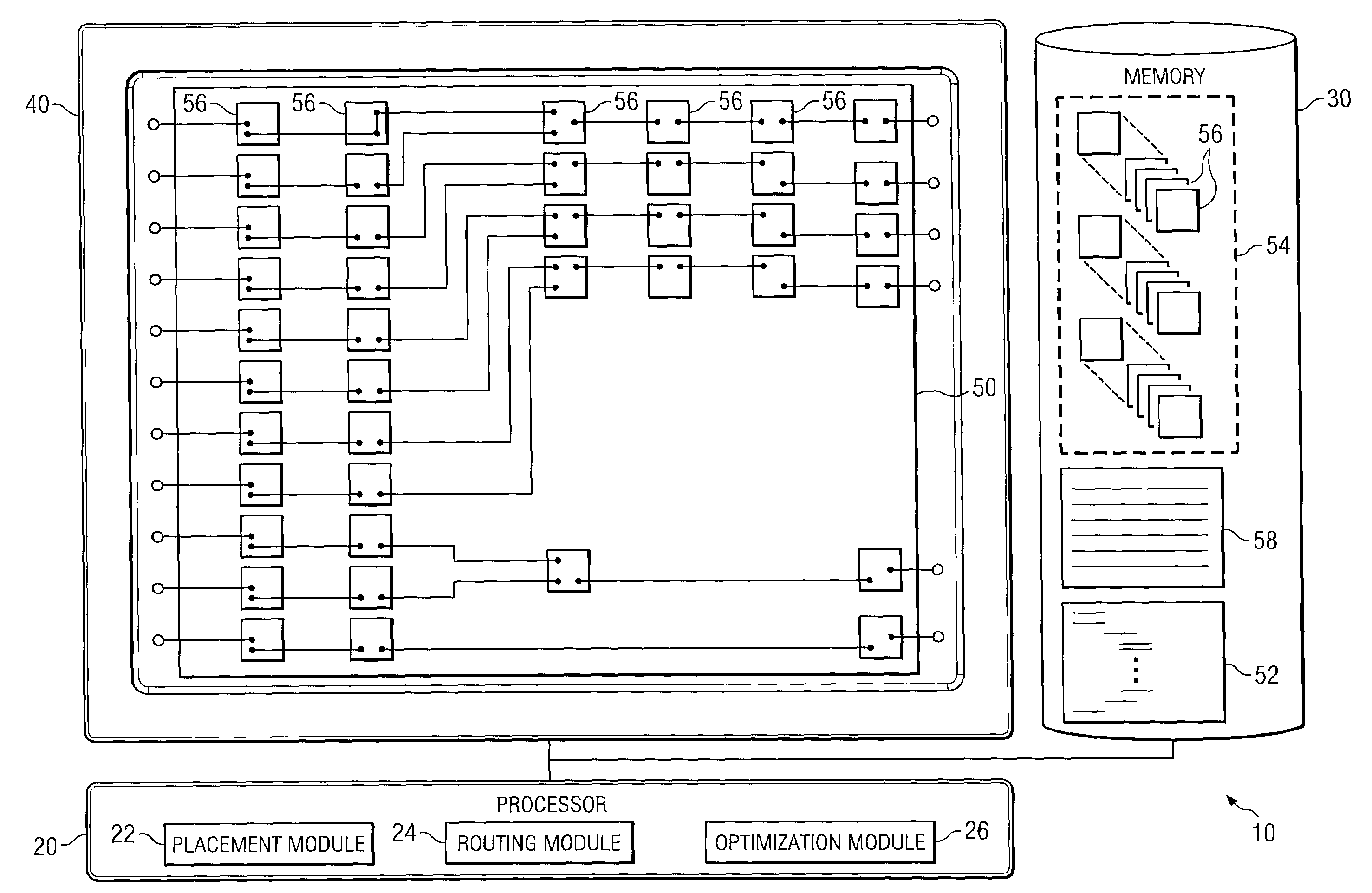

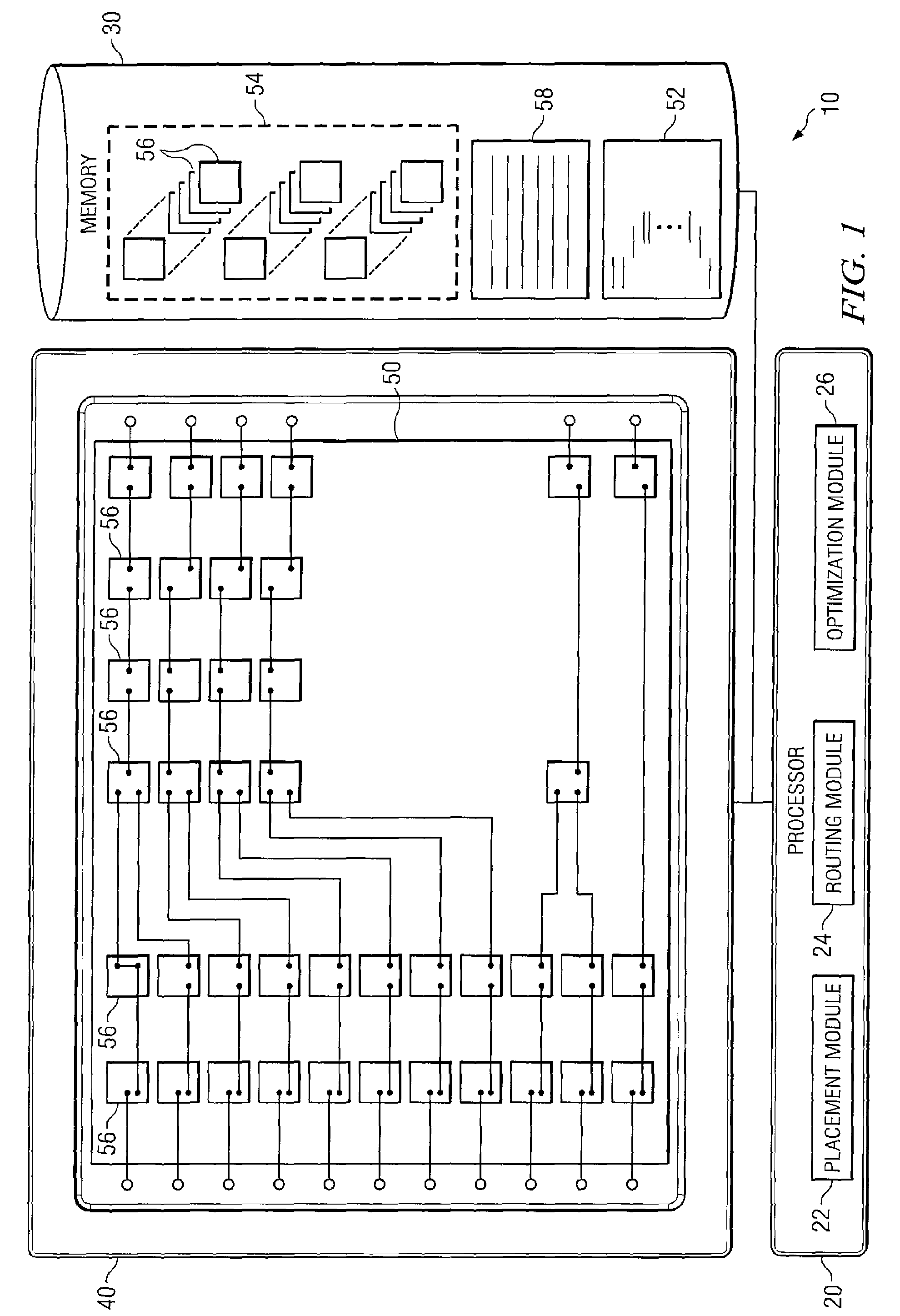

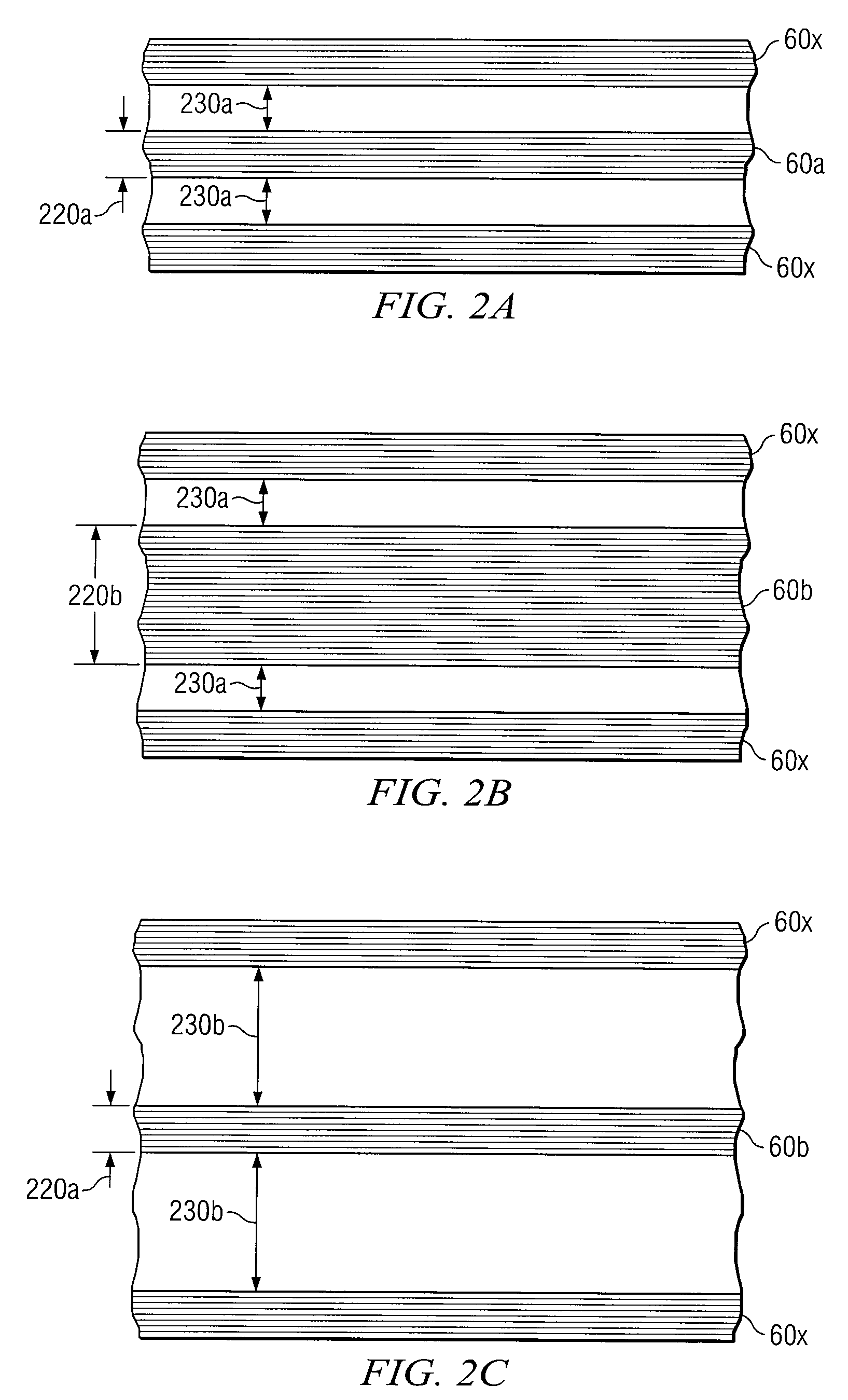

System and method for routing connections

InactiveUS20090164963A1Improve device performanceMinimal size increaseComputer aided designSpecial data processing applicationsWire widthCircuit modeling

A method for modeling a circuit includes receiving a netlist that defines a plurality of connections between a plurality of circuit elements and identifying a subset of the connections. The method also includes routing the identified connections with a first group of wires having a first wire width and routing at least a portion of the remaining connections with a second wire width. The second wire width is smaller than the first wire width. The method further includes replacing the first group of wires with a third group of wires having the second wire width.

Owner:MIE FUJITSU SEMICON

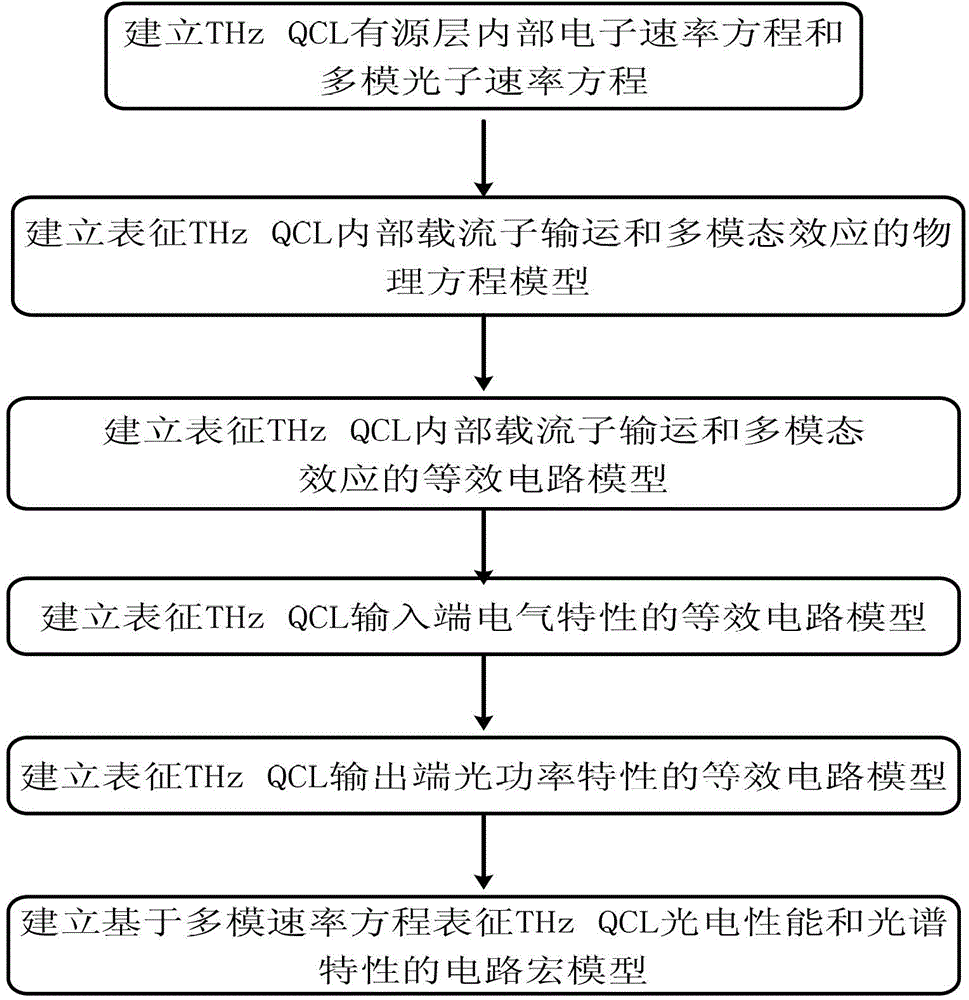

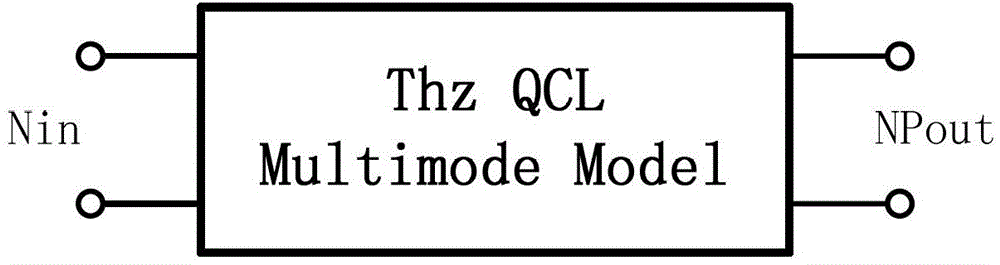

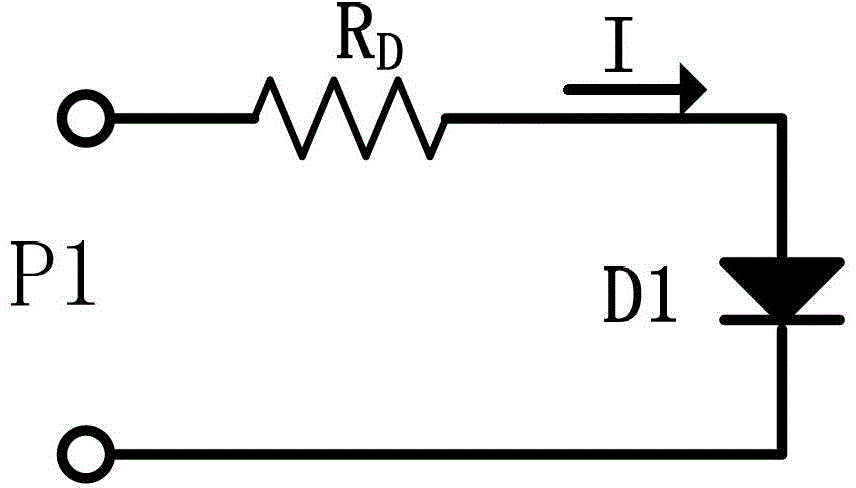

Circuit modeling and simulation method representing terahertz quantum cascading laser device multimode effect

InactiveCN104156545AMeet the needs of optoelectronic hybrid simulationGuaranteed Simulation AccuracySpecial data processing applicationsCircuit modelingOptical power

The invention relates to a circuit modeling and simulation method representing the terahertz quantum cascading laser device multimode effect. The method includes the steps of firstly, establishing a multimode velocity equation set representing carrier transportation characteristics inside a THzQCL active layer; secondly, establishing a physical equation model representing the multimode effect inside the THzQCL; thirdly, obtaining a corresponding equivalent circuit model through variable substitution and simplification; fourthly, establishing an equivalent circuit model representing the electrical characteristics of the input end of the THzQCL; fifthly, establishing an equivalent circuit model representing the luminous power characteristics of the output end of the THzQCL; sixthly, establishing a circuit macro model which comprises an electrical port and an optical power output port, and conducting photoelectric property simulation and output spectral property testing on the basis of the circuit macro model. By means of the circuit modeling and simulation method, the influences of the temperature on various photoelectric properties of the THzQCL can be tested, and imitation and simulation for the photoelectric property and the output multimode effect of the THzQCL can be supported and achieved.

Owner:WUHAN UNIV

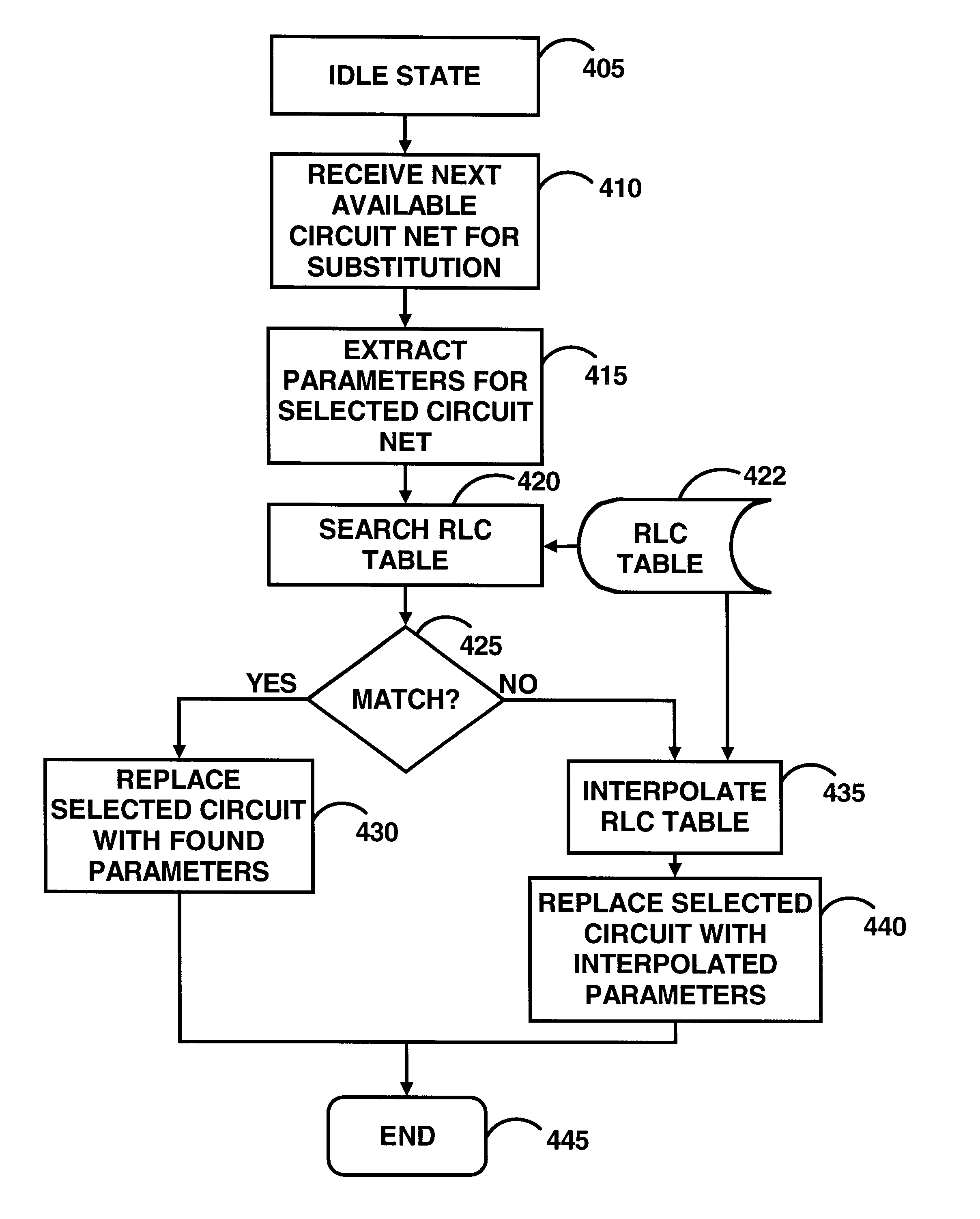

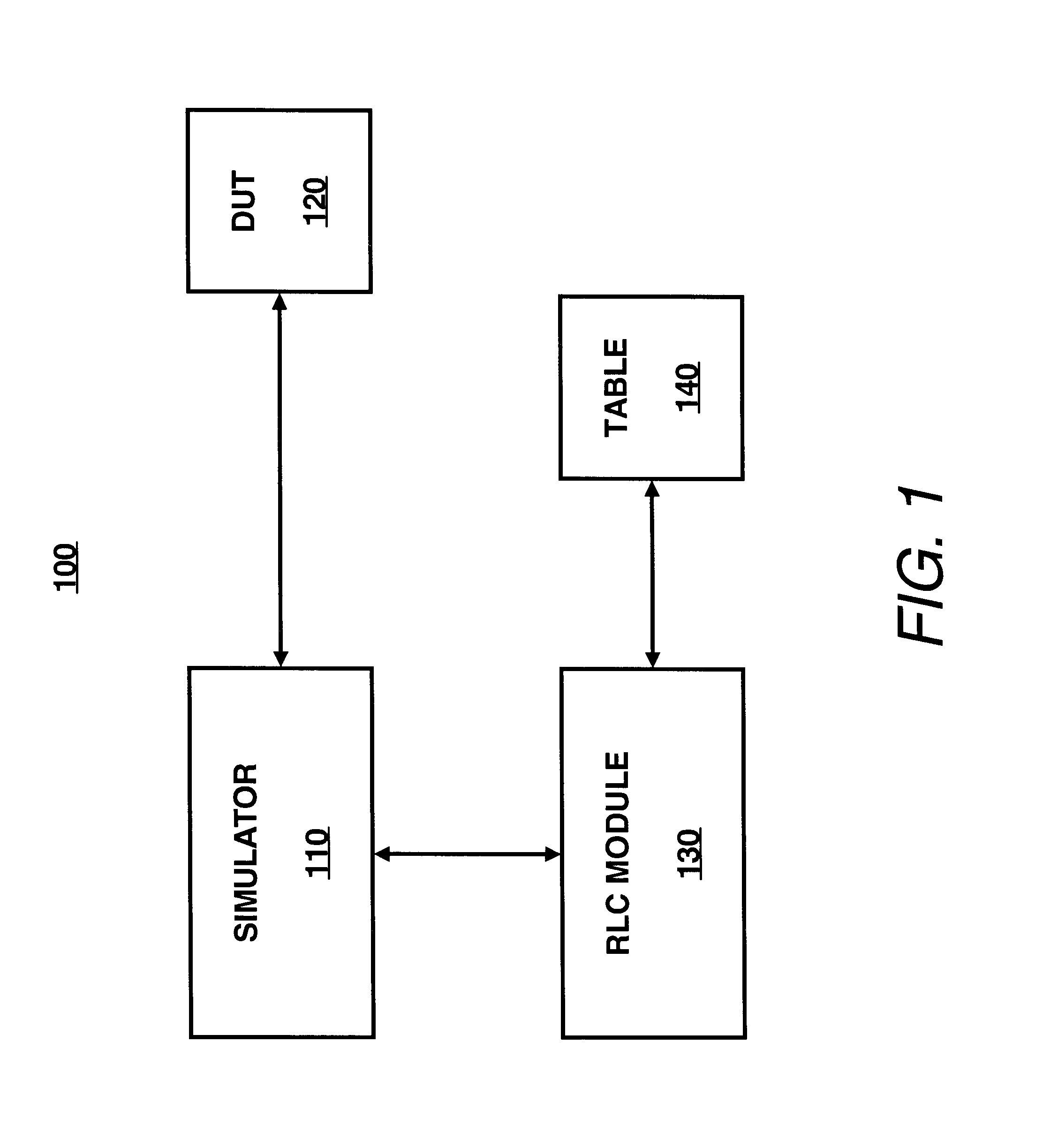

System for improving circuit simulations by utilizing a simplified circuit model based on effective capacitance and inductance values

InactiveUS6567960B2Detecting faulty computer hardwareComputer aided designCapacitanceCircuit modeling

An RLC module is configured to provide a simplified circuit modeling of a selected circuit net (or portion) of an electronic circuit. The RLC module may be configured to substitute an RLC circuit model for the selected circuit net, where the effective values of the capacitance and inductance for the RLC circuit model are retrieved from a table of capacitance and inductance values. A set of interconnect geometry factors (e.g., line length, line width, driver / receiver length, etc.) that describes the circuit net is used as an index into the table of capacitance and inductance values. The retrieved values of the effective capacitance and inductances values may be used to calculate a delay for the RLC circuit model. The RLC module may provide the capability to quickly calculate a delay for a selected circuit net without using computationally intensive calculations for inductance and capacitance values of circuit nets.

Owner:SAMSUNG ELECTRONICS CO LTD

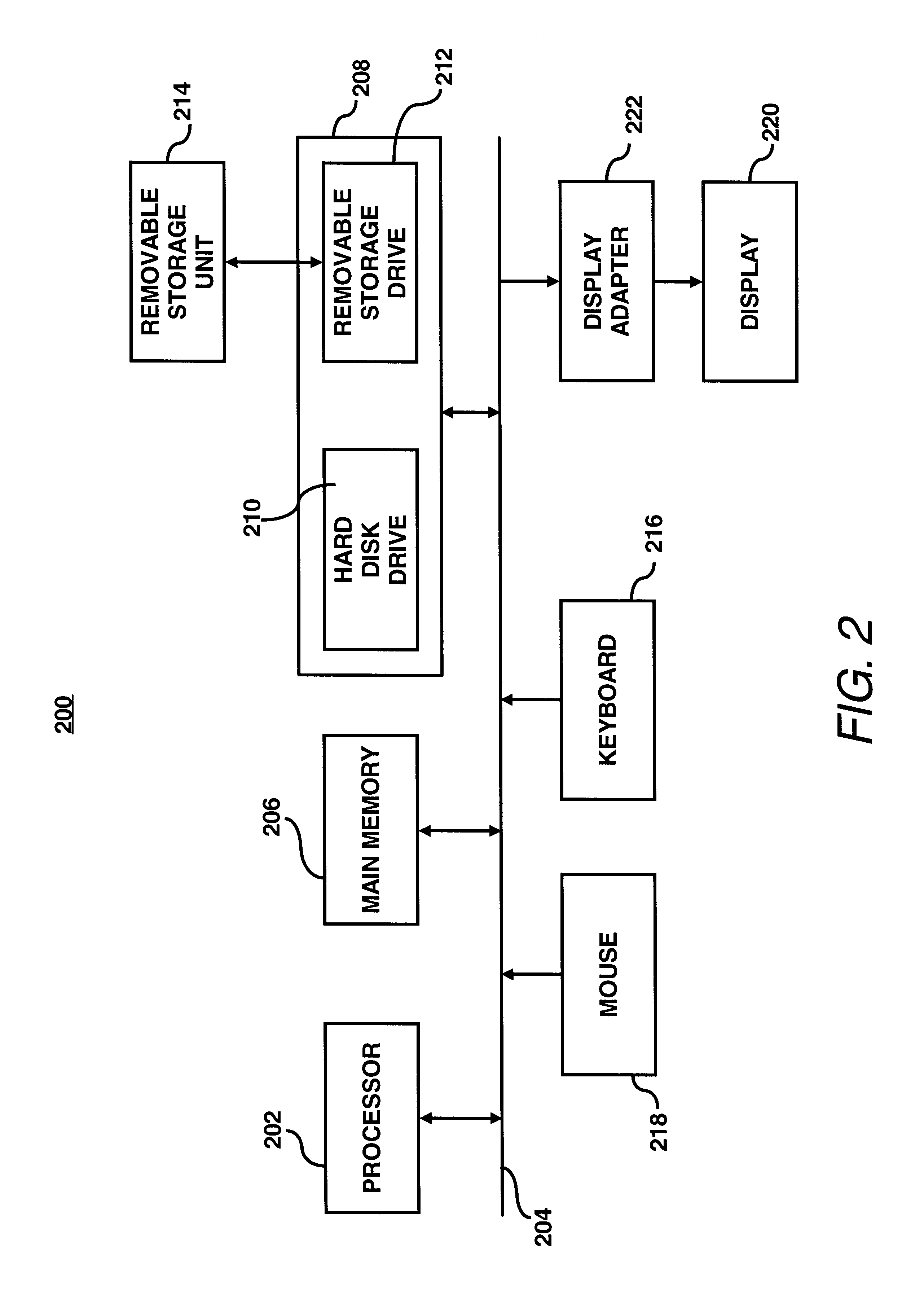

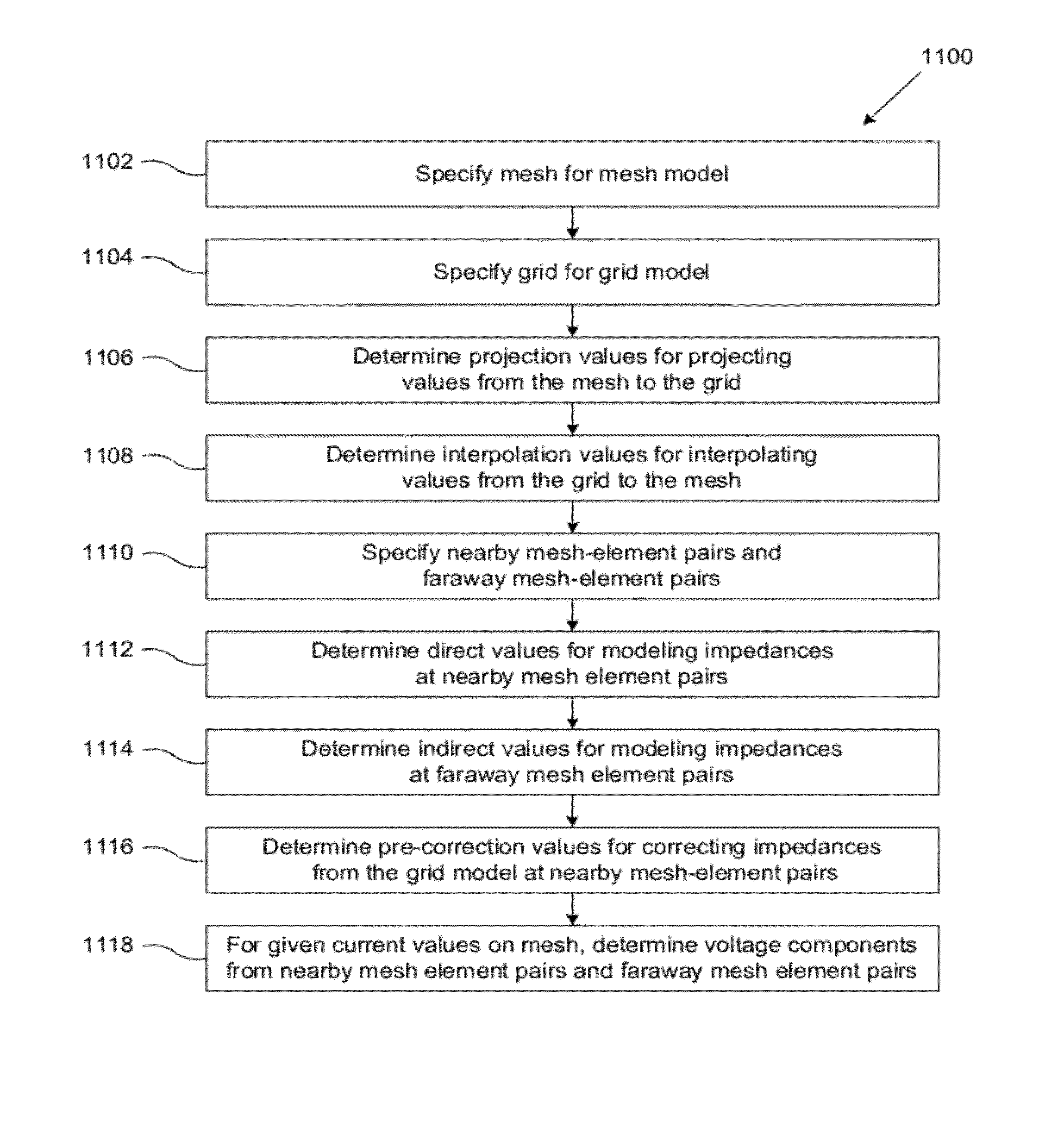

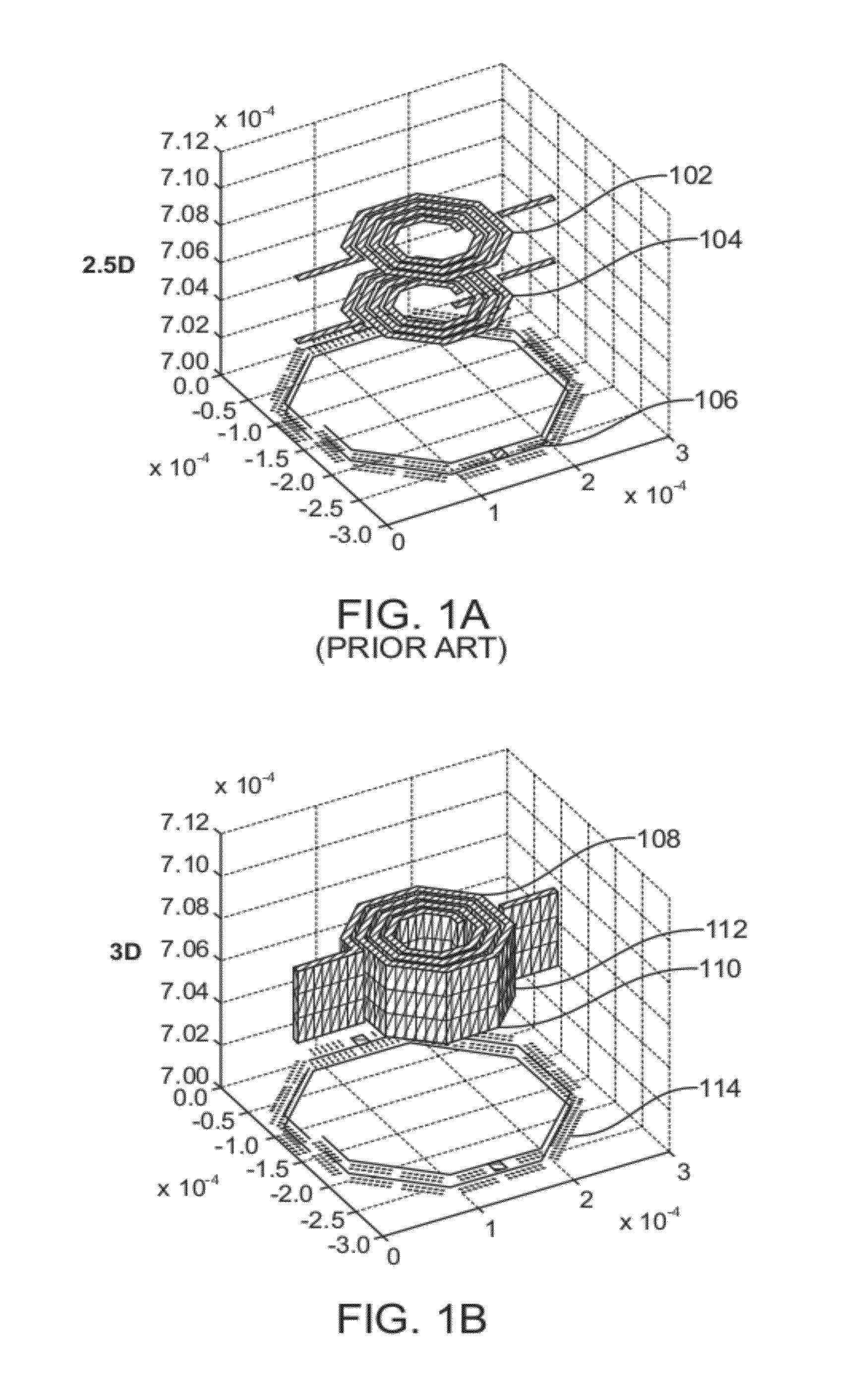

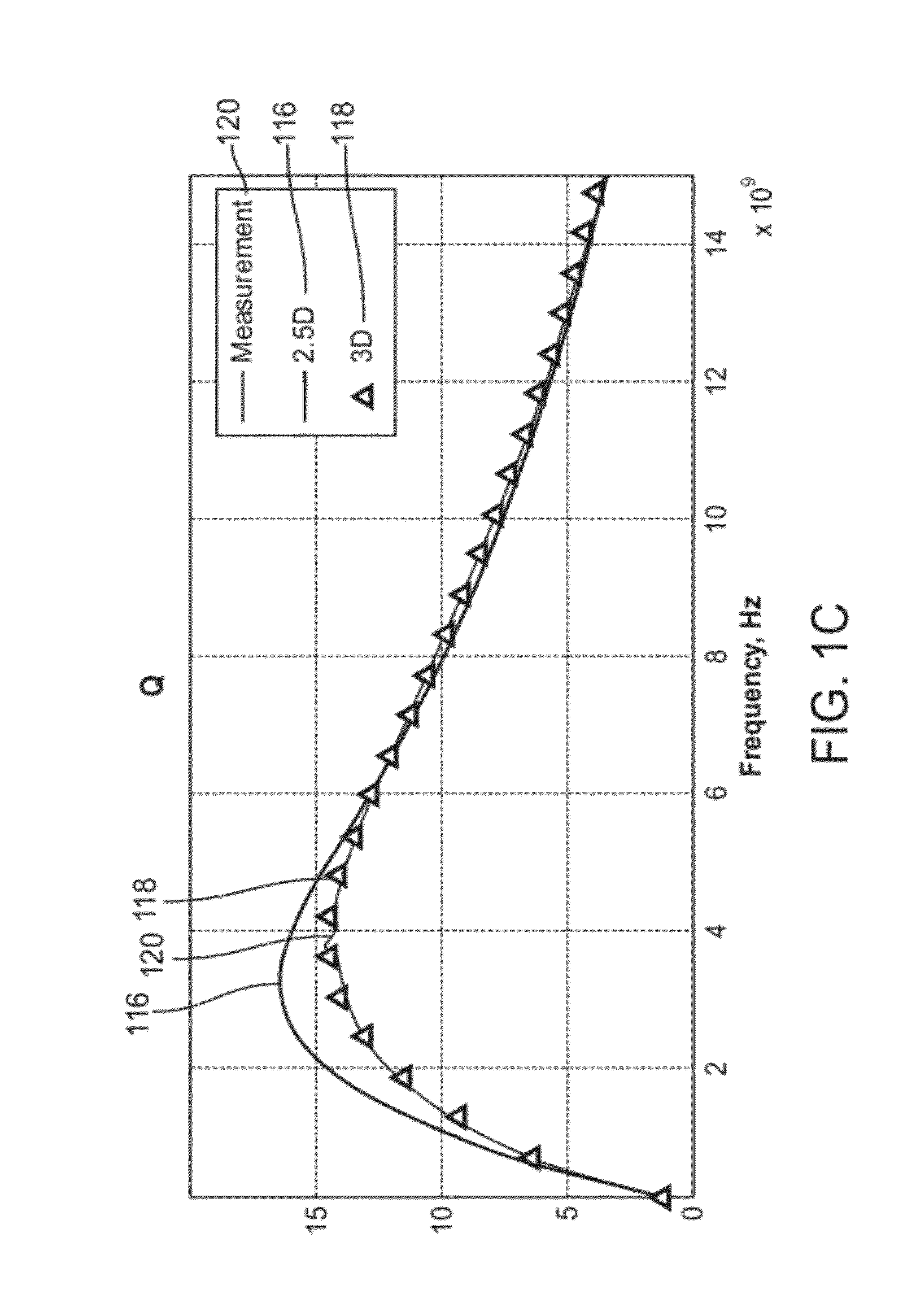

Solver for modeling a multilayered integrated circuit with three-dimensional interconnects

InactiveUS8255849B1Improve computing efficiencyDesign optimisation/simulationCAD circuit designCircuit modelingMesh model

Systems and methods for modeling a multilayer integrated circuit include three-dimensional interconnect models in multilayered substrates for greater accuracy. Mesh models are used to resolve effects of nearby elements and grid models are used to resolve effects of far-away elements. Sidewall mesh elements of three-dimensional interconnects are projected onto parallel (or substantially parallel) grids between the top and bottom walls of the interconnects so that grid models can be used to resolve three-dimensional effects of interconnects in multilayered substrates.

Owner:CADENCE DESIGN SYST INC

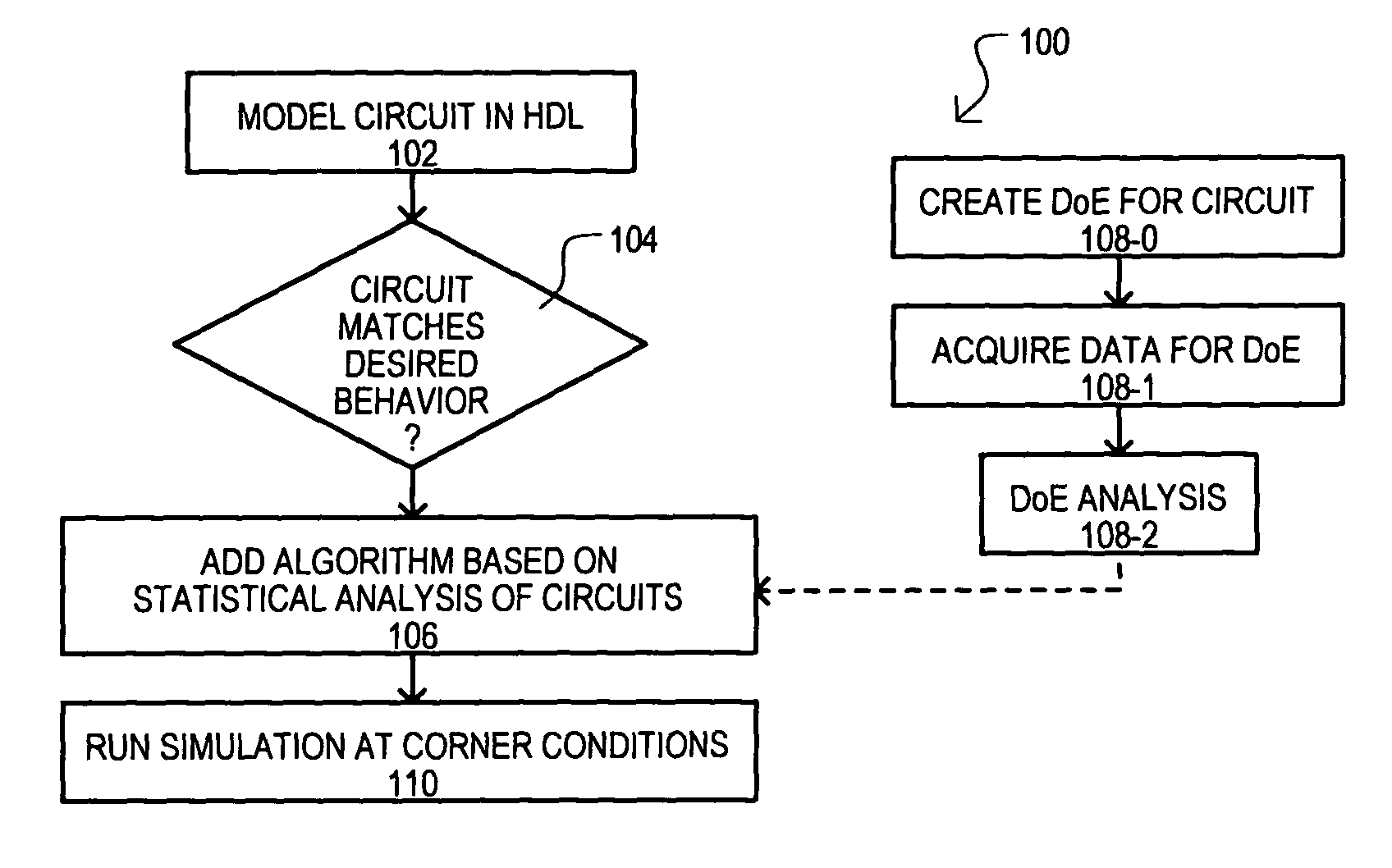

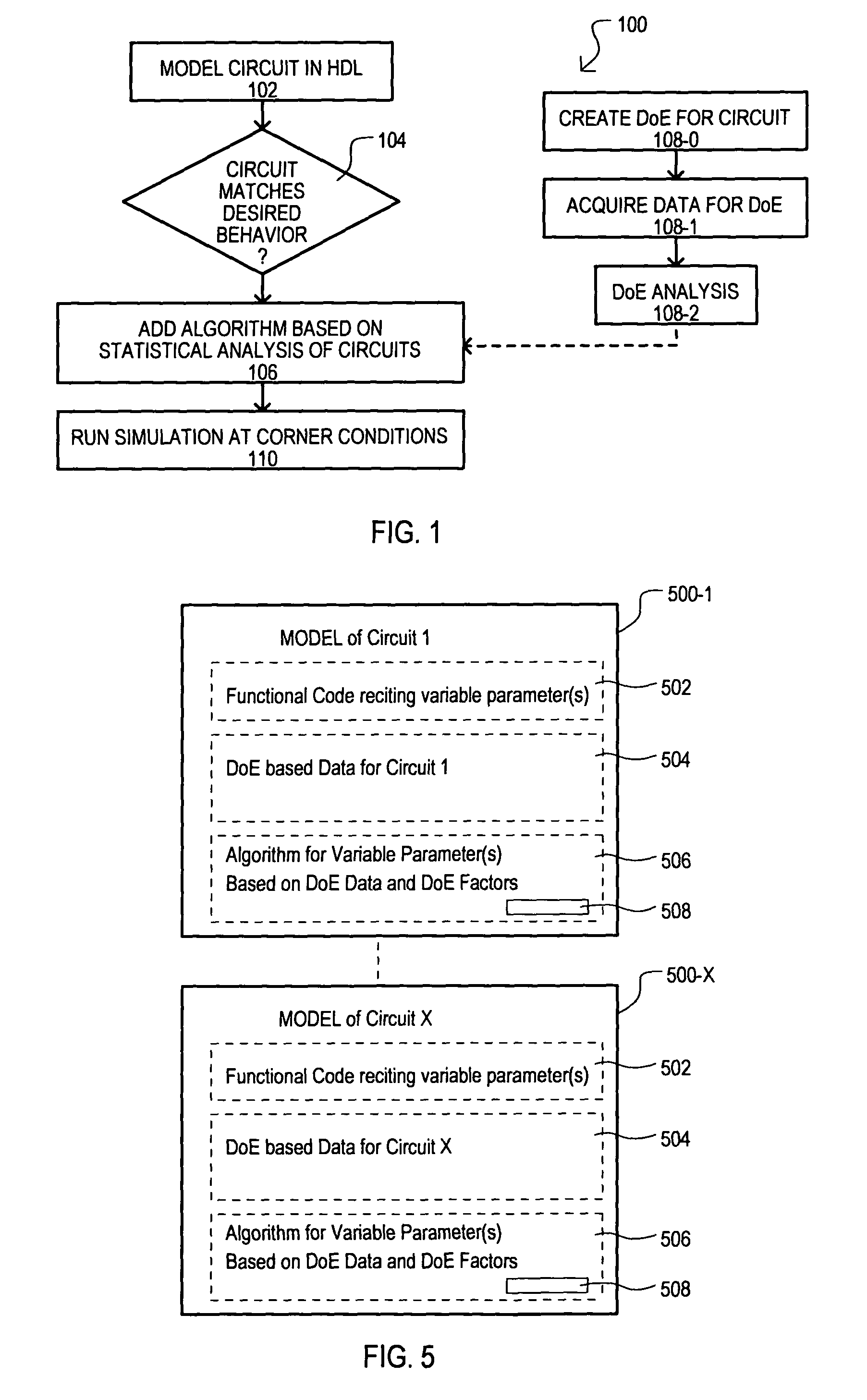

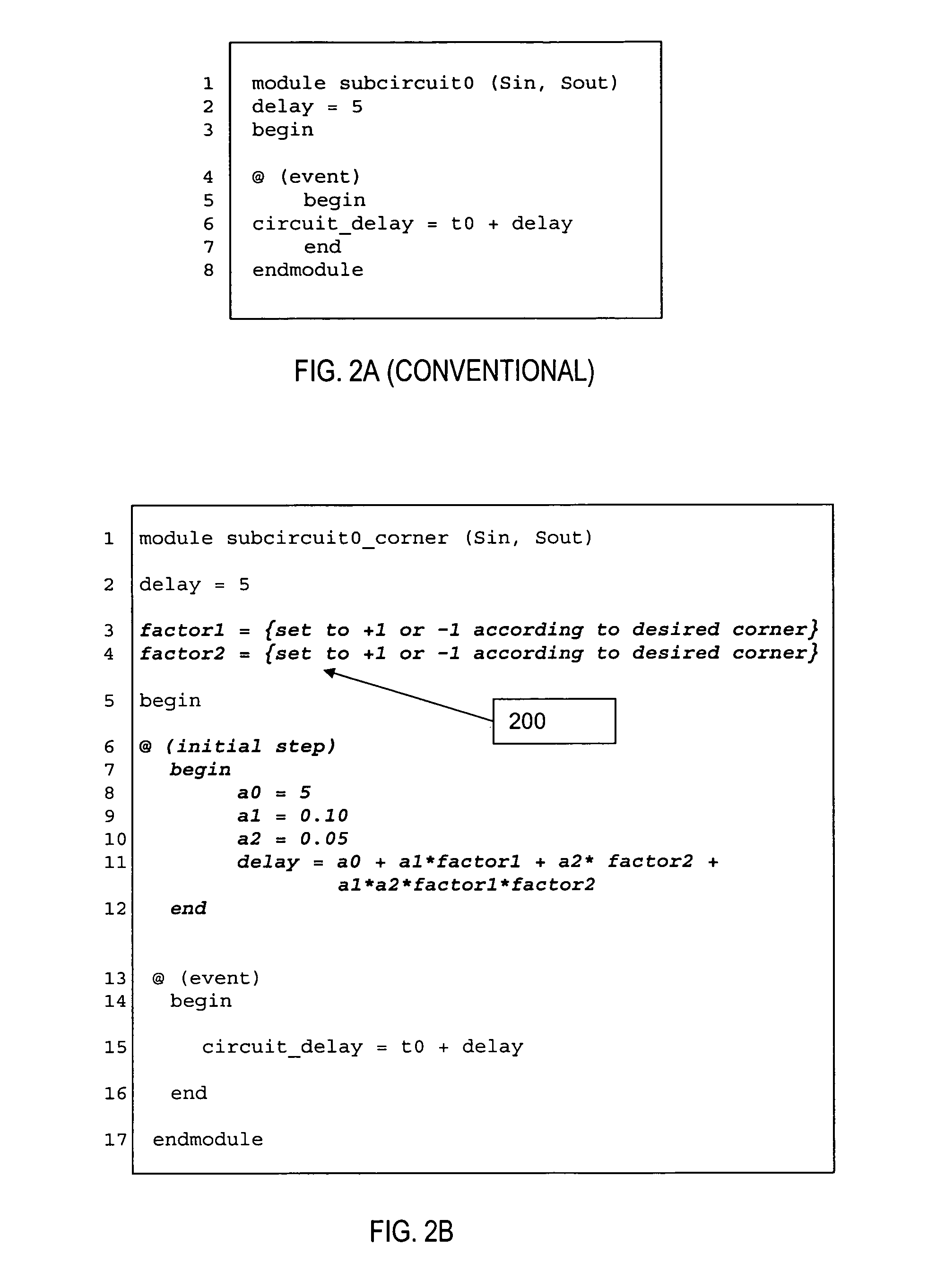

Hardware description language (HDL) incorporating statistically derived data and related methods

InactiveUS8818784B1Faster circuit simulationPreserving simulation accuracyCAD circuit designProbabilistic CADStatistical analysisCircuit modeling

A method of designing a circuit can include modeling one or more circuits in a hardware design language (HDL) (102) and confirming a basic behavior of such models (104). If a basic behavior has been met, the model can be modified to include an algorithm that is based on an experimental statistical analysis of manufactured circuits representing particular condition (e.g., factor) limits (referred to as “corners”) (106). Once a circuit model has been modified to include an algorithm that can represent performance corners, a simulation can be run that will represent circuit response at such an operational corner (110).

Owner:MONTEREY RES LLC

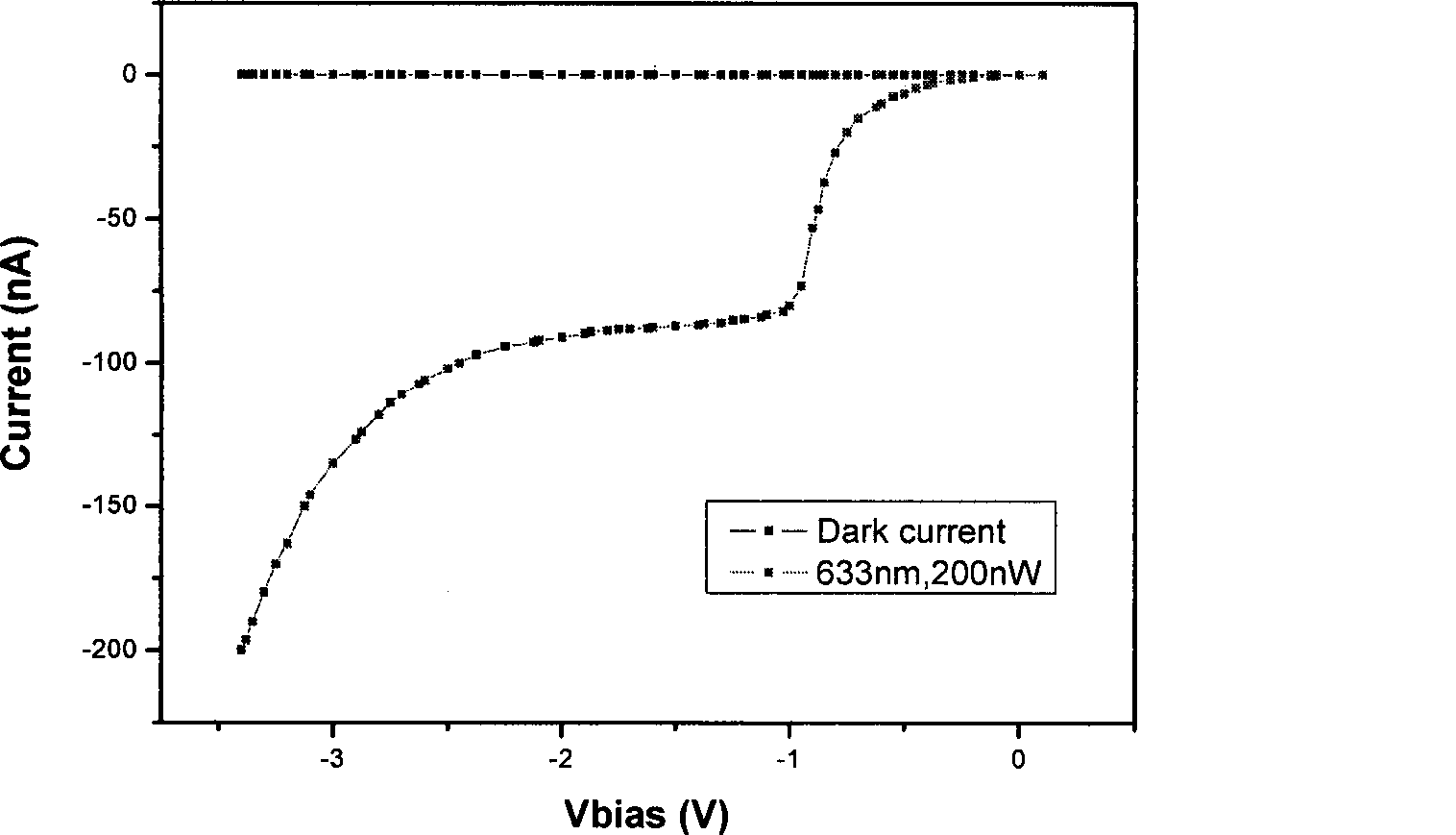

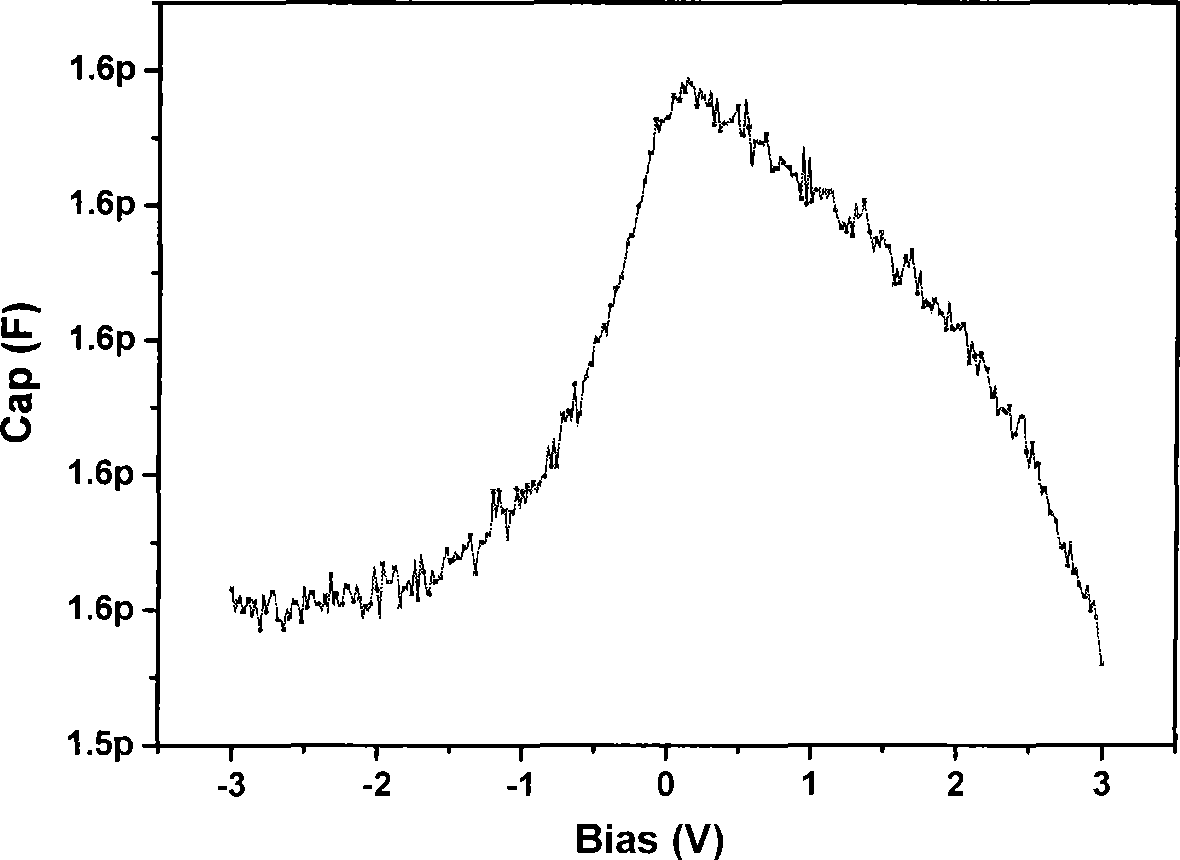

Design method for photoelectric detector reading circuit

InactiveCN101504313ASimple modeling procedureHigh precisionPhotometry electrical circuitsSpecial data processing applicationsCapacitanceCurve fitting

The invention discloses a method for designing a read-out circuit for a photoelectric detector, which is characterized in that the fitting of an electrical characteristic curve of the photoelectric detector is implemented, and functions of which the output current is the voltage and functions of which the capacitance is the voltage can be realized in an equivalent circuit model through one or more voltage-controlled current sources, capacitances and output impedances, so that the equivalent circuit model is established and corrected and improved by circuit simulation software; and finally the equivalent circuit model is taken as an input source of a CTIA type read-out structure, corresponding parameters of the read-out circuit are obtained, and the matching design of the read-out circuit for the photoelectric detector is implemented. Compared with the prior art, the method has the advantages of simple circuit modeling program, clear structure and high precision, provides great convenience for the design of the matched read-out circuit for the photoelectric detector, and has superior performances of small signal deviation and large dynamic range of the read-out circuit.

Owner:EAST CHINA NORMAL UNIV

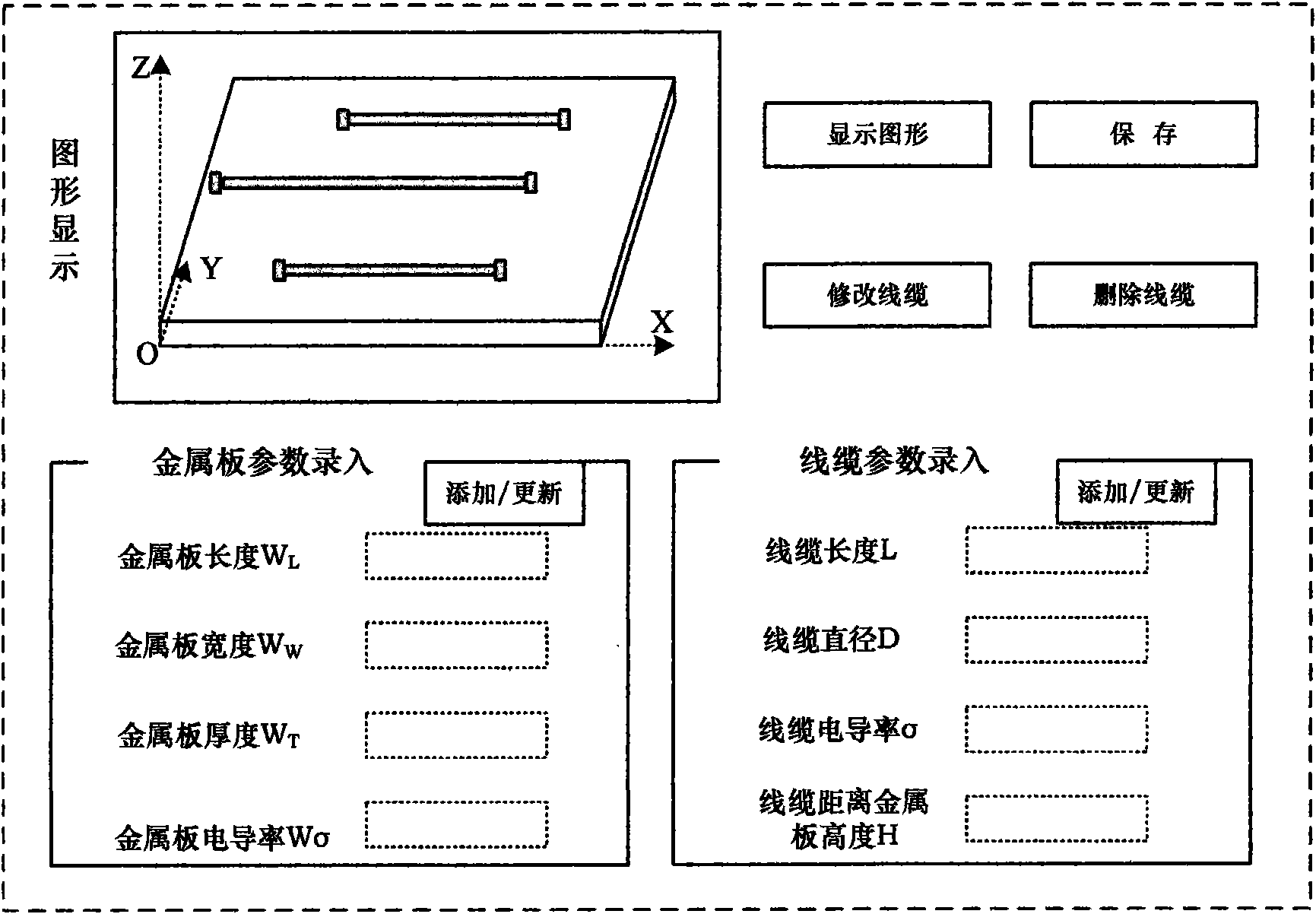

System for calculating crosstalk strength among cables based on partial element equivalent circuit (PEEC) theory

ActiveCN101667216ALive buildEasy to calculateSpecial data processing applicationsCapacitanceCoupling

The invention discloses a system for calculating crosstalk strength among cables based on a partial element equivalent circuit (PEEC) theory. The system comprises a computer and a parallel cable crosstalk module stored in the computer, wherein the parallel cable crosstalk module is redacted by applying VC++6.0 in the computer according to the PEEC theory. A parameter input and configuration unit acquires a cable configuration picture of cables and a metal plate according to configuration parameters; an SPICE circuit modeling unit carries out conversion process by adopting the PEEC theory to obtain an SPICE circuit; and an interference strength analysis unit obtains the crosstalk coupling interference strength of near-end equipment and far-end equipment of parallel cables according to an exciting source and a load which are loaded on the SPICE circuit. By adopting the PEEC theory to analyze the crosstalk among the cables, the invention can accurately and effectively calculate the coupling induction and the coupling capacitance between the cables and obtain the crosstalk strength between the cables.

Owner:BEIHANG UNIV

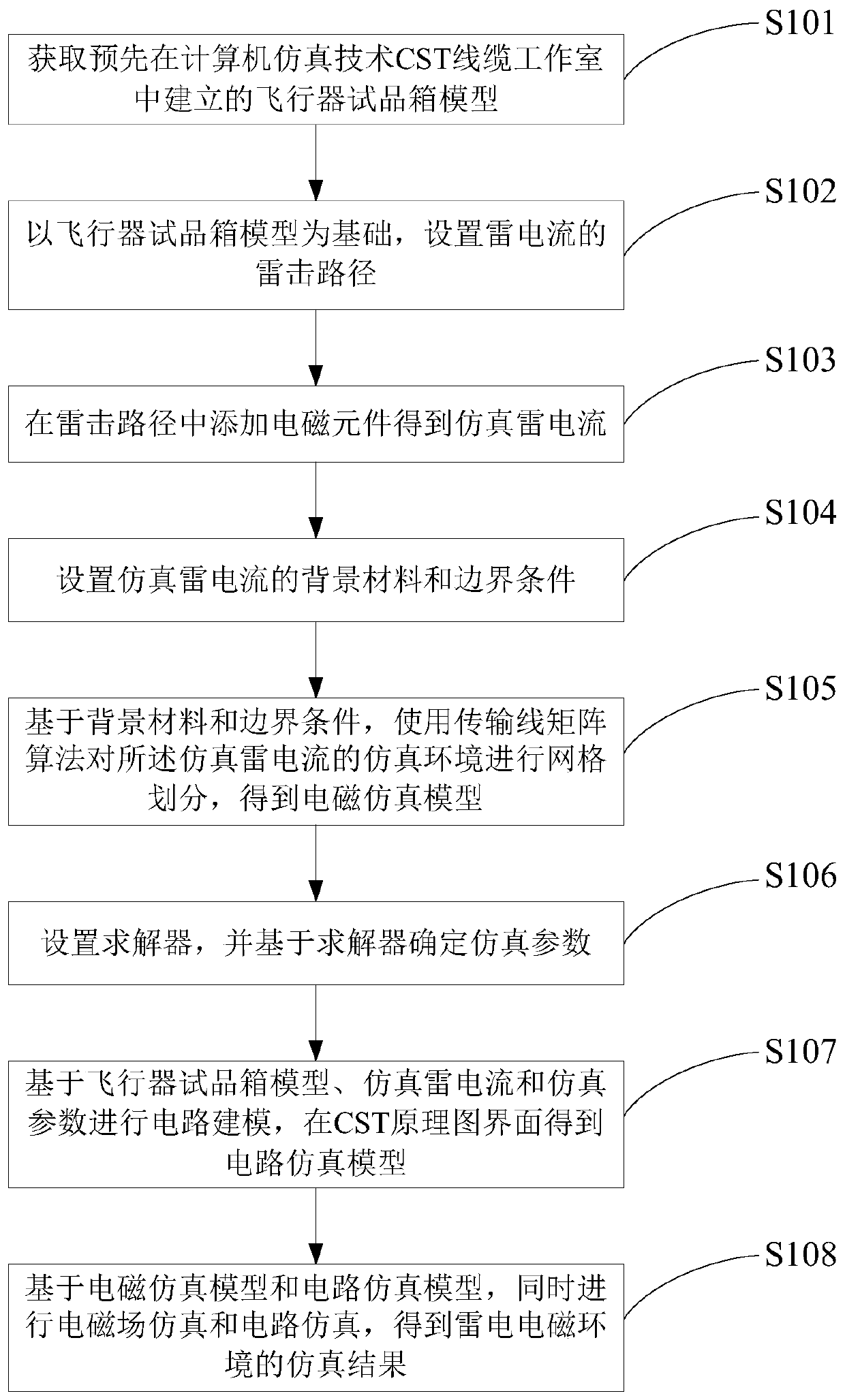

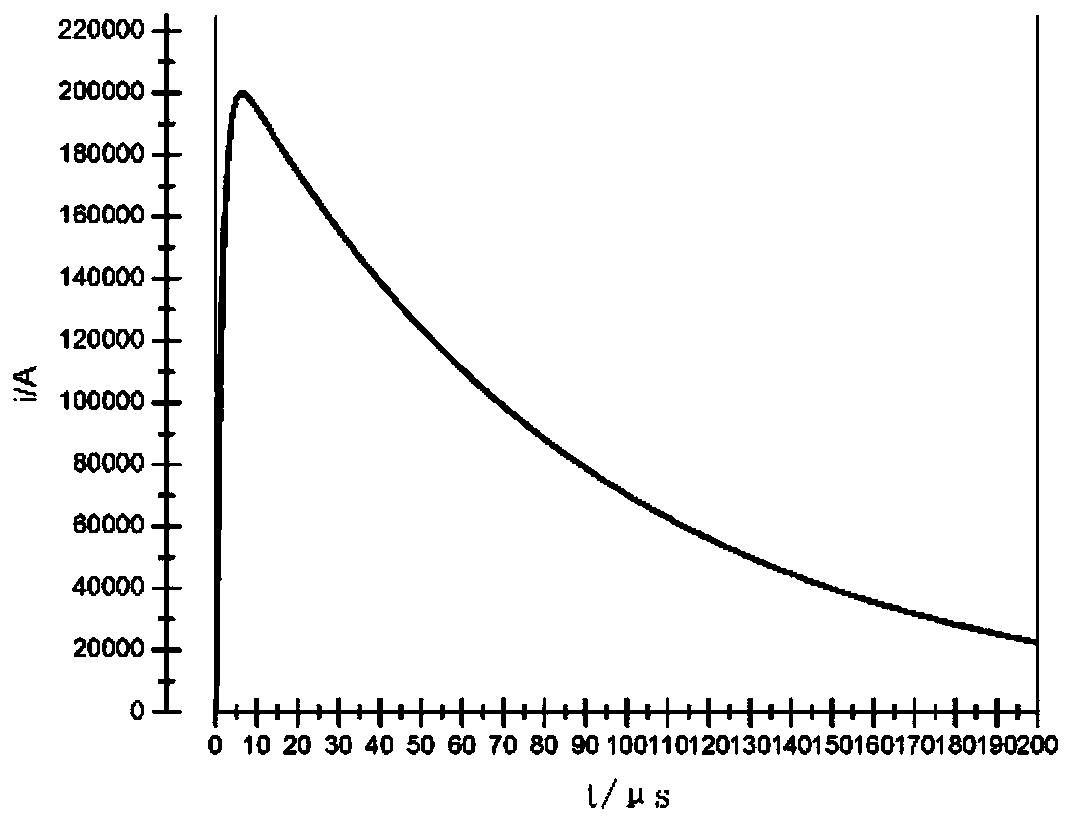

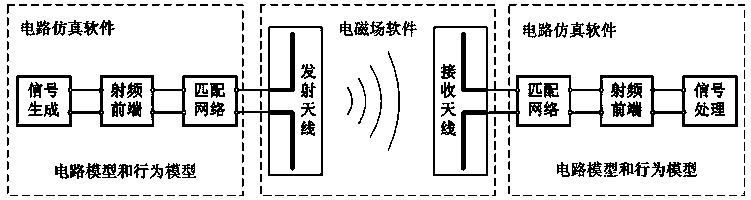

Lightning electromagnetic environment simulation method and system

ActiveCN110516397ASimulation is intuitive and vividConvenient verificationSpecial data processing applicationsLightning strokesCircuit modeling

The invention discloses a lightning electromagnetic environment simulation method and system. The method comprises steps of acquiring an aircraft sample box model established in a CST cable working chamber; setting a lightning stroke path of the lightning current based on the model; adding an electromagnetic element in the lightning stroke path to obtain a simulated lightning current; setting a background material and a boundary condition of the simulated lightning current; using a transmission line matrix algorithm to carry out mesh generation on a simulation environment to obtain an electromagnetic simulation model, determining simulation parameters based on a set solver, performing circuit modeling based on an aircraft sample box model, simulation lightning current and the simulation parameters to obtain a circuit simulation model, and performing electromagnetic field simulation and circuit simulation simultaneously based on the electromagnetic simulation model and the circuit simulation model to obtain a simulation result of a lightning electromagnetic environment. The CST platform is used for lightning electromagnetic environment analysis, the CST platform has the advantages of being convenient to verify, flexible, accurate and low in cost, and simulation of the electromagnetic environment can be visually and vividly achieved without complex work.

Owner:NANHUA UNIV

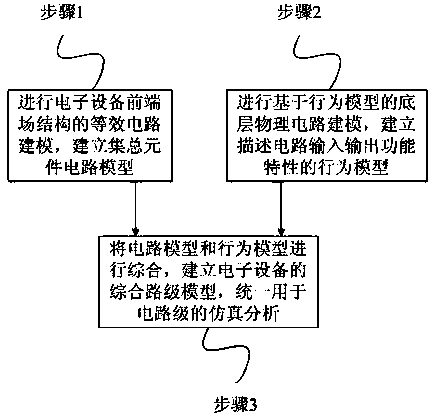

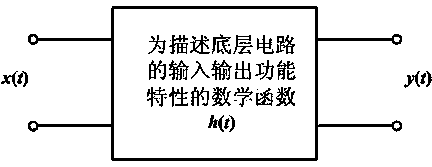

Behavioral model-based electromagnetic compatibility circuit-level integrated modeling method for electronic equipment

InactiveCN104392022AQuick calculationSimple calculationSpecial data processing applicationsCircuit modelingData interface

The invention discloses a behavioral model-based electromagnetic compatibility circuit-level integrated modeling method for electronic equipment. The behavioral model-based electromagnetic compatibility circuit-level integrated modeling method comprises the following steps: firstly, performing equivalent circuit modeling of a front-end field structure of the electronic equipment; establishing a lumped element circuit model; then, performing behavioral model-based bottom layer physical circuit modeling; establishing a behavioral model for describing the input / output functional characteristics of a circuit; finally, performing integration on the lumped element circuit model and the behavioral model for describing the input / output functional characteristics of the circuit, and establishing an integrated circuit-level model of the electronic equipment, wherein the integrated circuit-level model is uniformly used for simulated analysis of a circuit level. According to the behavioral model-based electromagnetic compatibility circuit-level integrated modeling method disclosed by the invention, calculation is simplified, and a data interface for traditional field-circuit collaborative analysis is omitted, and the problem that a large number of product differential equations are difficult to solve due to high integration level of the circuit in a system and high complexity of digital-analog hybrid is solved; the behavioral model and the circuit model can also mutually compatible, so that the analysis efficiency is improved; the established integrated circuit model is high in universality; parameters of the model can be flexibly adjusted according to the performance of the electronic equipment; the behavioral model-based electromagnetic compatibility circuit-level integrated modeling method is simple, and is easy to implement.

Owner:SHANGHAI RADIO EQUIP RES INST

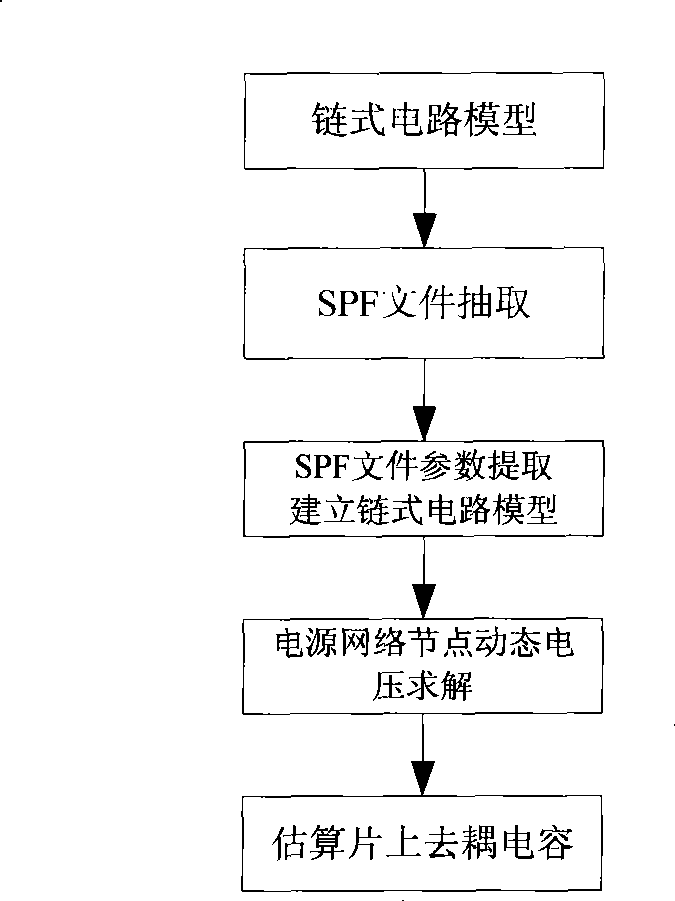

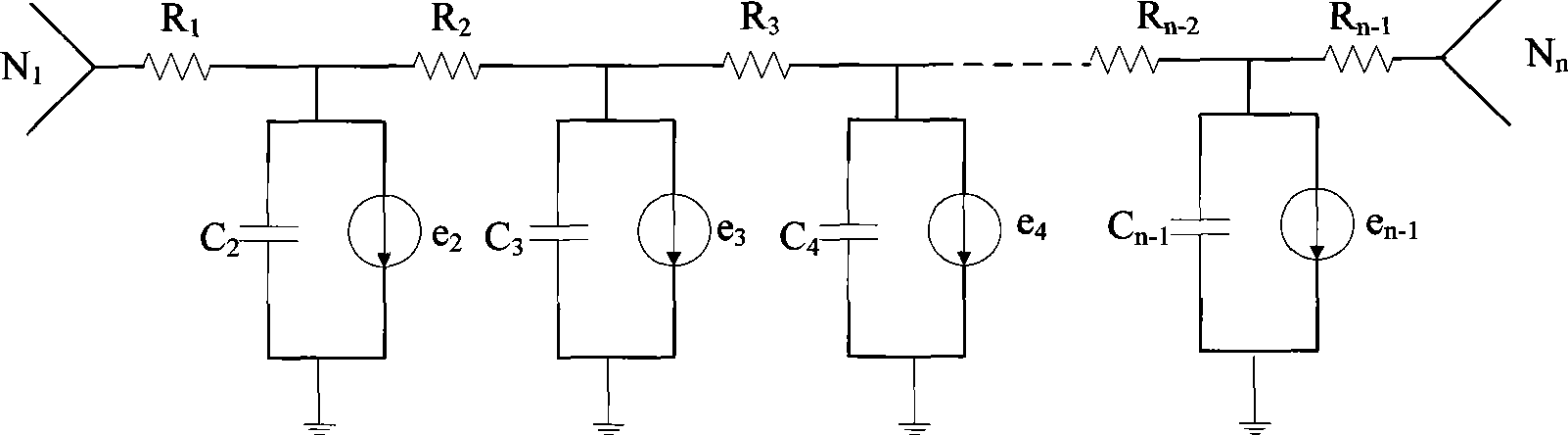

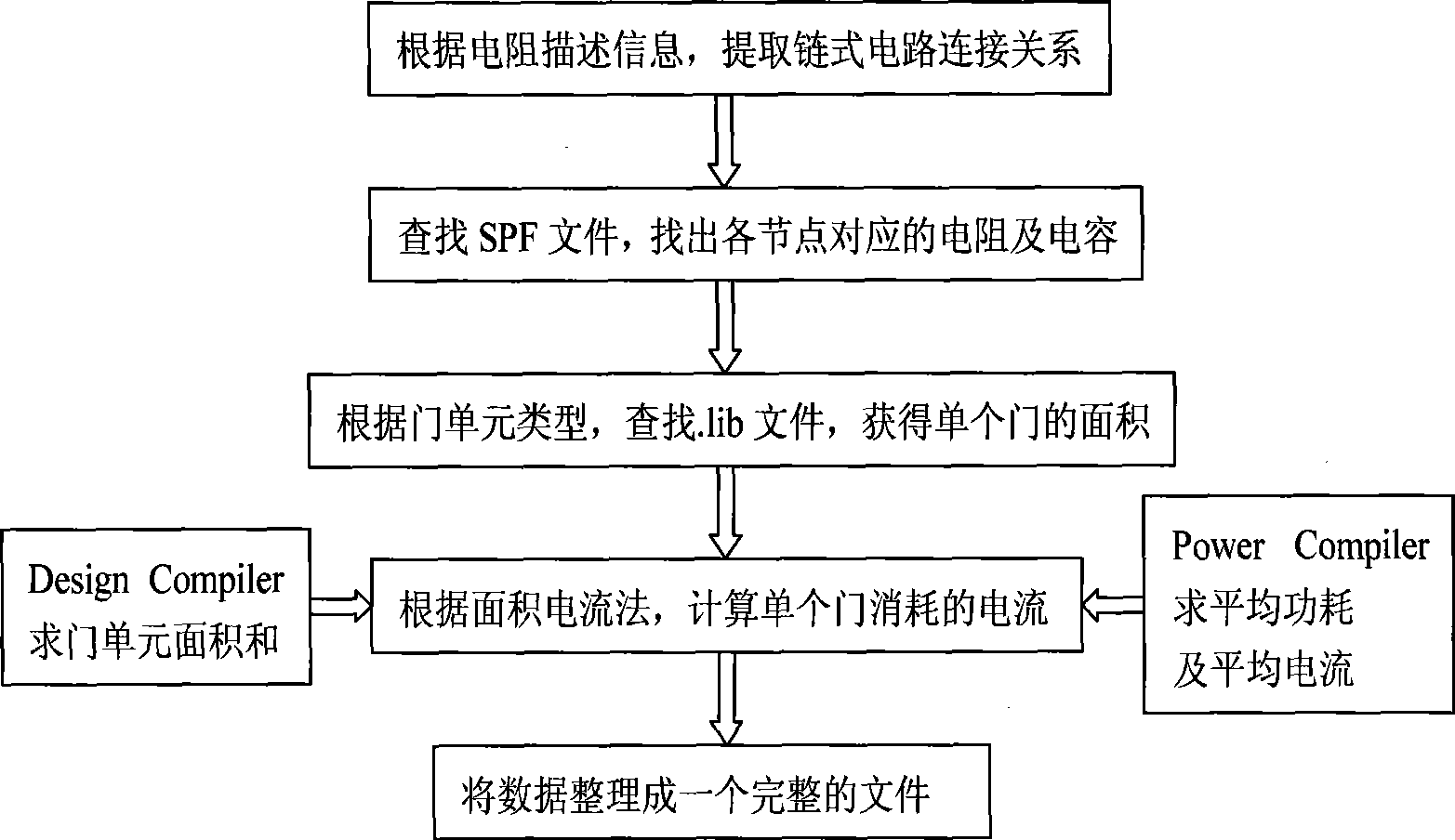

Evaluation method for decoupling capacitor on ASIC sheet based on chain circuit

ActiveCN101504681ASuppresses voltage fluctuationsSmall pressure dropCAD circuit designSpecial data processing applicationsCapacitanceCircuit modeling

The invention discloses a method for estimating the decoupling capacitors on a chip of an ASIC based on a chain circuit, and belongs to the field of estimation of the decoupling capacitors in inhibition of mains voltage fluctuation. The method comprises: firstly, adopting Star-RCXT to extract parasitic parameters of the ASIC after wiring, and using Perl to analyze the SPF file format and included information for the modeling of the chain circuit; secondly, using an Euler formula to realize the equivalence of the capacitors, and compressing the circuit by a Y-delta conversion method; thirdly, solving the voltage and the current of various nodes of a compressor circuit, and restoring the solving of the chain circuit; and fourthly, adopting integral idea to obtain the number of decoupling capacitors required to be added according to the principle that the voltage fluctuation of the nodes cannot exceed 10 percent of the mains voltage. The method estimates the number of the decoupling capacitors on a chip required to be added between power ground wires, makes the amplitude of mains fluctuation not exceed 10 percent of the mains voltage, and effectively solves the problem of voltage drop of a power network.

Owner:SOUTHEAST UNIV

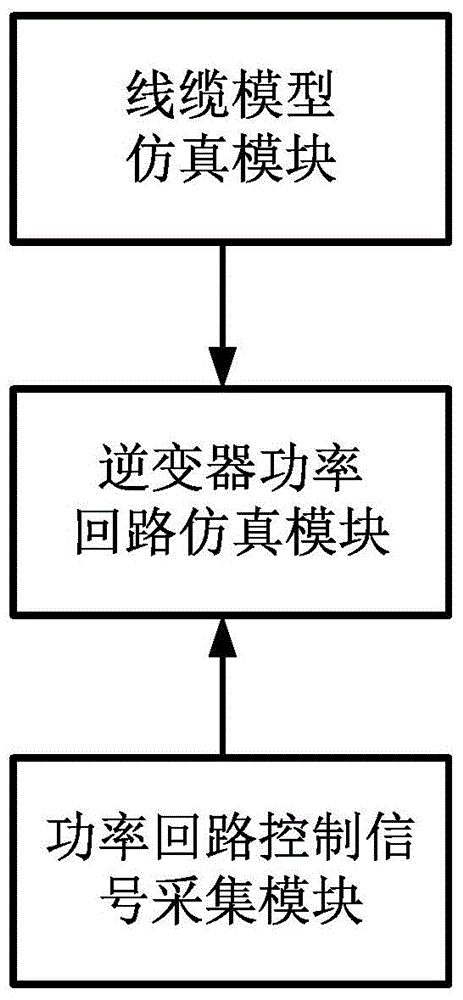

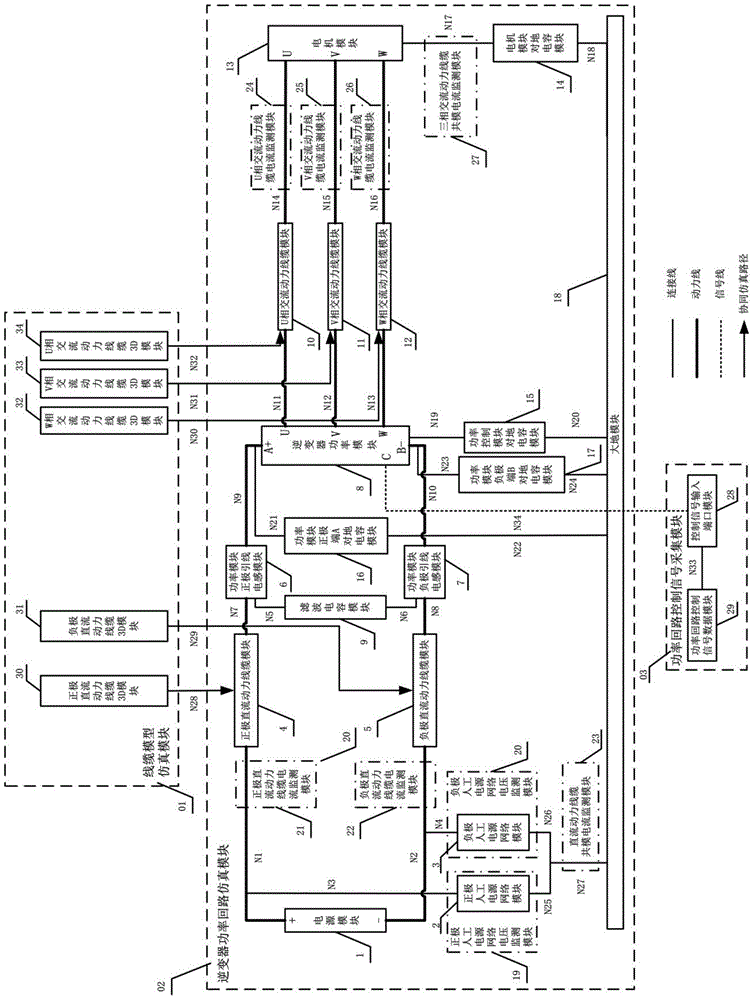

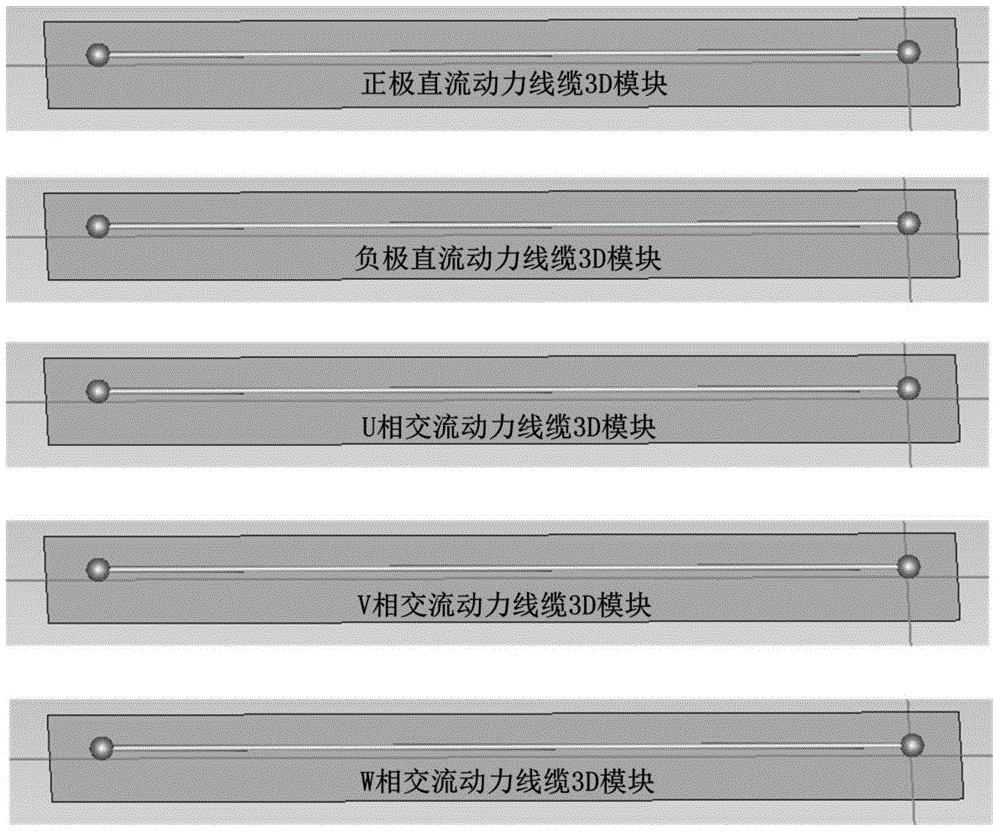

Conduction electromagnetic interference simulation system for alternating-current motor inverter power circuit of electric car

ActiveCN104698860ASave resourcesConducted electromagnetic interference to achieveSimulator controlControl signalMathematical simulation

The invention relates to a conduction electromagnetic interference simulation system for an alternating-current motor inverter power circuit of an electric car. The system comprises a cable model simulation module, an inverter power circuit simulation module and a power circuit signal acquisition module. The system is mainly used for analyzing the electric car motor drive system conduction electromagnetic interference production mechanism and propagation path. A cable model simulation module is established under electromagnetic compatibility cable modeling and simulation software, an inverter power circuit simulation module is established under electromagnetic compatibility high-frequency circuit modeling and simulation software, and a power circuit control signal acquisition module is established under mathematical simulation software. During simulation, the power circuit control signal acquisition module inputs control signals to the inverter power circuit simulation module to control the operation of the inverter, and a voltage monitoring module and a current monitoring module of the inverter power circuit simulation module are used for acquiring the power circuit voltage and current.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Method and apparatus for incrementally computing criticality and yield gradient

In one embodiment, the invention is a method and apparatus for incrementally computing criticality and yield gradient. One embodiment of a method for computing a diagnostic metric for a circuit includes modeling the circuit as a timing graph, determining a chip slack for the circuit, determining a slack of at least one diagnostic entity, and computing a diagnostic metric relating to the diagnostic entity(ies) from the chip slack and the slack of the diagnostic entity(ies).

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

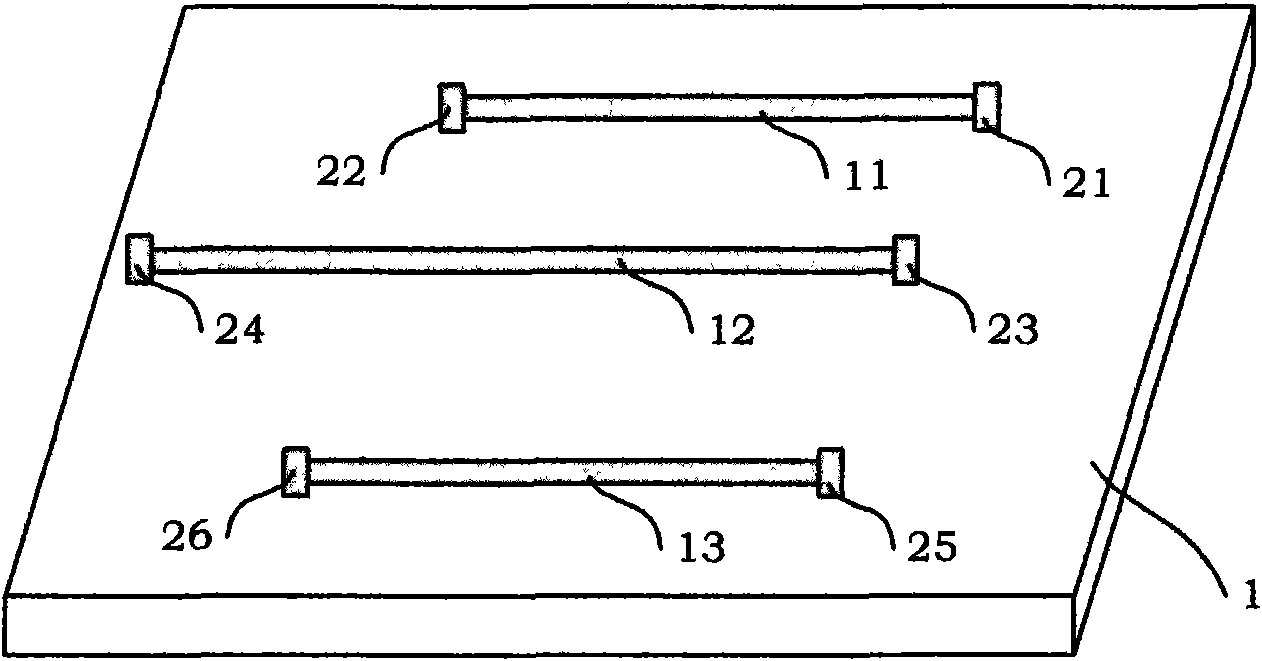

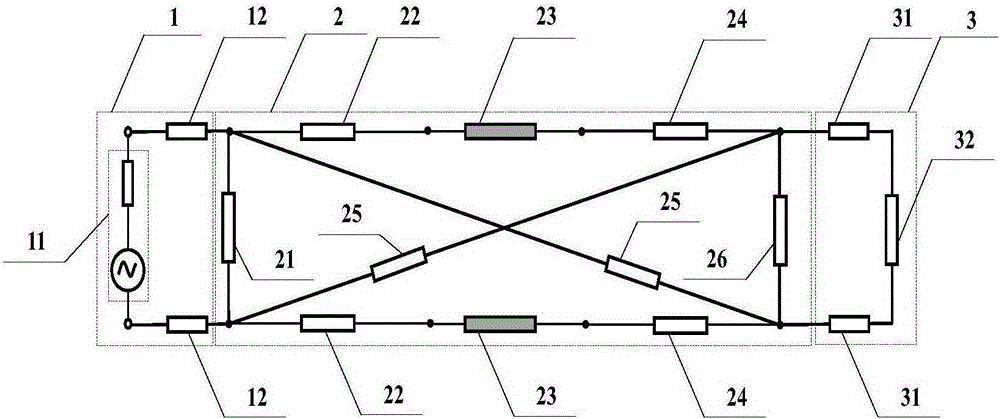

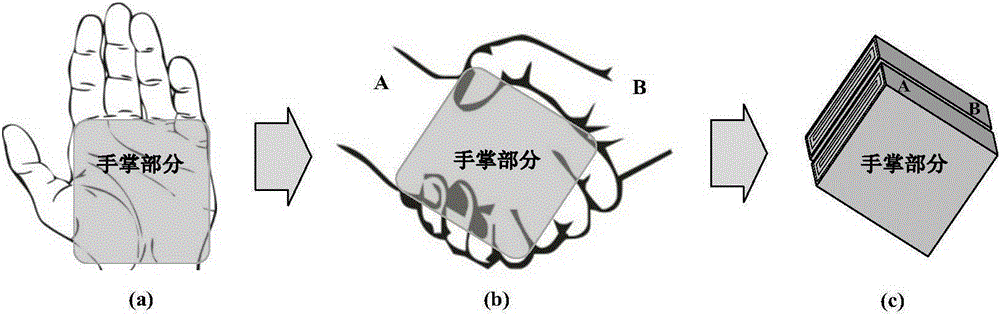

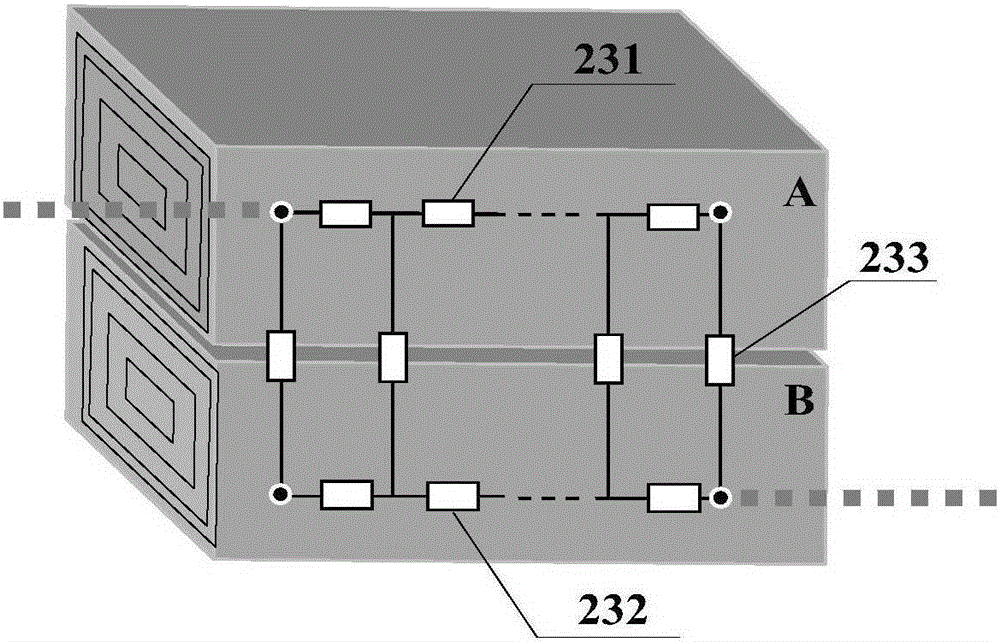

Information interaction modeling method and device based on current coupling type IBC

ActiveCN105320823ARealize interactive mathematical simulationEnsure safetySpecial data processing applicationsSystems designMathematical model

The invention belongs to the technical field of intra-body communication, and particularly relates to an information interaction modeling method and device based on the current coupling type IBC. The method comprises the steps that firstly, circuit modeling is carried out on an information interaction channel based on the current coupling type IBC to form an overall circuit model; secondly, according to the obtained overall circuit model, circuit modeling is carried out on contact resistance caused by body contact; thirdly, by means of the overall circuit model, an information interaction complete circuit model based on the current coupling type IBC is formed; finally, based on the built complete circuit model, an information interaction mathematic model based on the current coupling type IBC is obtained through circuit analysis. Compared with the prior art, safety guarantee is provided for information interaction based on the current coupling type IBC, the system design basis is provided for the design of the information interaction device based on the current coupling type IBC, the problems of geometric modeling, circuit modeling and mathematic modeling between two living bodies and an electronic device are solved, and the reference is provided for relevant research and design.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

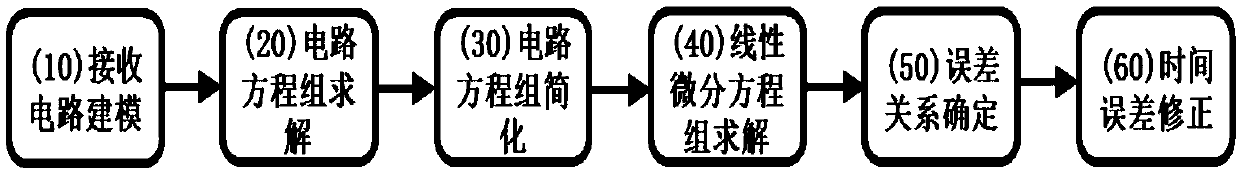

Pulse laser ranging system transistor type receiving circuit error correcting method

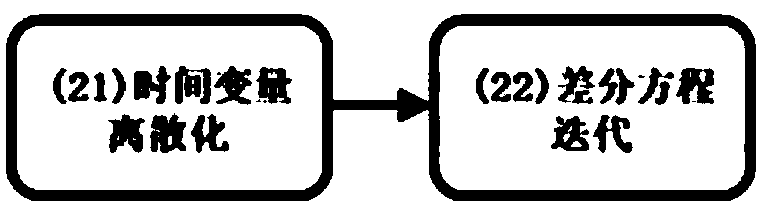

ActiveCN109633610AHigh measurement accuracyAccurate walk errorWave based measurement systemsTime errorDiscretization

The invention discloses a pulse laser ranging system transistor type receiving circuit error correcting method. The pulse laser ranging system transistor type receiving circuit error correcting methodcomprises the following steps that (10) a circuit modeling is received, wherein a circuit equation set is listed according to a circuit structure and a transistor classic model; (20) a circuit equation set is solved, wherein a numerical value approximation solution of the circuit equation set is solved by means of discretization and numerical analysis; (30) the circuit equation set is simplified,wherein the circuit equation set is reserved according to the numerical value approximation solution of the circuit equation set; (40) a linear differential equation set is solved, the linear differential equation set is solved to obtain an approximate relation between the walking error and the input current; (50) an error relation is determined, wherein a double-threshold moment is substituted into the approximate relation to obtain the relation between the walking error and the double-threshold moment; and (60) time error is corrected, wherein the specific numerical value of the double-threshold moment is substituted into the relation to obtain an error value, and the error value is subtracted from the time interval to obtain an accurate time interval. The error correcting method is small in error and high in system measuring precision.

Owner:NANJING UNIV OF SCI & TECH +1