Multi-clock system-on-chip with universal clock control modules for transition fault test at speed multi-core

A clock control module and multi-clock technology, which is applied in digital circuit testing, electronic circuit testing, electrical measurement, etc., can solve problems that depend on multi-clock chip-based system design, complexity, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

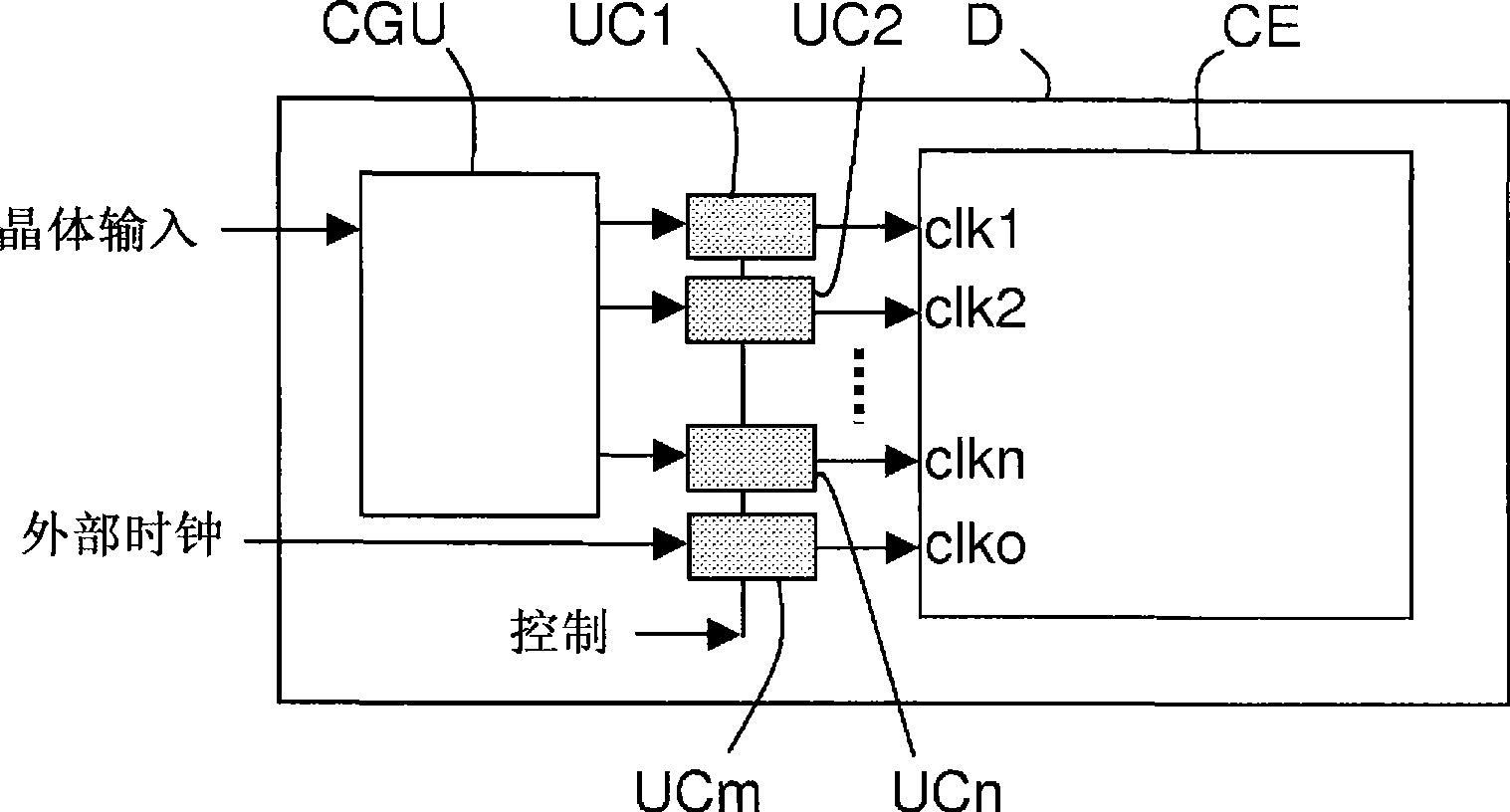

[0019] initial reference figure 2 Let us introduce the multi-clock chip-based system D according to the present invention.

[0020] In the following presentation a multi-clock chip-based system D equipped with an electronic device such as a mobile phone will be considered as an example. However, the present invention is not limited to this type of electronic device (or application). It applies to any type of electronic device that may or may not be suitable for communication (telecommunications) and that requires at least one core (i.e. processor or microcontroller) to execute a program (or software(s)) or commands . So, it could also be eg a Personal Digital Assistant (PDA), a computer (possibly portable), a game or an audio or video player, a television or a set top box.

[0021] Also in the following description, a multi-clock chip-based system D comprising only one core will be considered in order to simplify the description of the invention. However, the present inve...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com