Effective use of a bht in processor having variable length instruction set execution modes

A technology of execution mode and instruction set, applied in the field of effective organization of branch history table, can solve the problems of increasing cycle time, affecting processor performance, increasing silicon area and power consumption, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

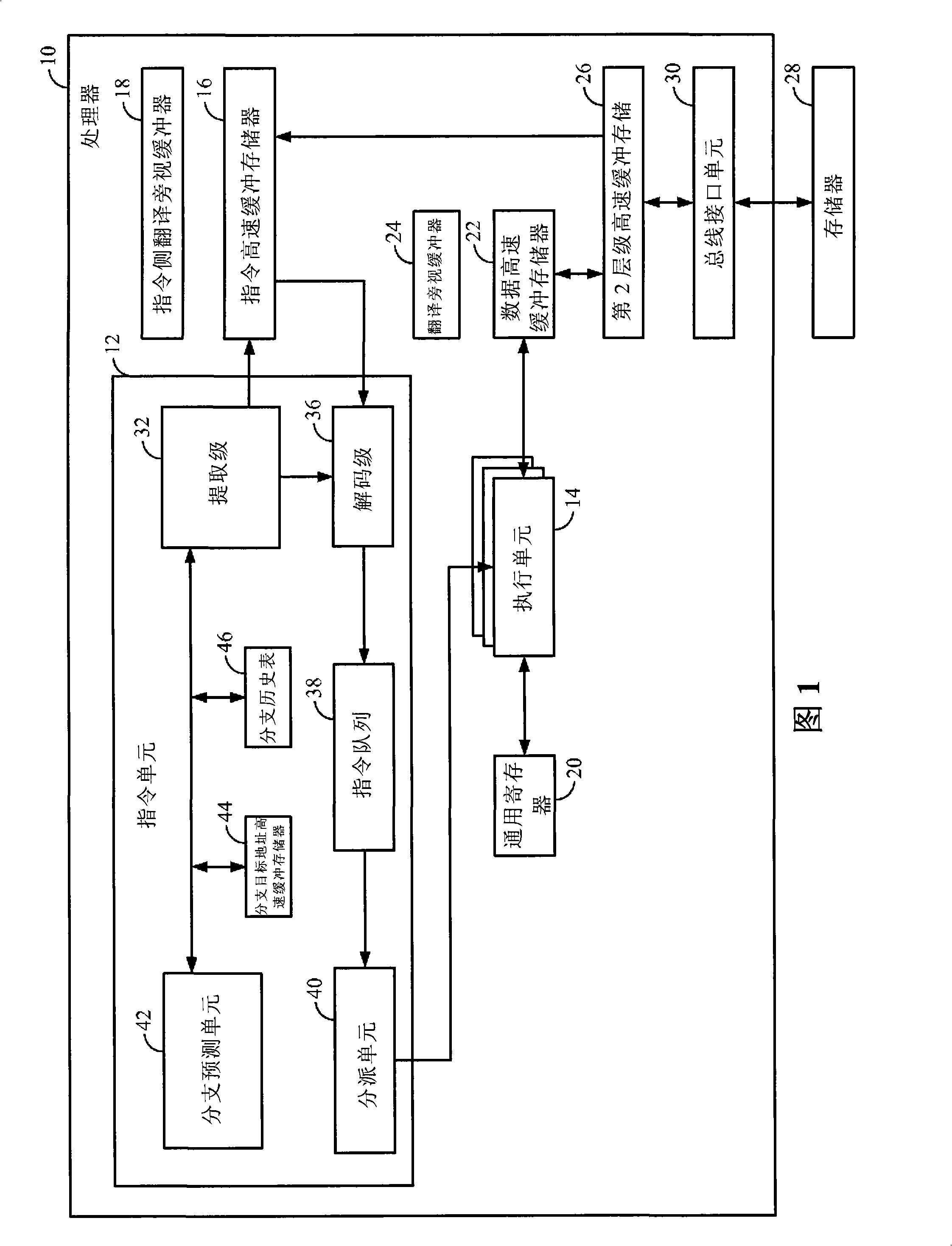

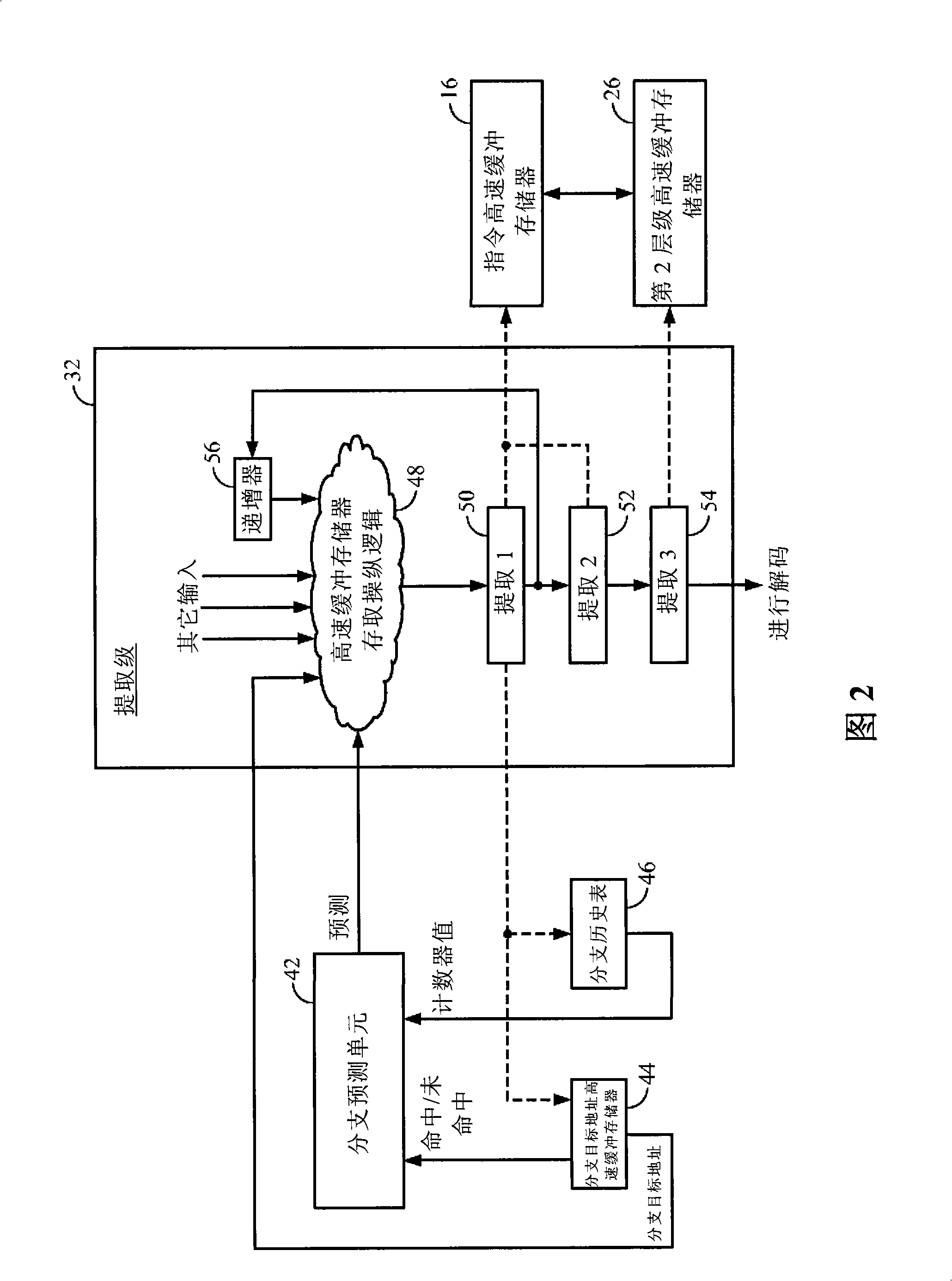

[0024] figure 1 A functional block diagram of processor 10 is depicted. Processor 10 includes an instruction unit 12 and one or more execution units 14 . Instruction unit 12 provides centralized control over the flow of instructions to execution unit 14 . The instruction unit 12 fetches instructions from an instruction cache 16 , where memory address translation and permissions are managed by an instruction side translation lookaside buffer (ITLB) 18 .

[0025] The execution unit 14 executes the instructions dispatched by the instruction unit 12 . Execution units 14 read and write general purpose registers (GPR) 20 and access data from data cache 22 , where memory address translation and permissions are managed by main translation lookaside buffer (TLB) 24 . In various embodiments, ITLB 18 may include a replica of portions of TLB 24 . Alternatively, the ITLB 18 and TLB 24 could be integrated. Similarly, in various embodiments of processor 10, instruction cache 16 and data...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More