Information processing device, memory control method, and memory control device

A technology for information processing devices and control devices, which is applied in memory systems, electrical digital data processing, instruments, etc., can solve the problems that the performance of the devices cannot be improved as expected, and the startup success rate is not high enough, so as to shorten the waiting time and ensure the consistency of the cache Sexuality, the effect of increasing the busy rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

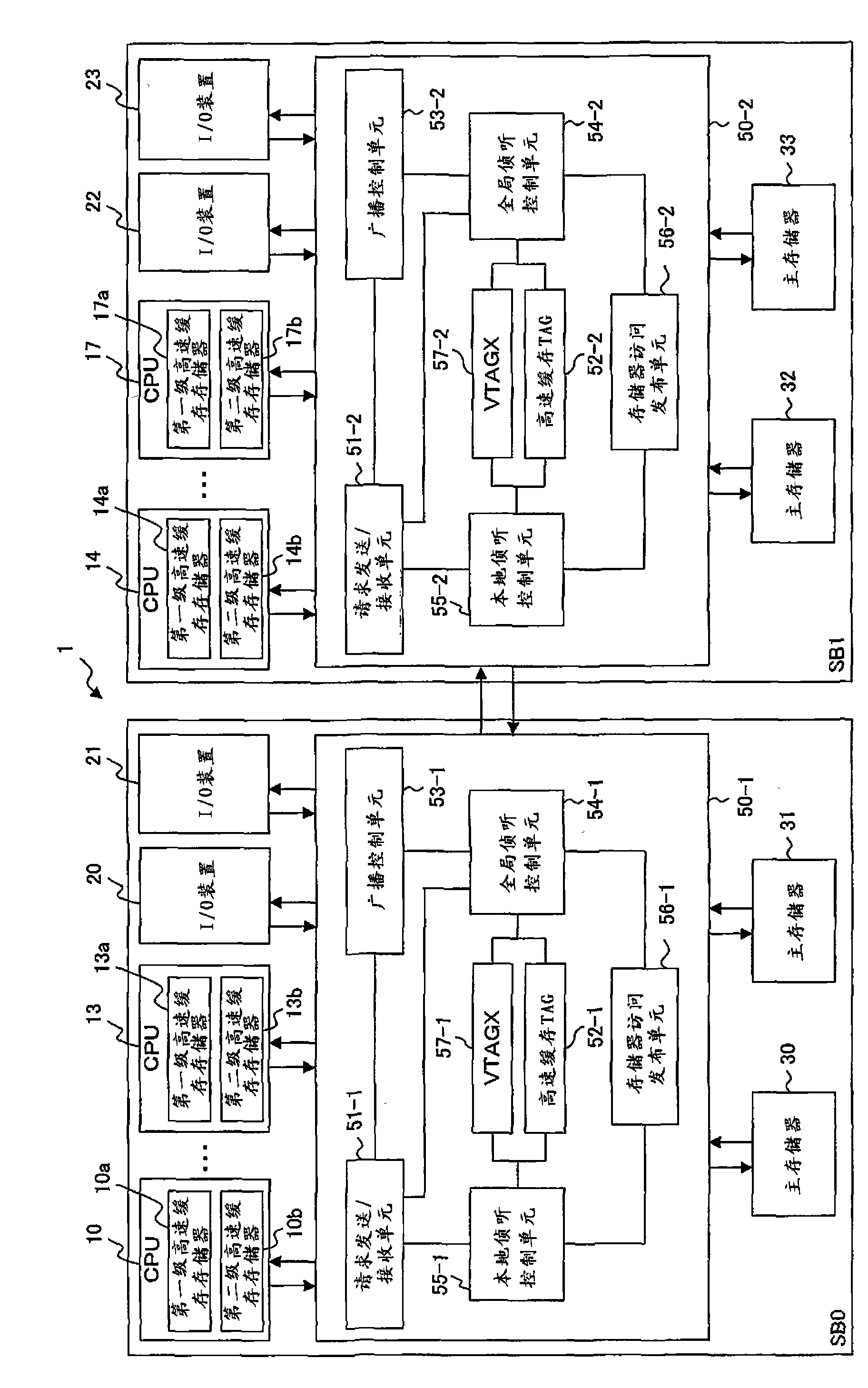

[0072] Embodiments of the present invention will be described below with reference to the drawings.

[0073] An embodiment of the invention

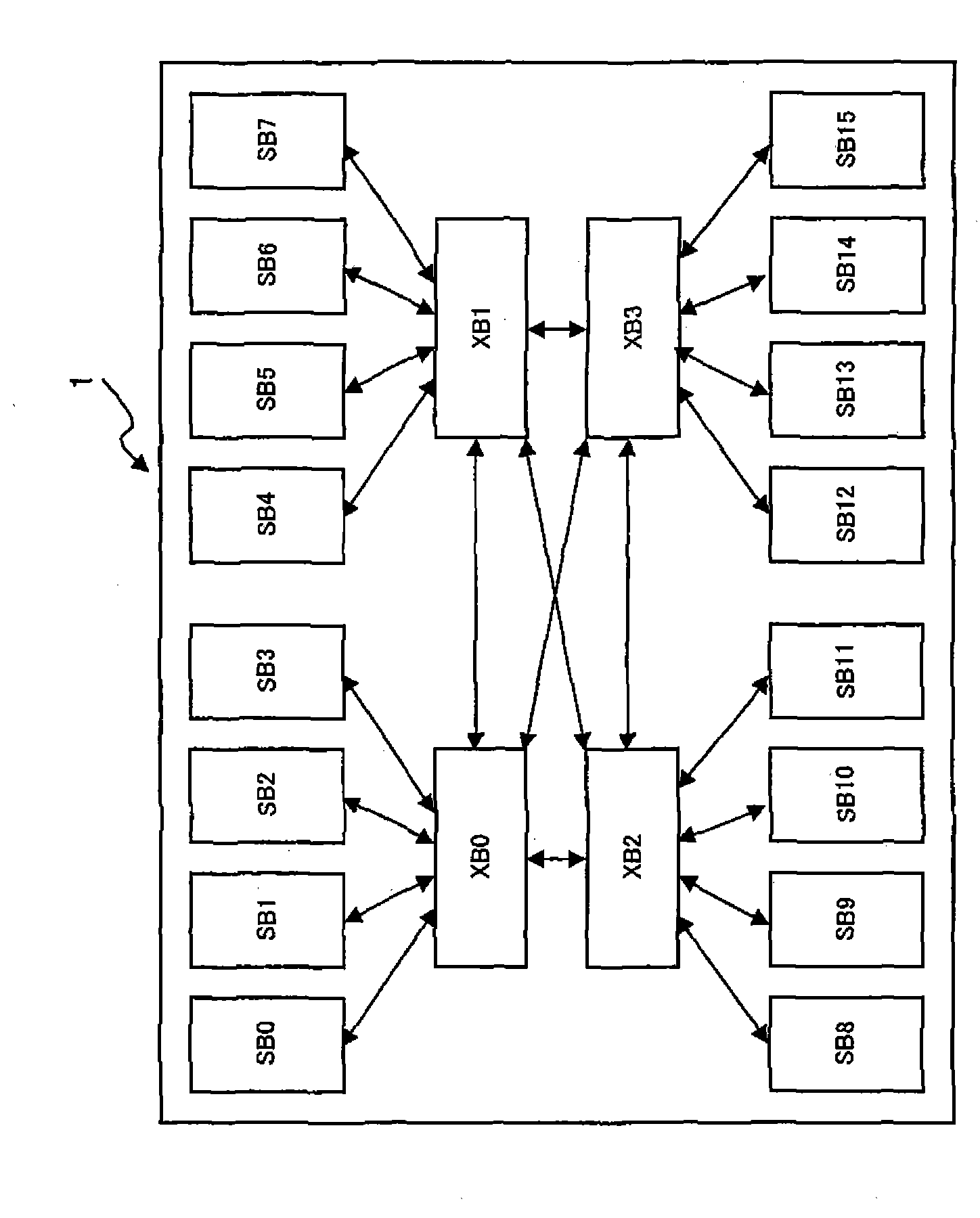

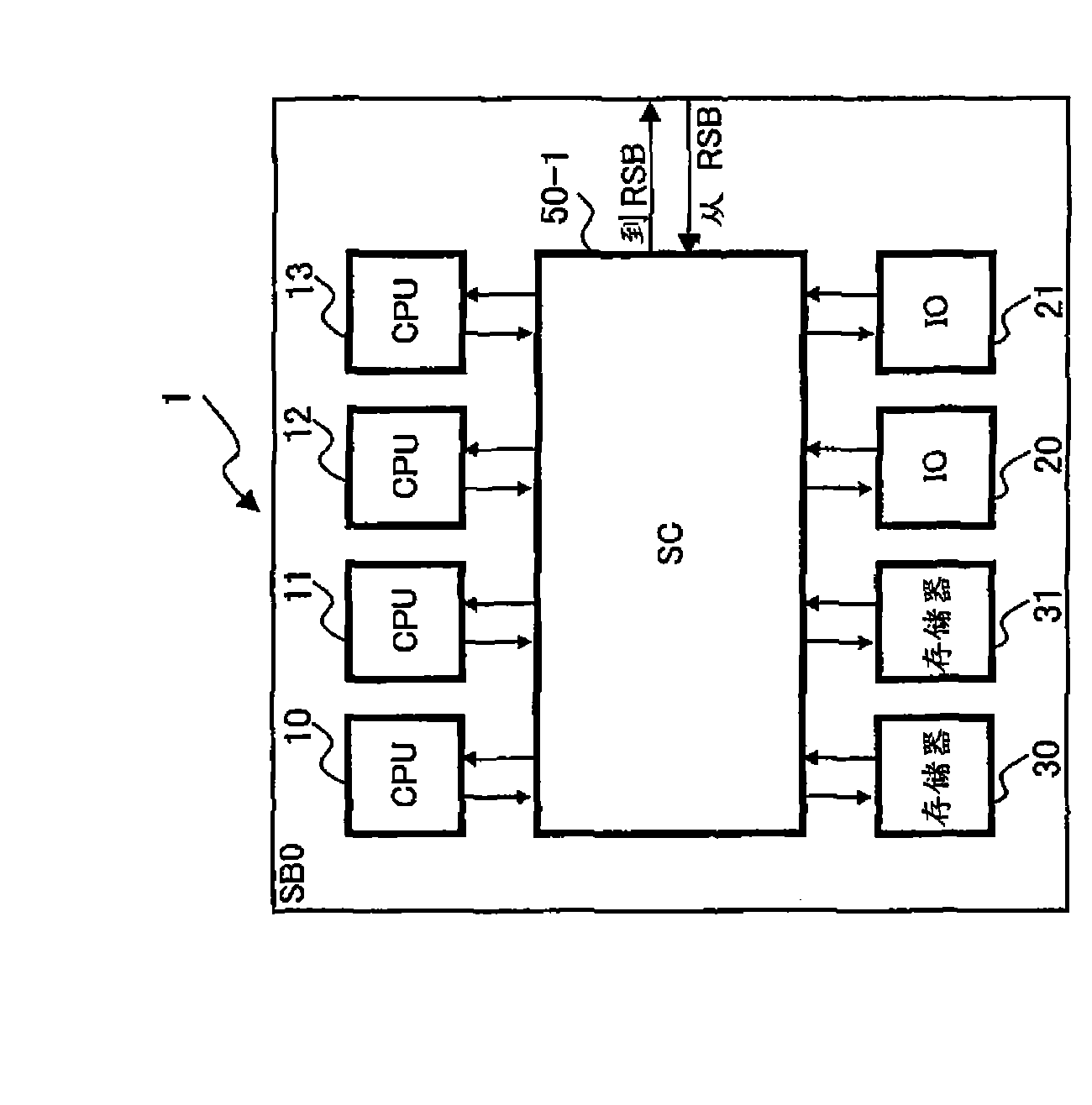

[0074] figure 1 is a block diagram showing the entire configuration of an information processing device as an embodiment of the present invention.

[0075] An information processing device 1 as an embodiment of the present invention is a large-scale SMP information processing device. Such as figure 1 As shown in , the information processing device 1 includes crossbar switches (crossbar switches) XB0 to XB3 ( figure 1 There are four crossbar switches in the example shown in ) and system boards (nodes or memory controllers) SB0 to SB15 (in figure 1 The example shown has 16 system boards). Crossbar switches XB0 to XB3 are connected to system boards SB0 to SB15 so that connections in the entire system are controlled.

[0076] The system boards SB0 to SB15 are separated from each other by partitions (nodes) formed by physical boun...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More