Semiconductor integrated circuit

A technology of integrated circuits and semiconductors, which is applied in the direction of semiconductor devices, circuits, semiconductor/solid-state device components, etc., and can solve problems such as reduced integration and increased chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

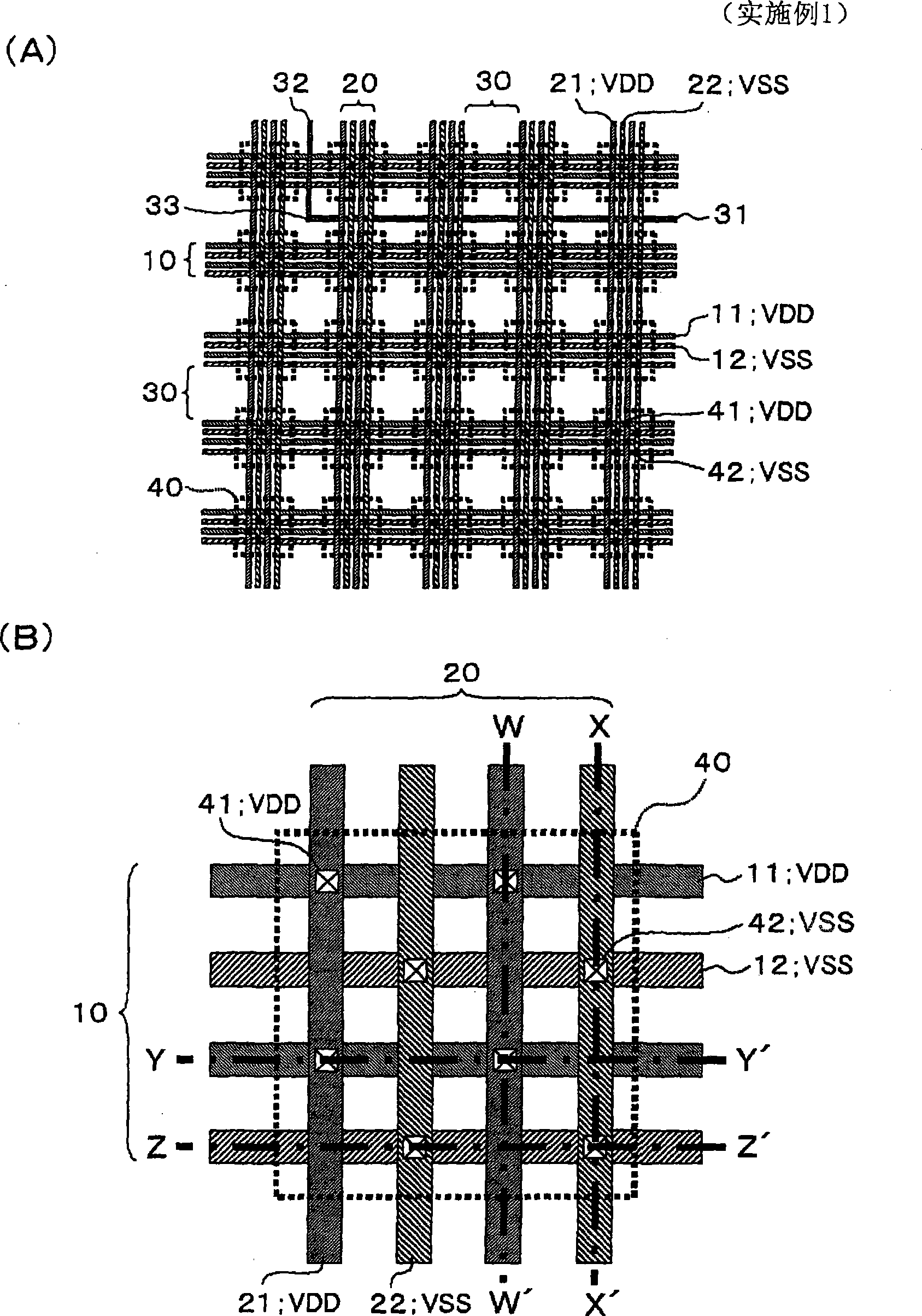

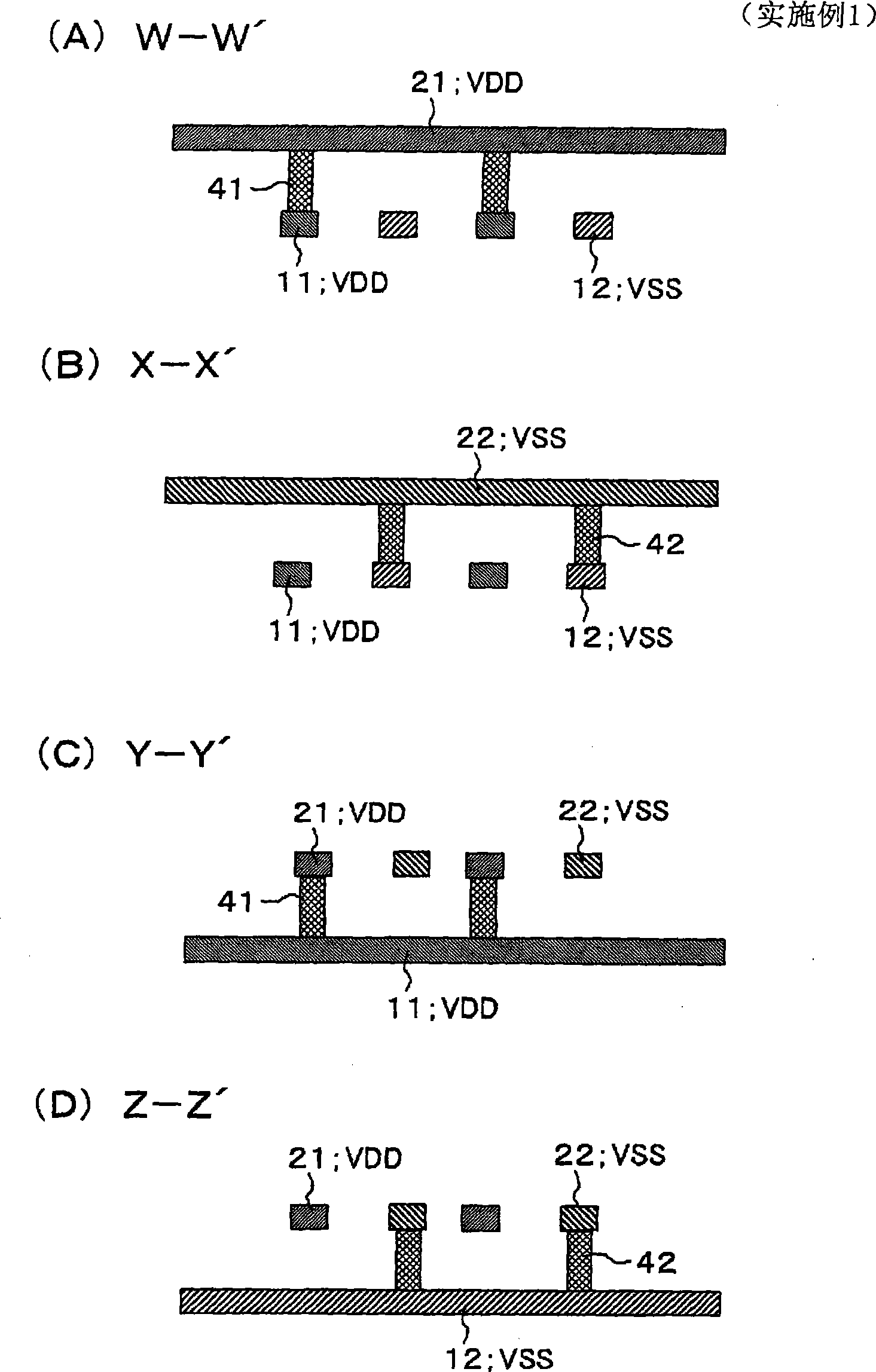

[0015] A semiconductor integrated circuit according to Embodiment 1 of the present invention will be described using the drawings. figure 1 It is (A) a partial plan view schematically showing the wiring structure of the semiconductor integrated circuit according to Embodiment 1 of the present invention and (B) an enlarged plan view of a three-dimensional intersection region. figure 2 It is a cross-sectional view between (A) W-W', (B) a cross-sectional view between XX', and a cross-sectional view between (C) Y-Y', schematically showing the wiring structure of the semiconductor integrated circuit according to Embodiment 1 of the present invention. , (D) Sectional view between Z-Z'. in addition, figure 1 and figure 2 Insulation layer is omitted.

[0016] refer to figure 1 , in a semiconductor integrated circuit, there are multilayer wiring layers on the elements formed on the semiconductor substrate, in which insulating layers and wiring layers are alternately stacked, a...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap