Chip data compressing and testing multiplex circuit and chip test circuit

A data compression and multiplexing technology, applied in the direction of electronic circuit testing, etc., can solve the problems of increased chip testing costs and production costs, and achieve the effects of improving test efficiency, increasing output, and reducing production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The chip data compression test multiplexing circuit (chip test circuit) of the present invention will be described in detail below with reference to the accompanying drawings, and the same components will be marked with the same symbols.

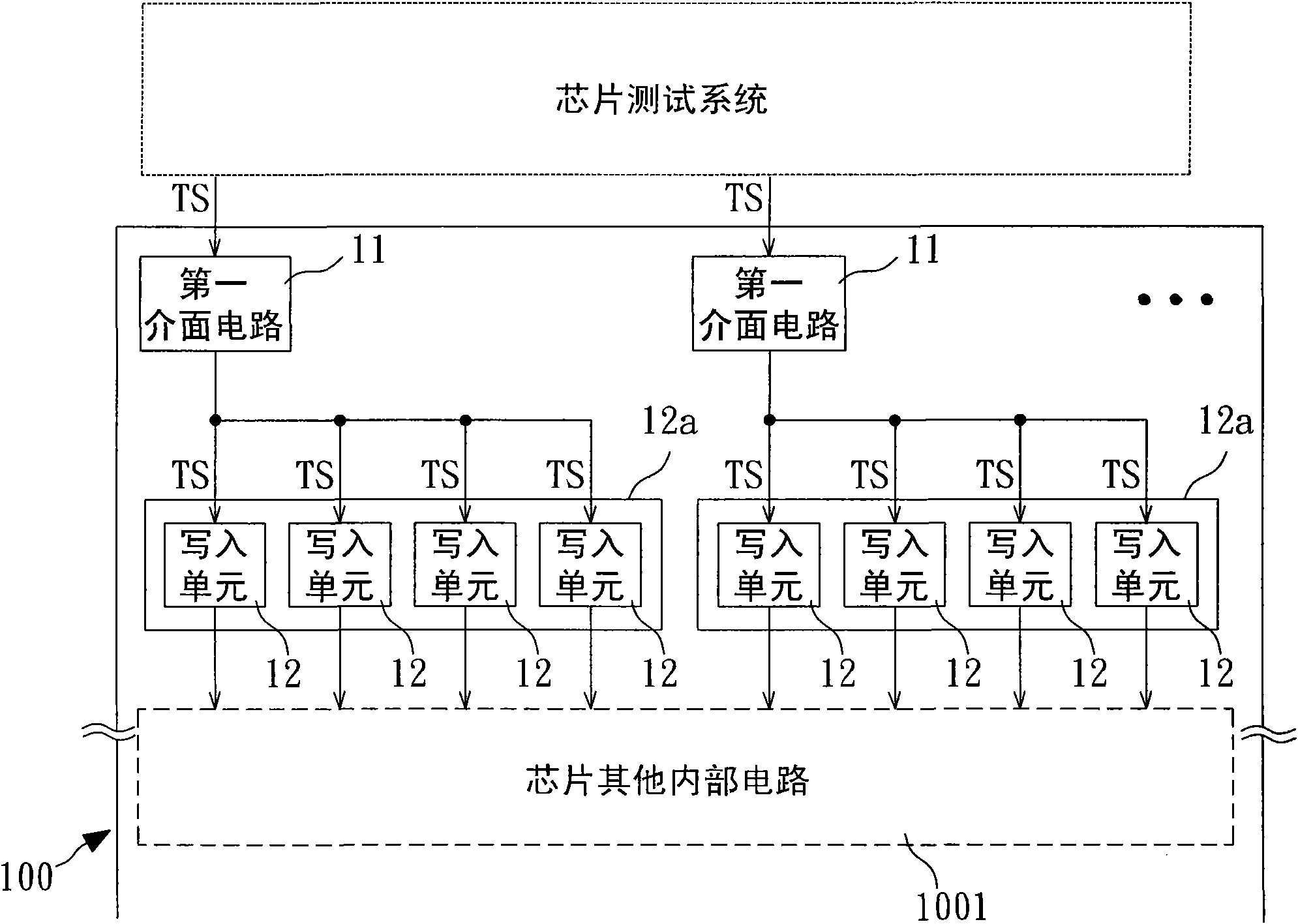

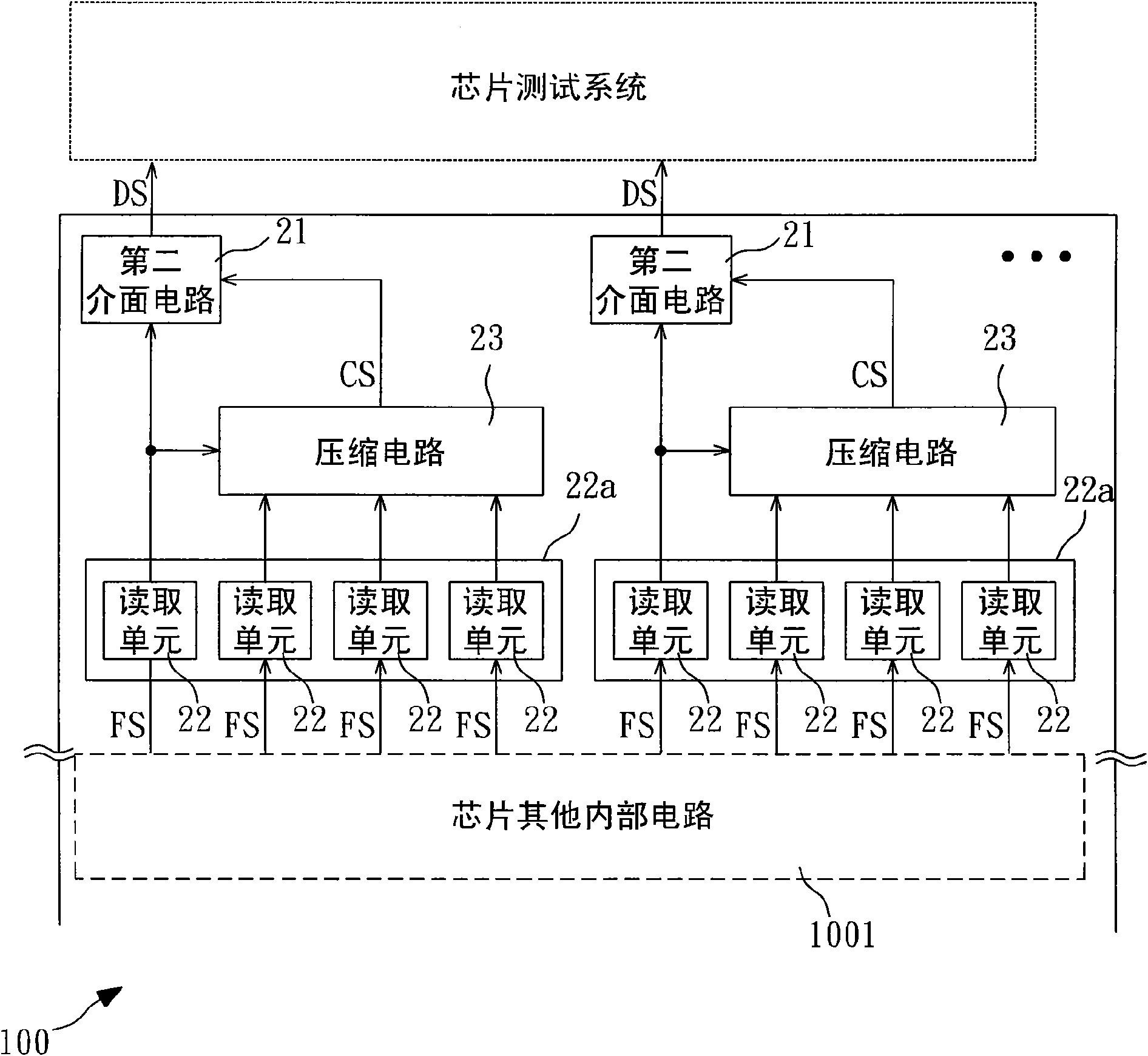

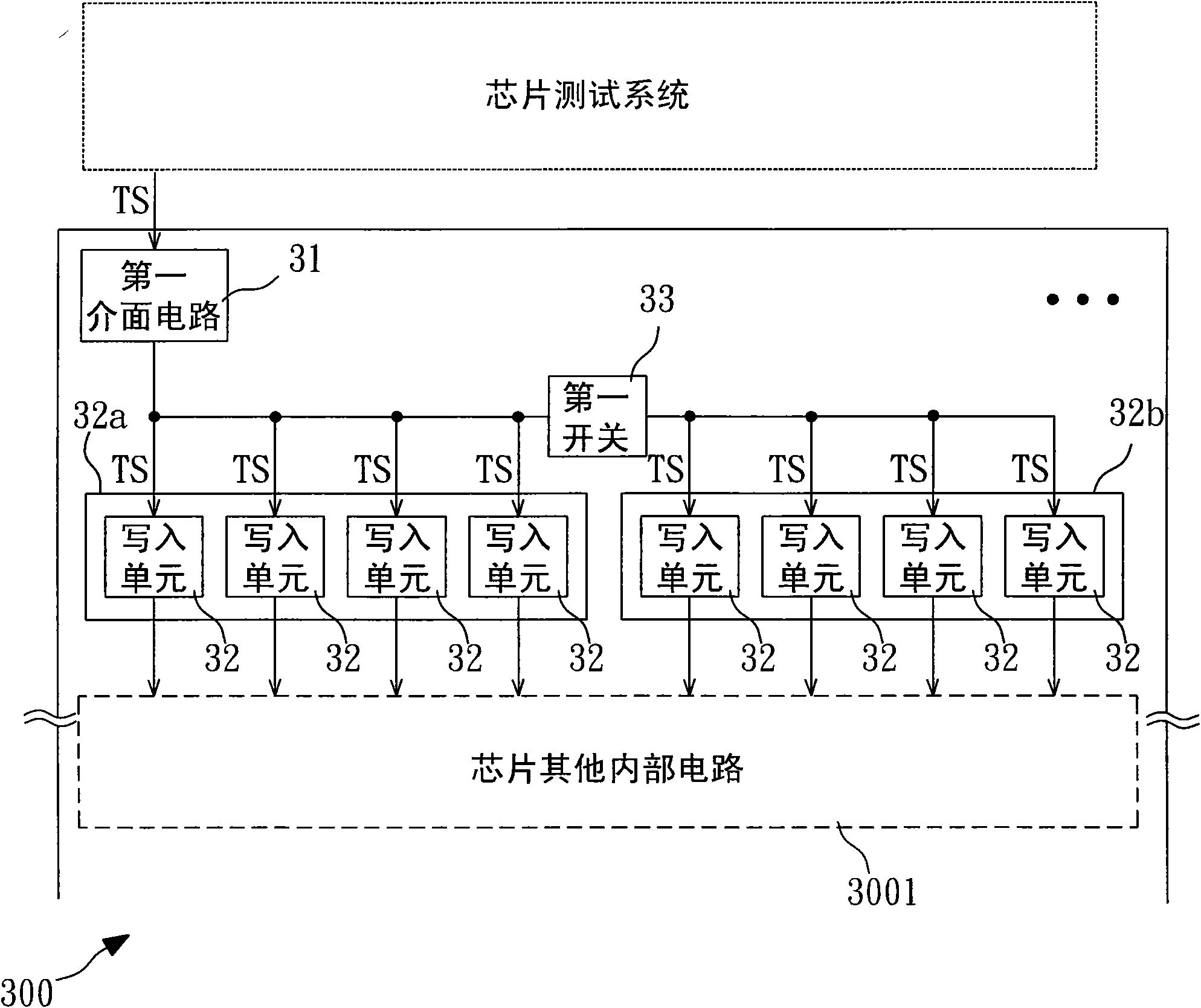

[0034] Figure 2A , Figure 2B A schematic diagram showing a chip data compression test multiplexing circuit (chip test circuit) according to an embodiment of the present invention. The chip data compression test multiplexing circuit 300 of an embodiment of the present invention includes input test signal TS to other internal circuits 3001 of the chip (Write) circuit part (such as Figure 2A shown), and obtain the feedback signal FS read (Read) circuit part from other internal circuits 3001 of the chip (such as Figure 2B shown).

[0035] Such as Figure 2A As shown, the writing circuit of the chip data compression testing multiplexing circuit 300 according to an embodiment of the present invention includes a plurality of writing un...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More