Method for manufacturing aluminum wiring

A manufacturing method and aluminum wiring technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems that affect the quality of semiconductor devices, and achieve the effect of avoiding quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

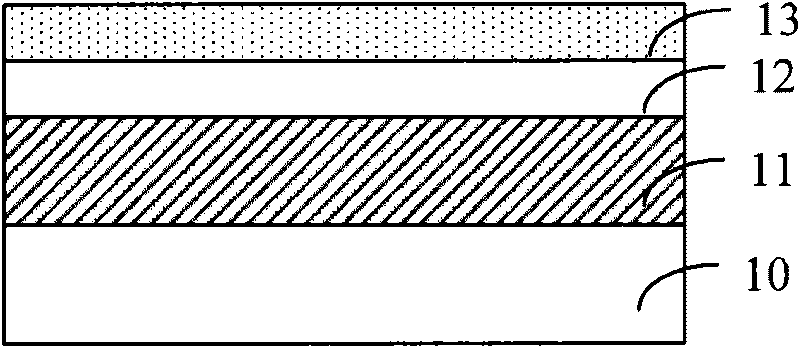

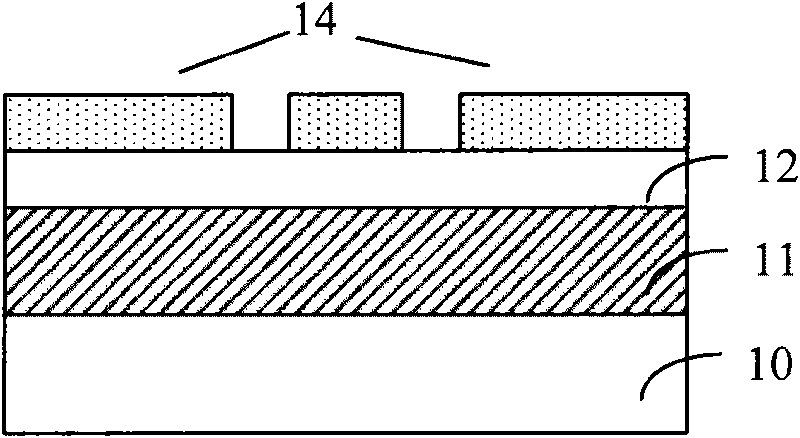

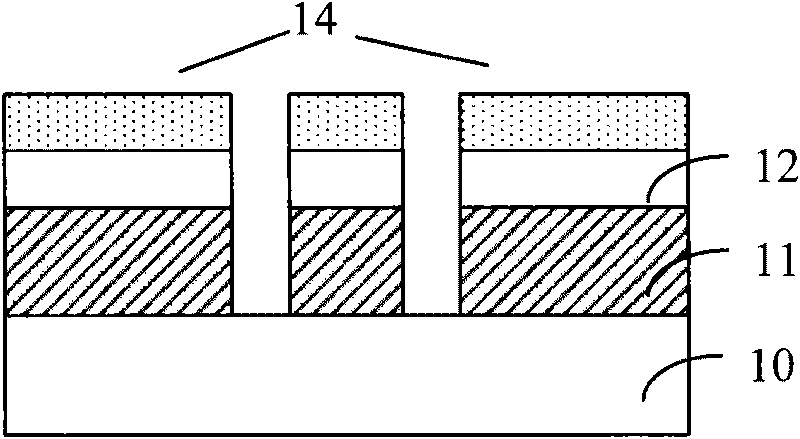

[0022] In view of this, an embodiment of the aluminum wiring manufacturing method of the present invention includes:

[0023] performing a first etching process on the aluminum wiring, the first etching process is a reactive ion etching process, and no bias voltage is applied;

[0024] After the first etching process, a second etching process is performed on the aluminum wiring to form an aluminum wiring pattern, and the second etching process is a reactive ion etching process for applying a bias voltage.

[0025] Reactive ion etching without bias voltage can make the etching process more uniform, and the etching rate is lower, that is to say, the etching rate of the center of the wafer and the edge of the wafer will tend to be the same. The etch rate of wide aluminum wiring and narrow aluminum wiring will also tend to be the same. (A detailed description of this process will be revealed in subsequent examples)

[0026] Thus, the aluminum wiring layer can be uniformly thinne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More