Error correcting controller, flash memory chip system thereof and error correcting method

A technology of error correction and flash memory chip, which is applied in the direction of instruments, static memory, etc., and can solve the problems of unable to support flash memory and error correction ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

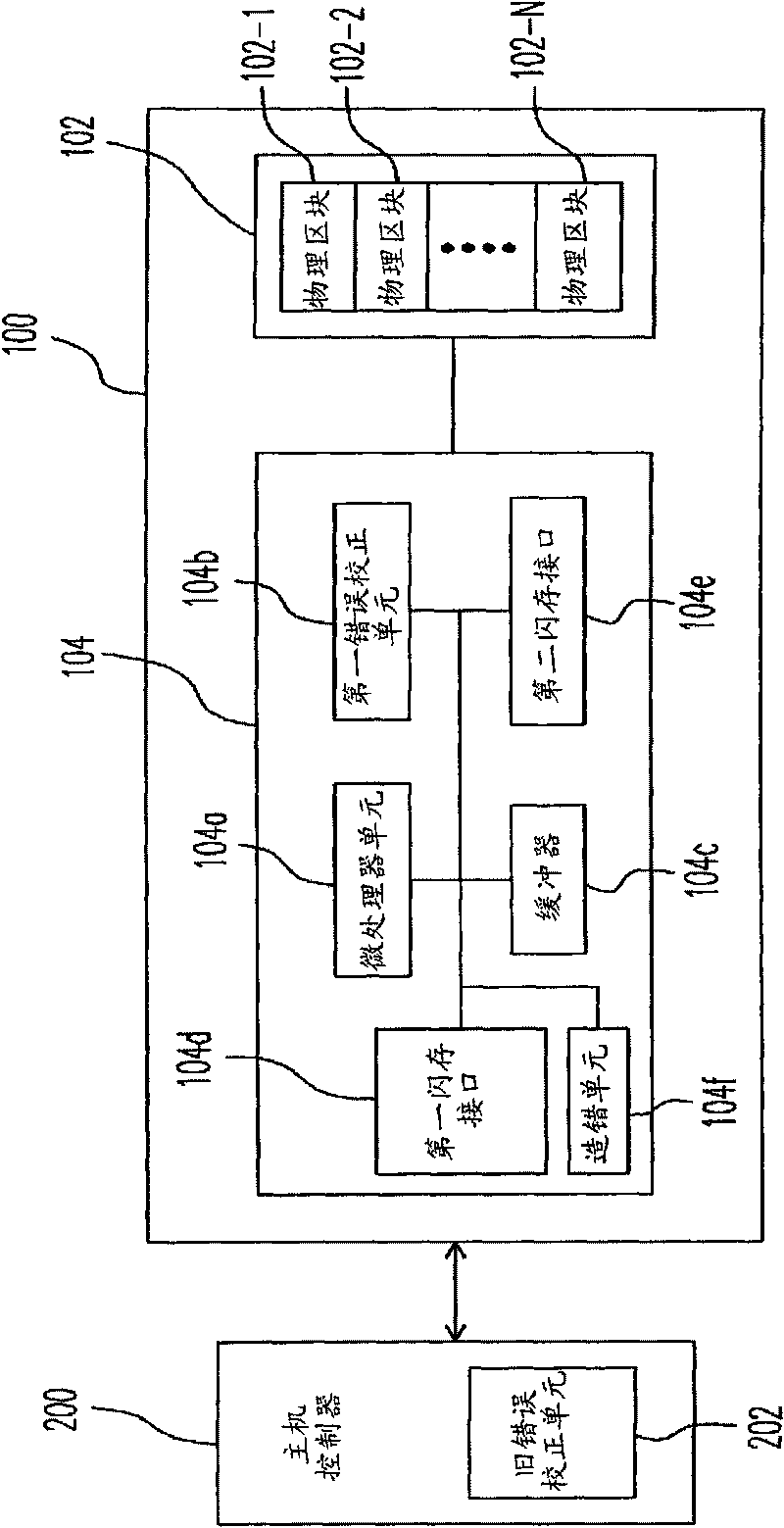

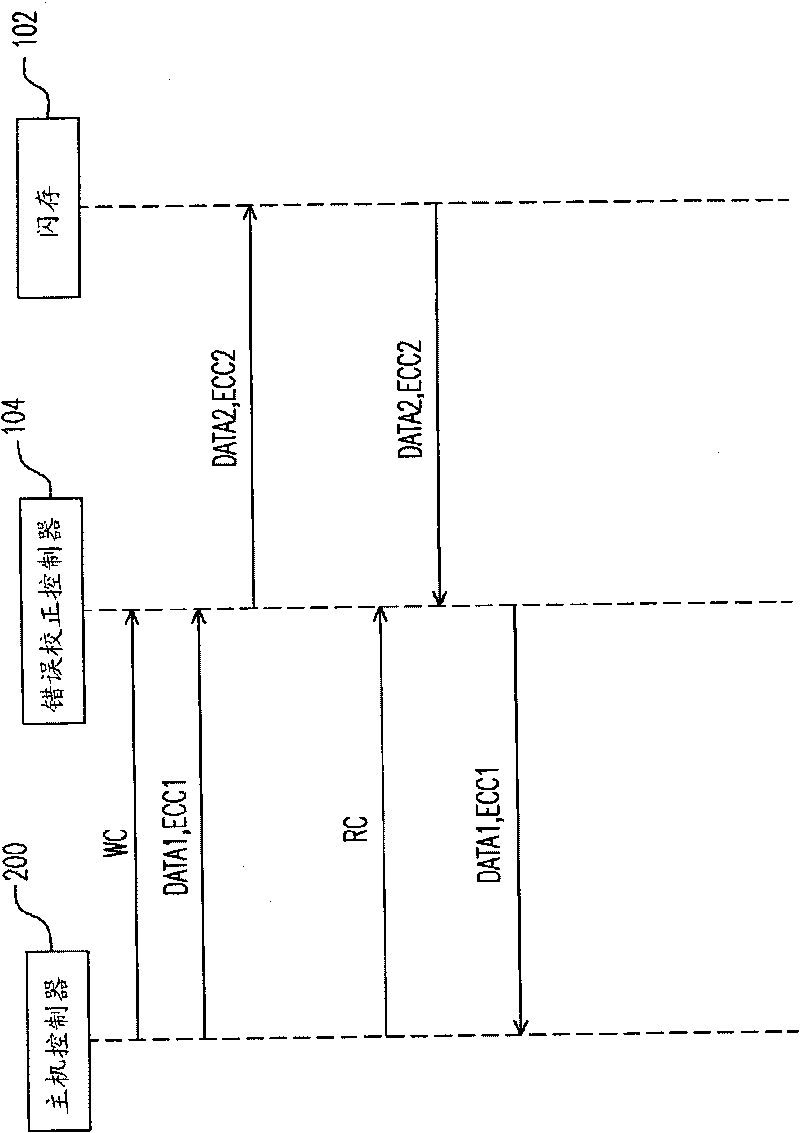

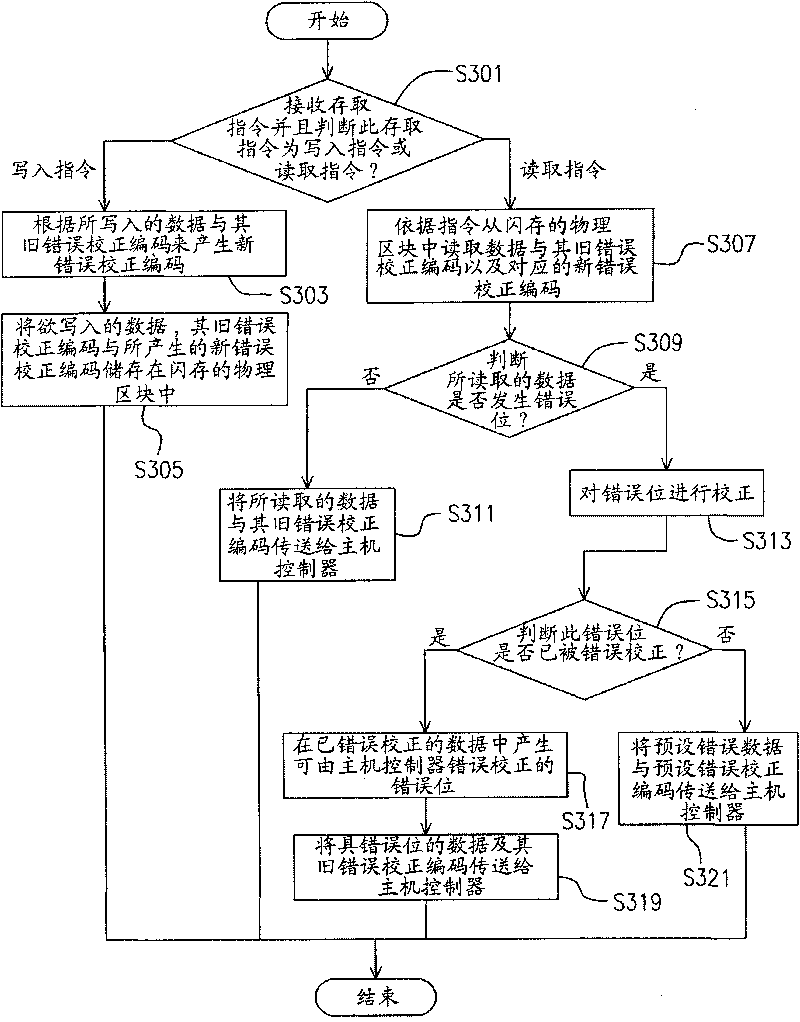

[0061] figure 1 is a schematic block diagram illustrating a flash memory chip system according to the first embodiment of the present invention.

[0062] Please refer to figure 1 , the flash chip system 100 includes a flash memory 102 and an error correction controller 104 . The flash memory chip system 100 is connected with the host controller 200, and the host controller 200 performs various access operations on it. In particular, the host controller 200 has an old error correction unit 202, wherein the old error correction unit 202 can provide the ability to correct 1 error bit and detect 2 error bits for data. It is worth mentioning that in this embodiment, the flash memory 102 and the error correction controller 104 are packaged as a single system chip, but in another embodiment of the present invention, the flash memory 102 and the error correction controller 104 can be independent chips.

[0063] The flash memory 102 is a storage medium for storing data. The flash m...

no. 2 example

[0095] Figure 4 is a schematic block diagram illustrating a flash memory chip system according to a second embodiment of the present invention.

[0096] Please refer to Figure 4 , the flash chip system 400 includes a flash memory 402 and an error correction controller 404 . The flash chip system 400 is connected to the host controller 200 so that the host controller 200 can perform various access operations thereon. As mentioned above, the host controller 200 has the old error correction unit 202, wherein the old error correction unit 202 can provide the capability of error correction of 1 error bit and detection of 2 error bits for data.

[0097] The flash memory 402 is the same as the flash memory 102 in the first embodiment, and will not be repeated here.

[0098]The error correction controller 404 is electrically connected to the flash memory 402 and used for executing error correction codes and error correction programs that meet the error correction capability requi...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap