Semiconductor technology and the silicon substrate and chip packaging structure formed by applying this technology

A semiconductor and process technology, which is applied in the field of silicon substrate and chip packaging structure, can solve problems such as inability to achieve thinning, and achieve the effect of thin package thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

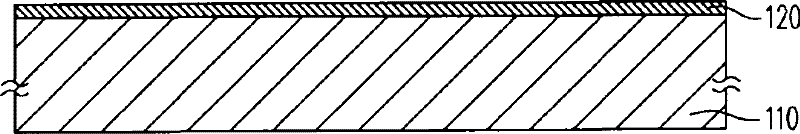

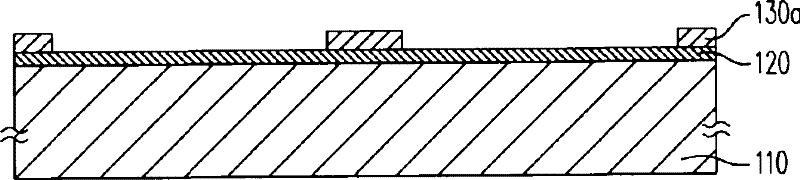

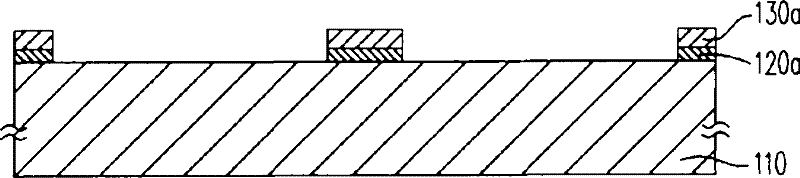

[0038] Please refer to Figure 1B , and then, forming a first patterned photoresist mask 130 a on the first insulating layer 120 . Next, at least one stepped structure 140 is formed on the silicon substrate 110 (please refer to Figure 1L ). In detail, the steps of forming the stepped structure 140 are as follows, please refer to Figure 1C and Figure 1D , first, using the first patterned photoresist mask 130a as an etching mask, etch the first insulating layer 120 exposed outside the first patterned photoresist mask 130a to form a patterned The first insulating layer 120a. Next, the first patterned photoresist mask 130a is removed to expose the patterned first insulating layer 120a under the first patterned photoresist mask 130a. Please refer to Figure 1E , and then, using the patterned first insulating layer 120a as an etching mask, etching the silicon substrate 110 exposed outside the patterned first insulating layer 120a to form at least one layer having a first de...

PUM

| Property | Measurement | Unit |

|---|---|---|

| height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More