Time-to-digital convertoer and all-digital phase locked loop

A technology of time-to-digital converters, applied in the field of digital-to-time converters, which can solve problems such as poor phase calibration accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Certain exemplary embodiments of the present invention will be described in more detail with reference to the accompanying drawings.

[0032] In the following description, the same reference numerals denote the same elements even in different drawings. Features such as detailed construction and elements defined in the description are provided to facilitate a more comprehensive understanding of the invention. However, the present invention may be practiced without using these specifically defined features. Also, well-known functional constructions are not described in detail since they would obscure the invention with unnecessary detailed description.

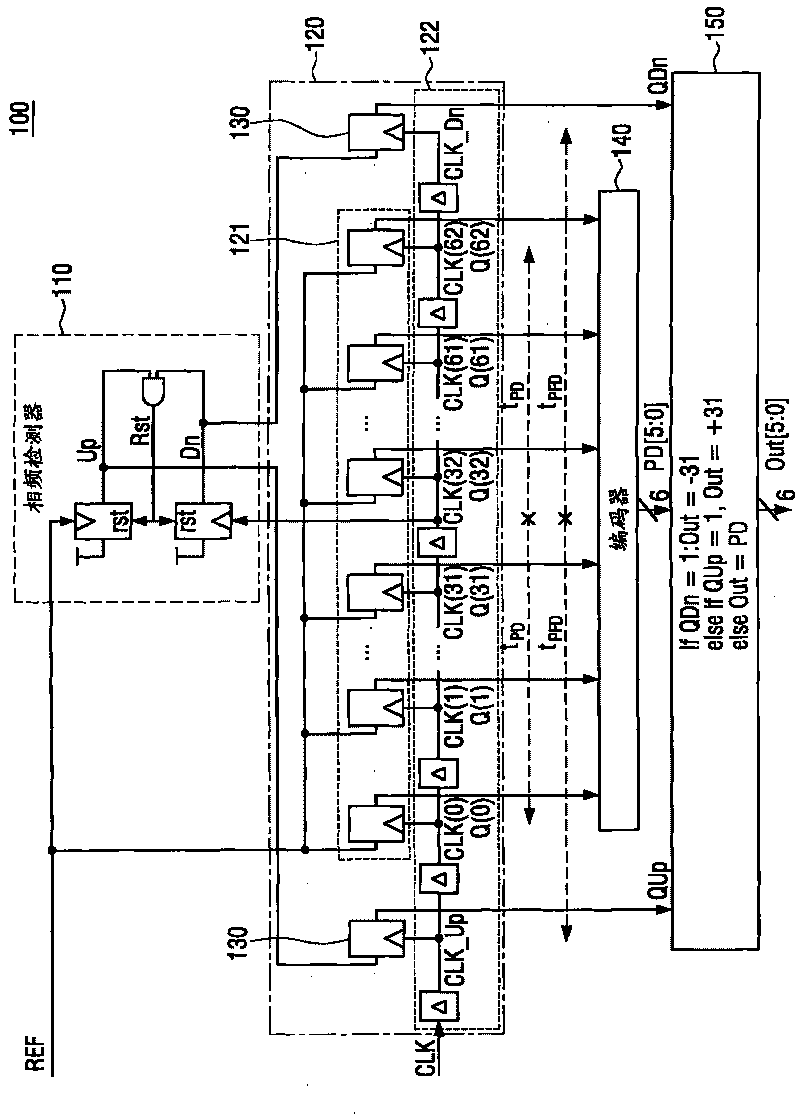

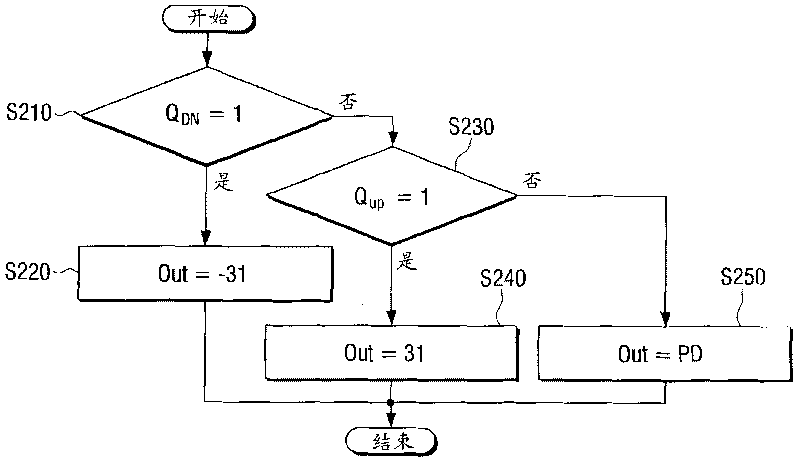

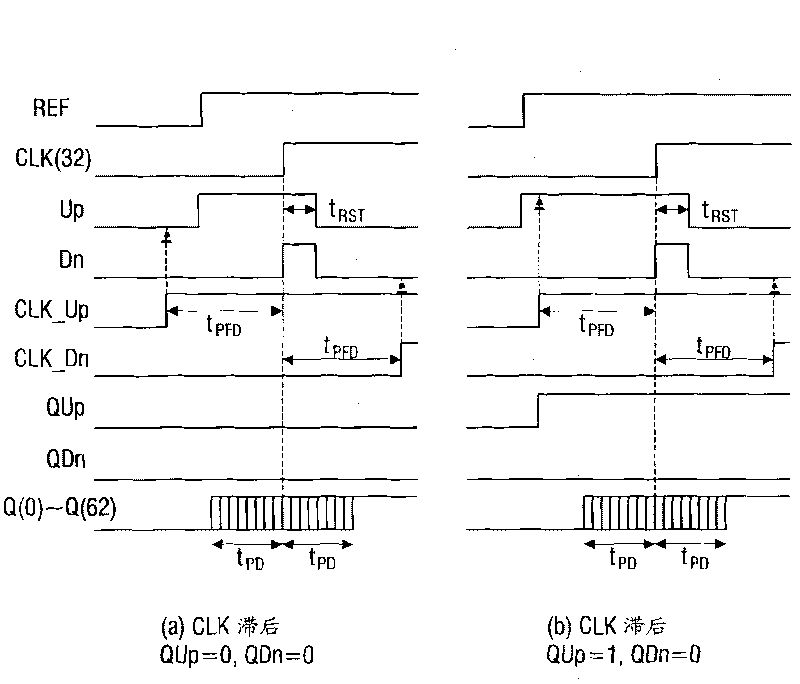

[0033] figure 1 is a circuit diagram of a time-to-digital converter (TDC) 100 according to an exemplary embodiment of the present invention. refer to figure 1 , the TDC 100 may include a phase frequency detector (PFD) 110 , a converter 120 , a frequency detector 130 and an output device 150 .

[0034] PFD 100 receive...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More