Method for chip alignment

A technology for wafers and alignment marks, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., and can solve the problems of complicated error values, error values on the wafer carrier, and increased measurement errors, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

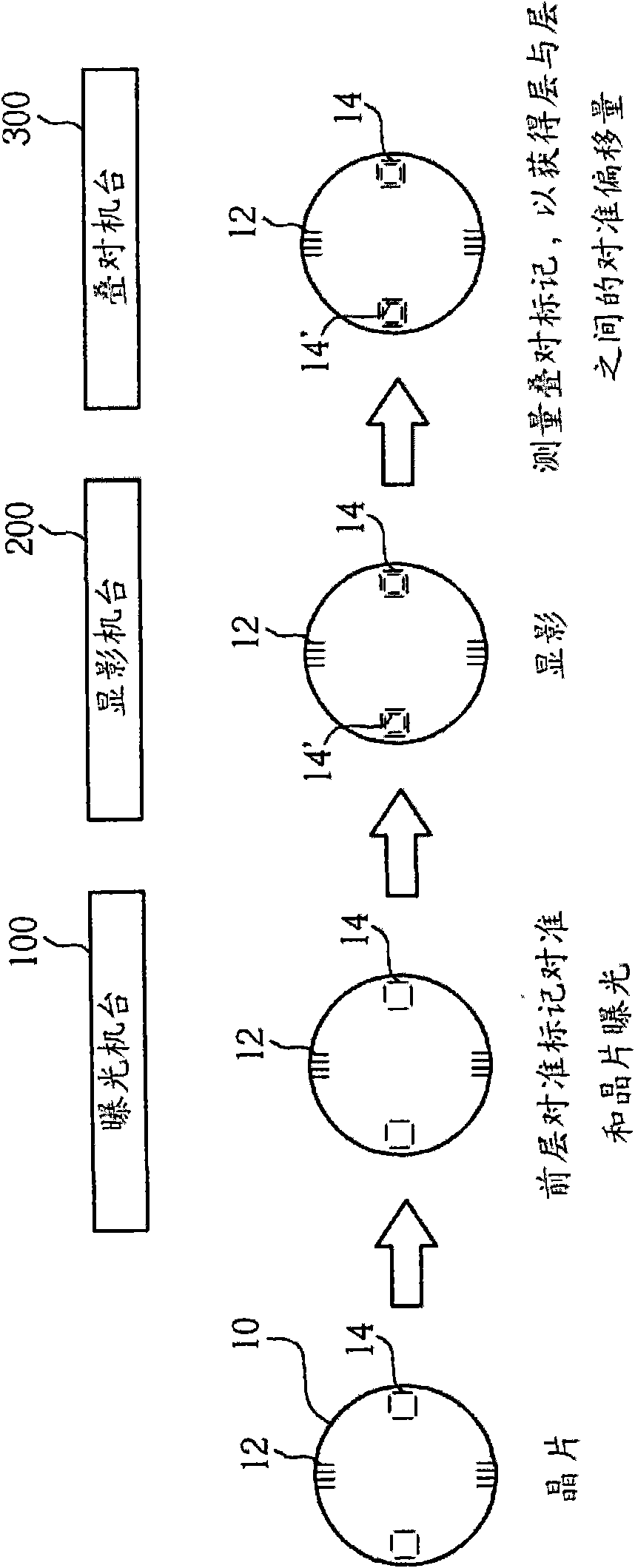

[0021] figure 1 is a schematic diagram of a known wafer alignment method.

[0022] Such as figure 1 As shown, at first a wafer 10 is provided, on which a first material layer (not shown), a second material layer (not shown) and a third material layer (not shown) are sequentially arranged from bottom to top, the first material layer layer and the second material layer may be a silicon substrate, a conductive layer or an insulating layer, and the third material layer may be photoresist. In the first material layer on the wafer 10, alignment marks 12 and overlay marks 14 are provided. The alignment mark 12 and the overlay mark 14 may be groove structures recessed in the first material layer, and are disposed at the edge of the wafer or on the dicing line. Next, the wafer 10 is sent into the exposure machine 100, and the alignment marks 12 are used to align the wafer 10 before exposure, so that the wafer 10 is placed in a suitable exposure position, and then the wafer 10 is irr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More