Static random-access memory for eliminating reading interference

A technology of static randomness and read interference, which is applied in the direction of static memory, digital memory information, information storage, etc., can solve the problems of static random memory read interference, achieve the effect of avoiding read interference and improving stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

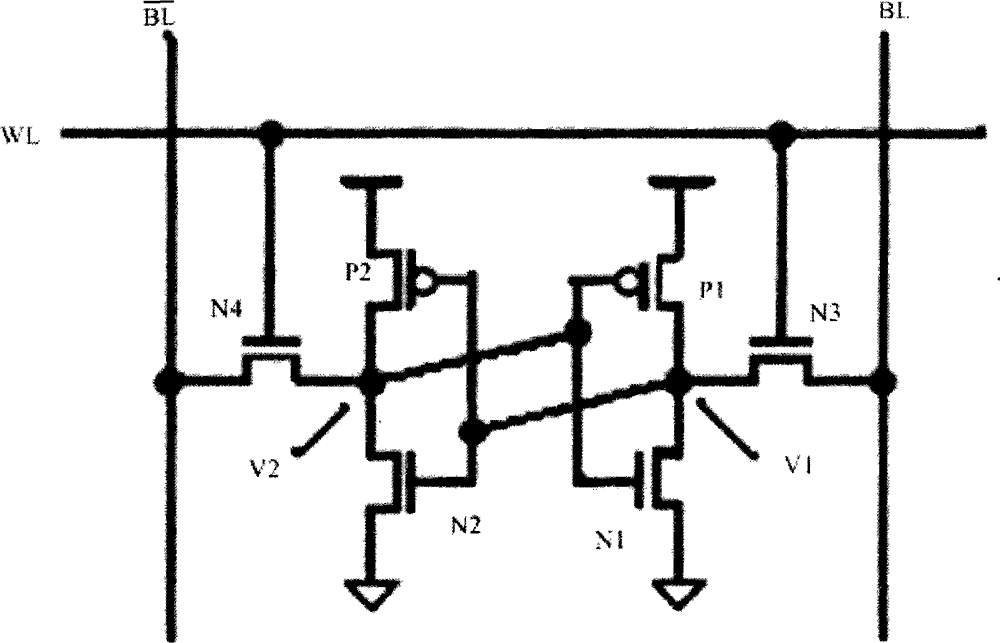

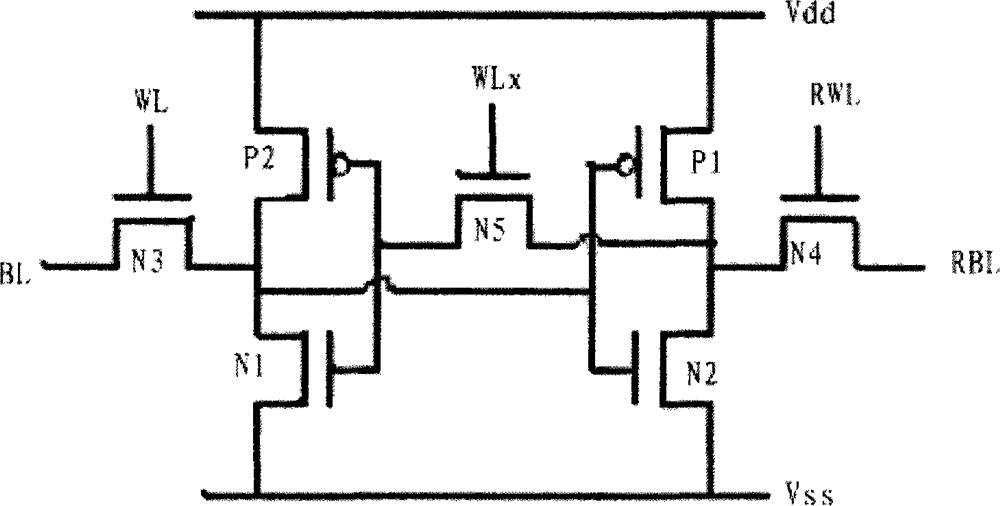

[0014] Please refer to image 3 , image 3 It is a static random access memory that eliminates read interference in the present invention. The static random access memory adds an NMOS transistor on the basis of the existing six-transistor static random access memory. The existing SRAM is composed of six transistors. The six transistors include four NMOS transistors (N1, N2, N3, N4) and two PMOS transistors (P1, P2), wherein the first PMOS transistor P1, the first NMOS transistor N1 and the second PMOS transistor P2, the first Two NMOS transistors N2 form two COMS inverters, and cross-coupling forms a bistable flip-flop; the third NMOS transistor N3 and the fourth NMOS transistor N4 of the gating transistor provide access and control for data input and output; in the figure BL, is a bit line control signal, WL is a word line of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More