Clock circuit and data decoding circuit of non-contact type IC (Integrated Circuit) card

A non-contact, decoding circuit technology, applied in the field of non-contact IC cards, can solve the problems of easy loss of decoding ability, limited pause cycle width, complex circuit, etc., and achieve strong anti-interference ability, high correct decoding rate, and accurate decoding The effect of the result

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

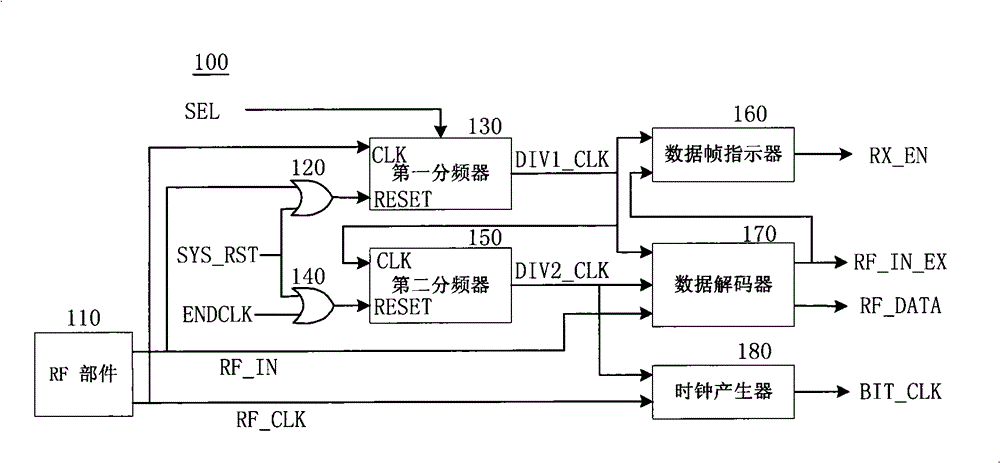

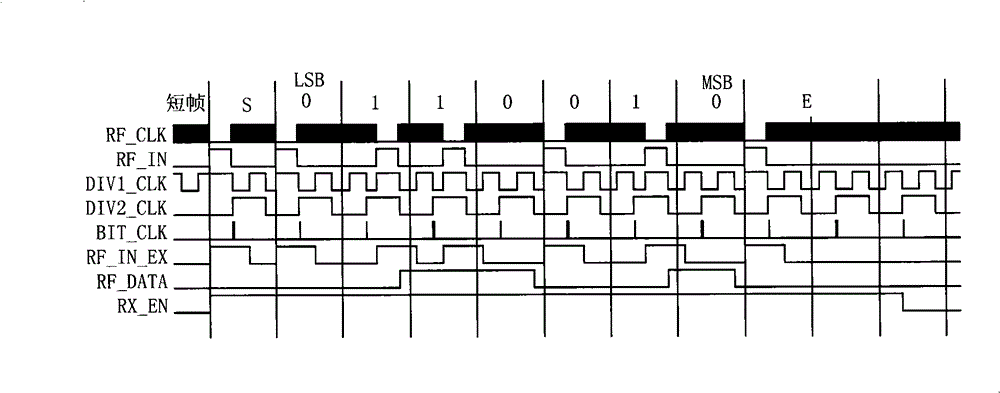

[0027] see figure 1 and combine figure 2 As shown, the clock circuit and data decoding circuit 100 of the present invention are contained in a non-contact IC card, and include an RF component 110 (receiver), an OR gate 120, a second OR gate 140, and a first frequency divider 130 , a second frequency divider 150 , a clock generator 180 , a data decoder 170 , and a data frame indicator 160 .

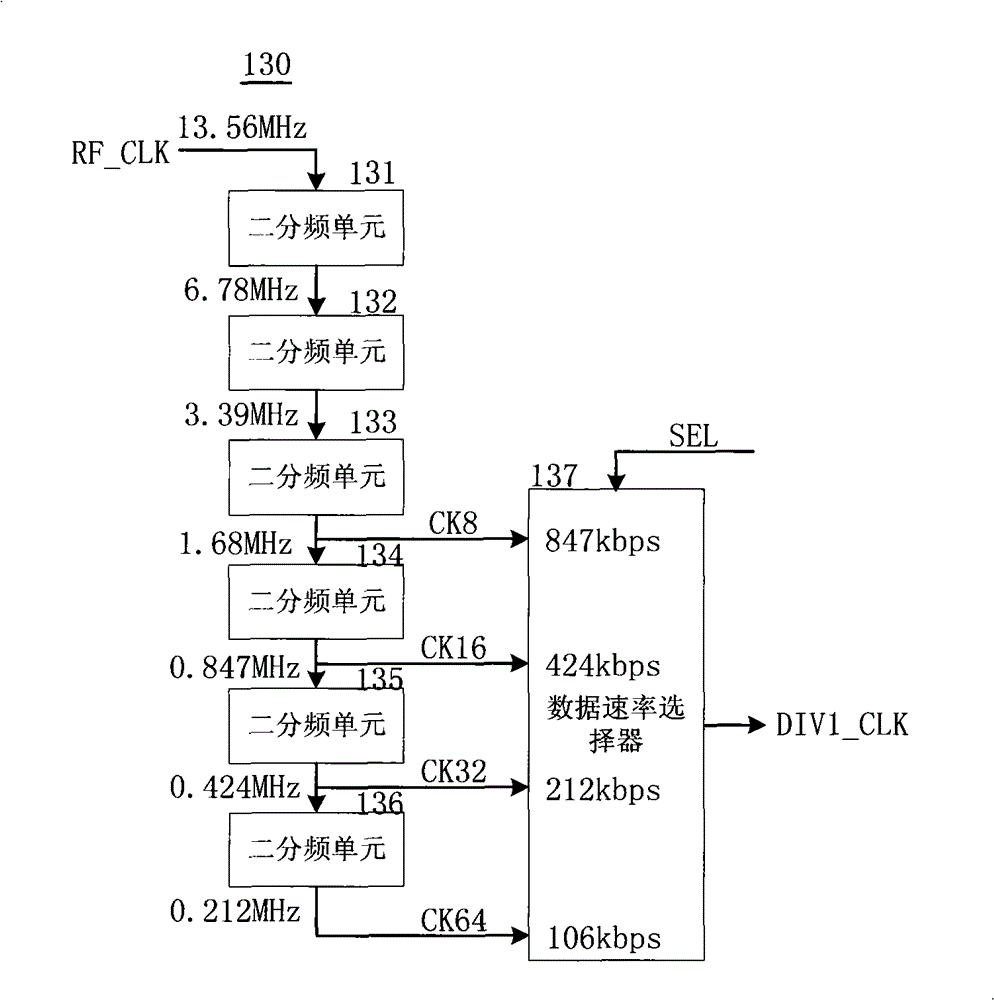

[0028] The RF part 110 is used to receive, for example, 13.56MHz and a bit rate of 106kbps RF signal with a pause period according to the ISO / IEC14443A type protocol (in the specific embodiment of the present invention, the RF signal of the 106kbps bit rate is taken as an example, for 212kbps, The main difference between the 424kpbs and 847kbps bit rate RF signals is that the first frequency divider is provided with a selection port SEL, which can select the frequency division clock signal DIV1_CLK of different frequency division frequencies, and is used to select the bit rate of the non...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More