Chip structure, wafer structure and chip fabrication technique

A technology of chip structure and manufacturing process, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as chip fragmentation, and achieve the effect of improving cutting yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

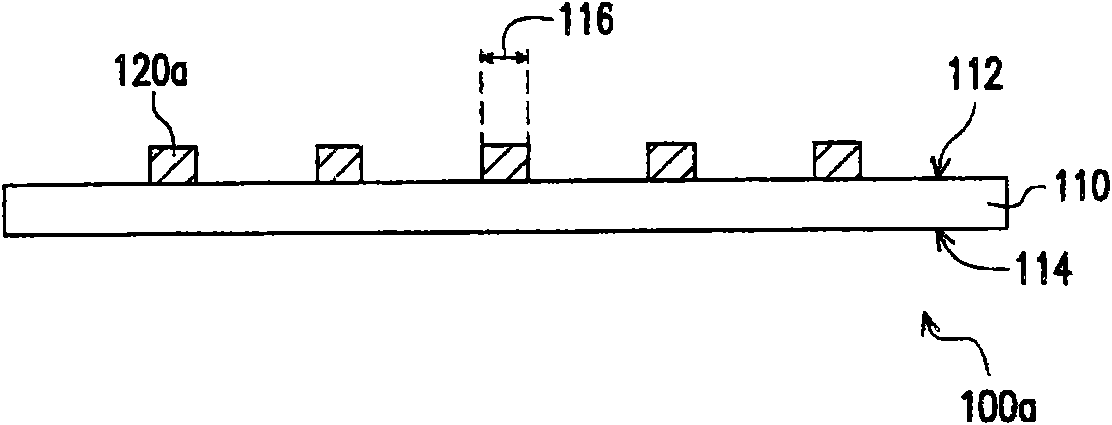

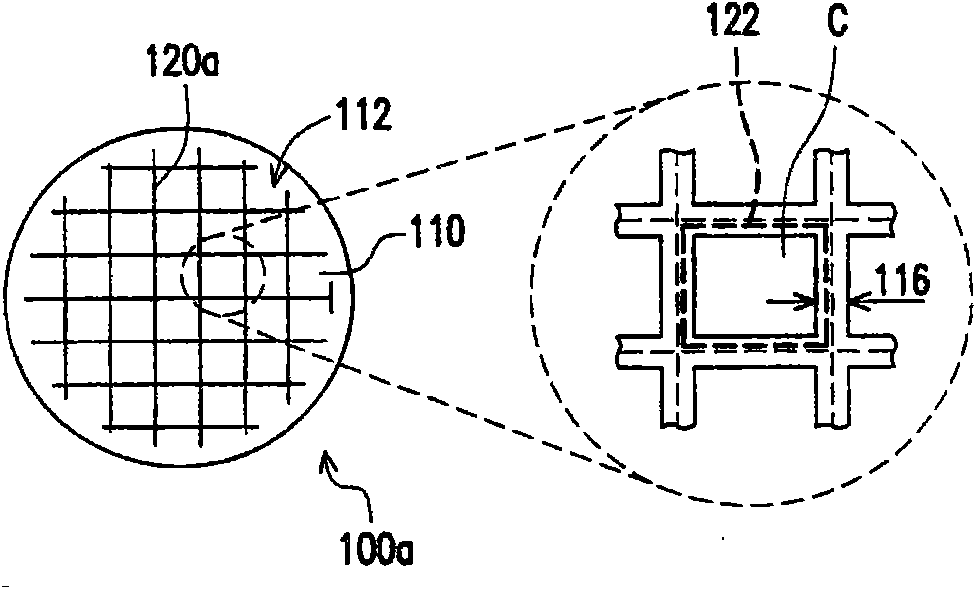

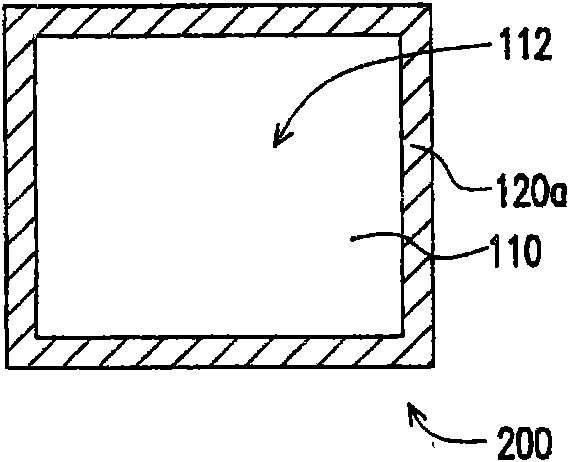

[0021] Figure 1A is a schematic cross-sectional view of a wafer structure according to an embodiment of the present invention, Figure 1B for Figure 1A The top view schematic diagram and partial enlarged schematic diagram of the wafer structure, Figure 1C for cutting Figure 1A A schematic top view of a chip structure formed by the wafer structure. Please also refer to Figure 1A and Figure 1B , in this embodiment, the wafer structure 100a includes a substrate 110 and a stress buffer layer 120a.

[0022] Specifically, the substrate 110 has a first surface 112, a second surface 114 opposite to the first surface 112, and a plurality of dicing lines 116 separating the substrate 110 into a plurality of chip regions C, wherein the dicing lines 116 are formed by a A passivation layer (not shown) is defined by a region not covering the first surface 112 of the substrate 110 , and this region does not include a pad region (not shown) exposed by the passivation layer.

[0023] T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More